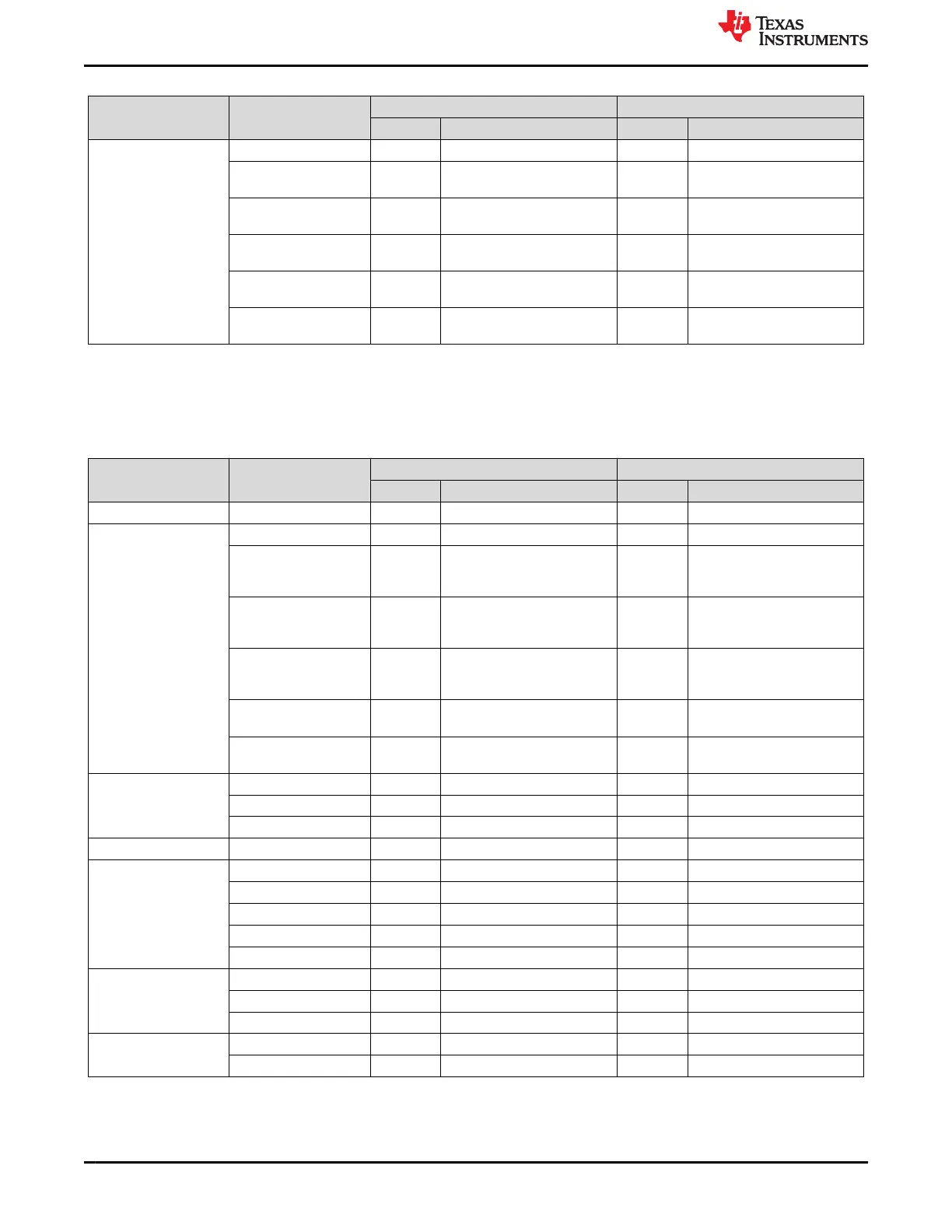

Table 5-9. POWERGOOD NVM Settings (continued)

Register Name Field Name

TPS65941213-Q1 TPS65941111-Q1

Value Description Value Description

PGOOD_SEL_4 PGOOD_SEL_VCCA 0x0 Masked 0x0 Masked

PGOOD_SEL_TDIE_W

ARN

0x0 Masked 0x0 Masked

PGOOD_SEL_NRSTO

UT

0x0 Masked 0x0 Masked

PGOOD_SEL_NRSTO

UT_ SOC

0x0 Masked 0x0 Masked

PGOOD_POL 0x0 PGOOD signal is high when

monitored inputs are valid

0x0 PGOOD signal is high when

monitored inputs are valid

PGOOD_WINDOW 0x0 Only undervoltage is

monitored

0x0 Only undervoltage is

monitored

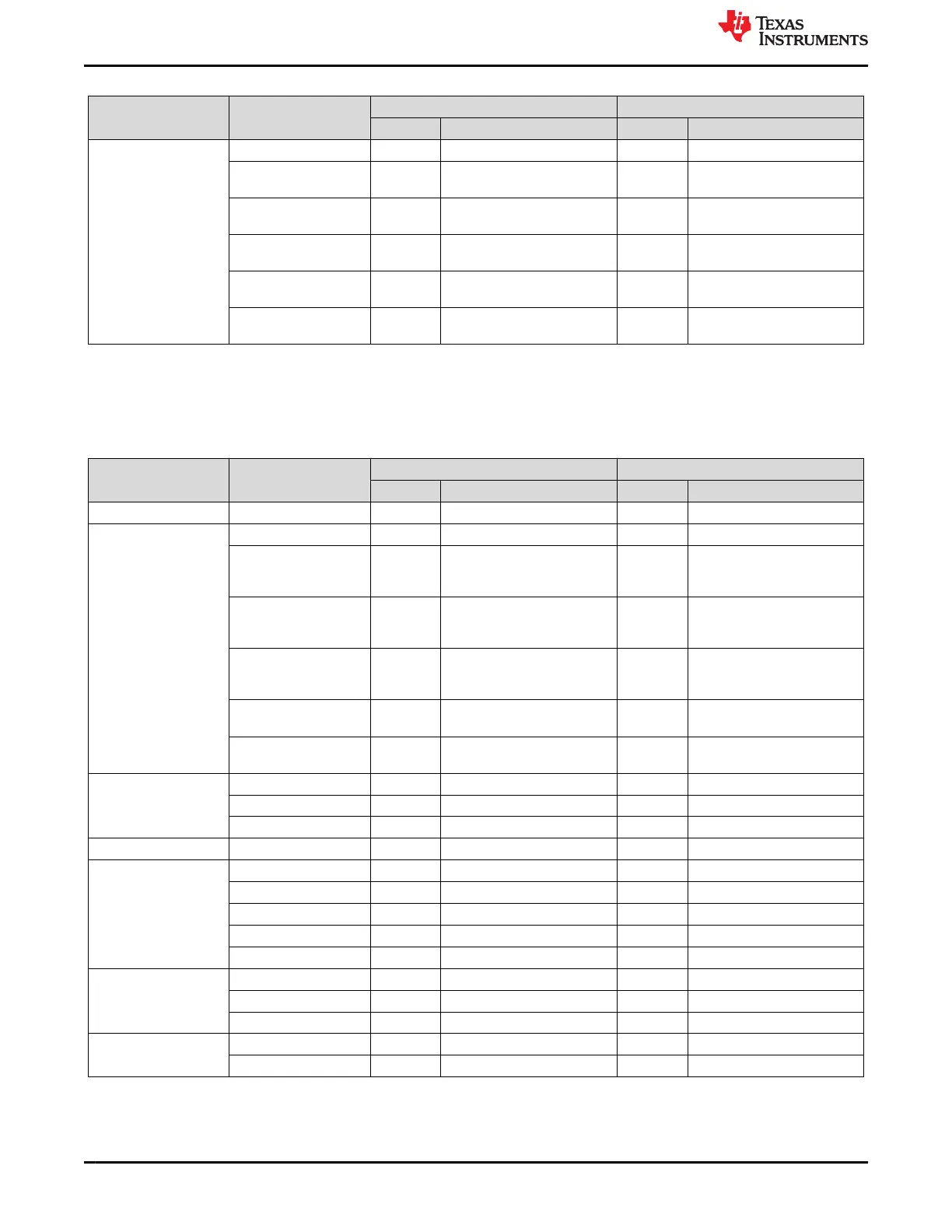

5.10 Miscellaneous Settings

These settings detail the default configurations of additional settings, such as spread spectrum, BUCK

frequency, and LDO timeout. All these settings can be changed though I

2

C after startup.

Table 5-10. Miscellaneous NVM Settings

Register Name Field Name

TPS65941213-Q1 TPS65941111-Q1

Value Description Value Description

PLL_CTRL EXT_CLK_FREQ 0x0 1.1 MHz 0x0 1.1 MHz

CONFIG_1 TWARN_LEVEL 0x0 130C 0x0 130C

I2C1_HS 0x0 Standard, fast or fast+ by

default, can be set to Hs-mode

by Hs-mode controller code.

0x0 Standard, fast or fast+ by

default, can be set to Hs-mode

by Hs-mode controller code.

I2C2_HS 0x0 Standard, fast or fast+ by

default, can be set to Hs-mode

by Hs-mode controller code.

0x0 Standard, fast or fast+ by

default, can be set to Hs-mode

by Hs-mode controller code.

EN_ILIM_FSM_CTRL 0x0 Buck/LDO regulators ILIM

interrupts do not affect FSM

triggers.

0x0 Buck/LDO regulators ILIM

interrupts do not affect FSM

triggers.

NSLEEP1_MASK 0x0 NSLEEP1(B) affects FSM

state transitions.

0x0 NSLEEP1(B) affects FSM

state transitions.

NSLEEP2_MASK 0x0 NSLEEP2(B) affects FSM

state transitions.

0x0 NSLEEP2(B) affects FSM

state transitions.

CONFIG_2 BB_CHARGER_EN 0x0 Disabled 0x0 Disabled

BB_VEOC 0x0 2.5V 0x0 2.5V

BB_ICHR 0x0 100uA 0x0 100uA

RECOV_CNT_REG_2 RECOV_CNT_THR 0xf 0xf 0xf 0xf

BUCK_RESET_REG BUCK1_RESET 0x0 0x0 0x0 0x0

BUCK2_RESET 0x0 0x0 0x0 0x0

BUCK3_RESET 0x0 0x0 0x0 0x0

BUCK4_RESET 0x0 0x0 0x0 0x0

BUCK5_RESET 0x0 0x0 0x0 0x0

SPREAD_SPECTRUM

_1

SS_EN 0x0 Spread spectrum disabled 0x0 Spread spectrum disabled

SS_MODE 0x1 Mixed dwell 0x1 Mixed dwell

SS_DEPTH 0x0 No modulation 0x0 No modulation

SPREAD_SPECTRUM

_2

SS_PARAM1 0x7 0x7 0x7 0x7

SS_PARAM2 0xc 0xc 0xc 0xc

Static NVM Settings www.ti.com

28 Optimized Dual TPS6594-Q1 PMIC User Guide for Jacinto

™

7 DRA829 or

TDA4VM Automotive PDN-0C

SLVUC99 – JANUARY 2022

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Loading...

Loading...