Clock Outputs (DCLKout and SDCLKout)

www.ti.com

36

SNAU145B–MAY 2013–Revised March 2018

Submit Documentation Feedback

Copyright © 2013–2018, Texas Instruments Incorporated

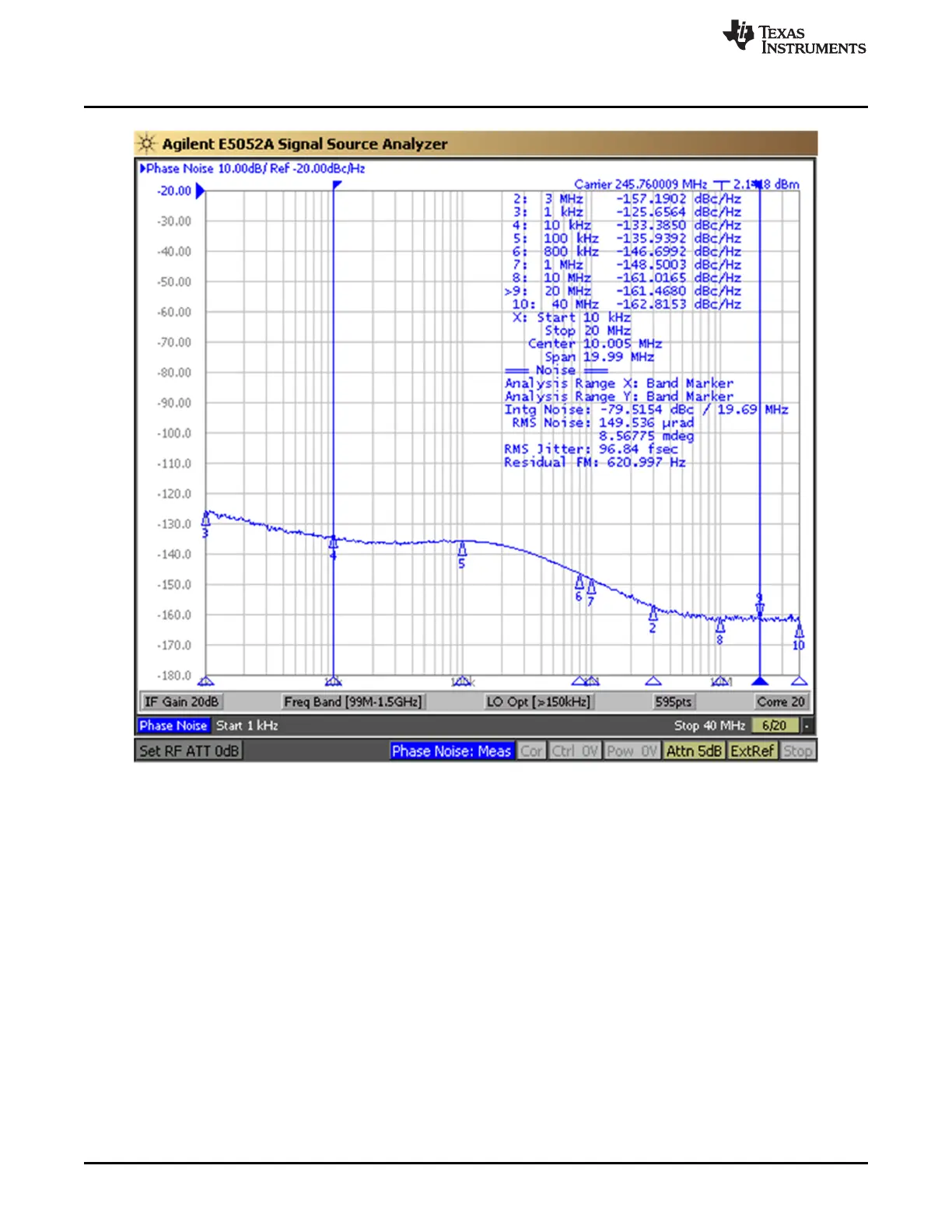

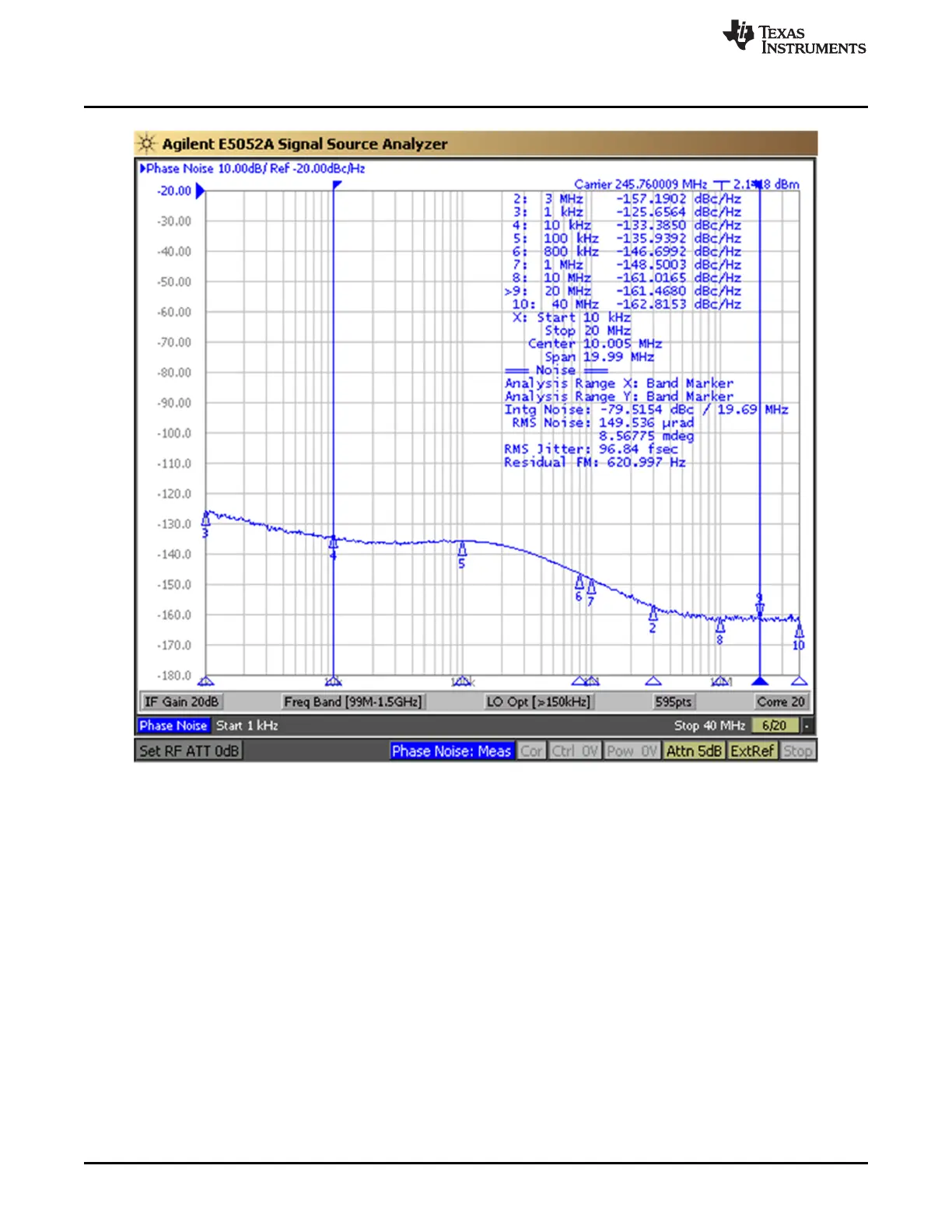

Typical Phase Noise Performance Plots

Figure 25. LMK04828 DCLKout2, VCO0, 245.76 MHz, Div10, LVPECL20 /w

240-Ω Emitter Resistor, DCLKoutX_MUX=Divider, IDL=1, ODL=0, Single Ended

Loading...

Loading...