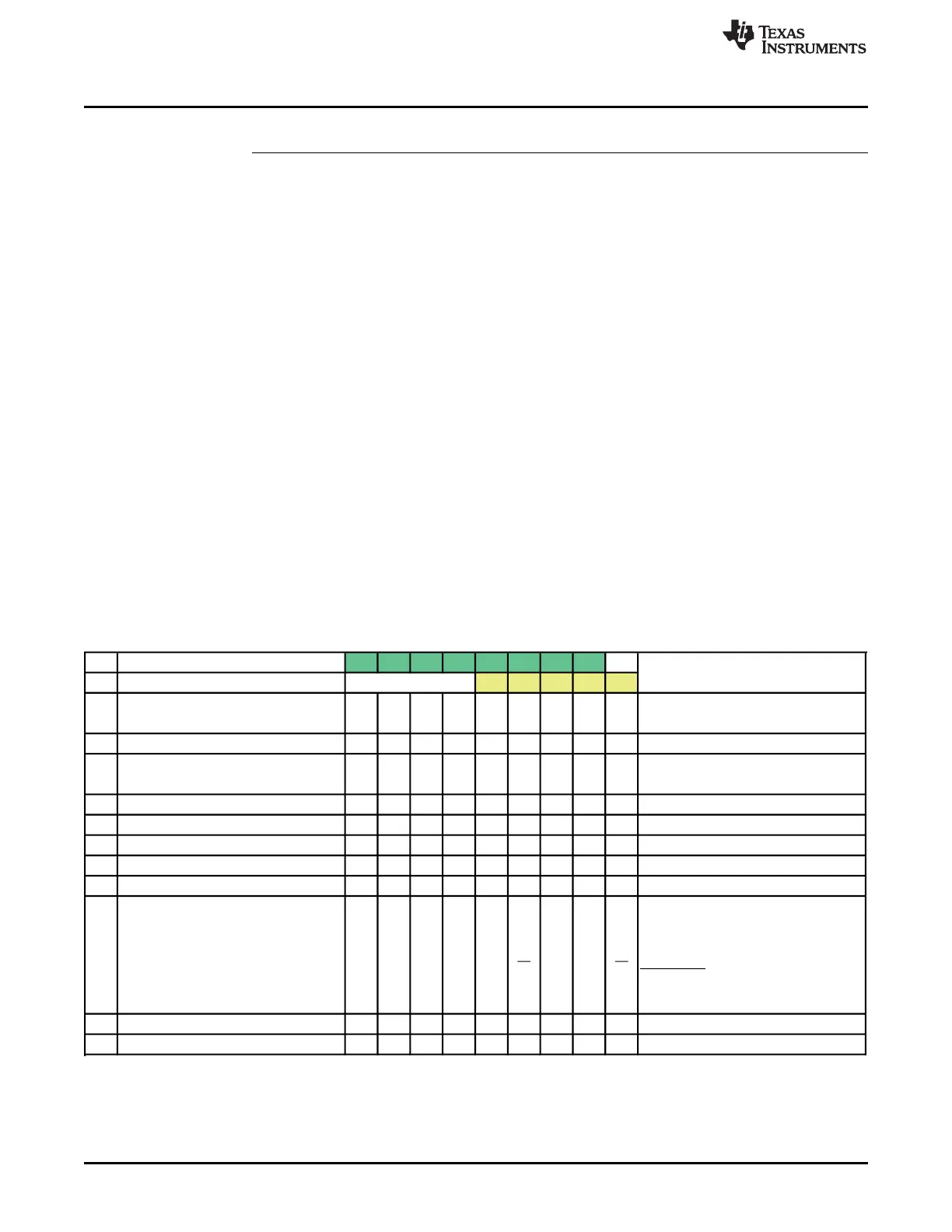

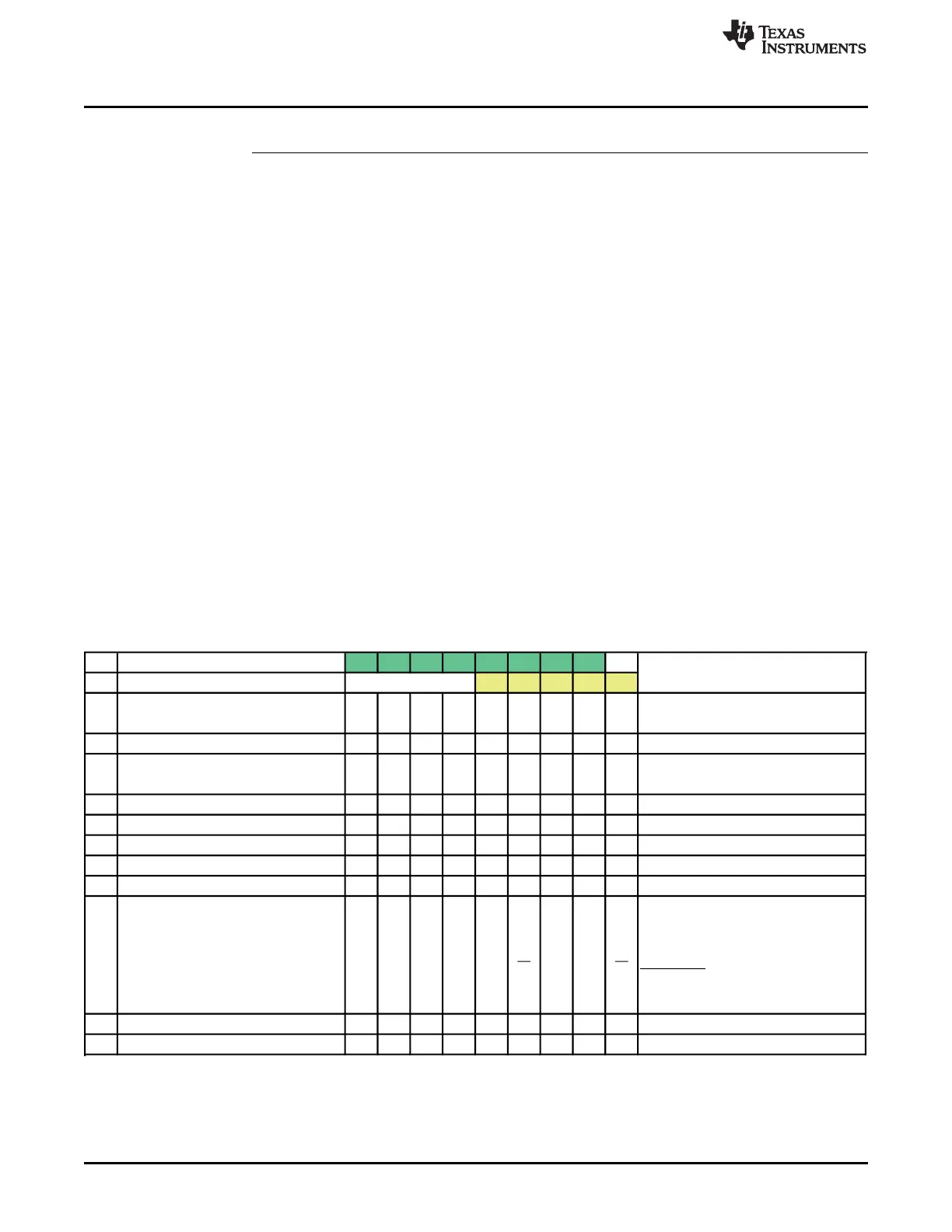

Instruction F1 F2 D1 D2 R1 R2 E W

R1 R2 E1 E2 E3

MPYF32 R6H, R5H, R0H

|| MOV32 *XAR7++, R4H

I2 F32TOUI16R R3H, R4H I2 I1

ADDF32 R3H, R2H, R0H

|| MOV32 *--SP, R2H

I4 MOV32 @XAR3, R6H I4 I3 I2 I1

I4 I3 I2 I1

I4 I3 I2 I1

I4 I3 I2 I1

I4 I3 I2 I1

I4

I4 samples the result as it enters

the R2 phase. The product

R6H=R5H*R0H (I1) finishes

computing in the E3 phase, but is

forwarded

as an operand to I4.

This makes I4 appear to be a 2p

instruction, but I4 actually takes

3p cycles to compute.

I4 I3 I2

I4 I3

I3

Comments

FPU pipeline--->

I1 I1

I3 I2 I1

Usage Notes and Known Design Exceptions to Functional Specifications

www.ti.com

26

SPRZ412K–December 2013–Revised February 2020

Submit Documentation Feedback

Copyright © 2013–2020, Texas Instruments Incorporated

TMS320F2837xD Dual-Core MCUs Silicon Revisions C, B, A, 0

Advisory FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation

Revision(s) Affected 0, A, B, C

Details This advisory applies when a multi-cycle (2p) FPU instruction is followed by a FPU-to-

CPU register transfer. If the FPU-to-CPU read instruction source register is the same as

the 2p instruction destination, then the read may be of the value of the FPU register

before the 2p instruction completes. This occurs because the 2p instructions rely on

data-forwarding of the result during the E3 phase of the pipeline. If a pipeline stall

happens to occur in the E3 phase, the result does not get forwarded in time for the read

instruction.

The 2p instructions impacted by this advisory are MPYF32, ADDF32, SUBF32, and

MACF32. The destination of the FPU register read must be a CPU register (ACC, P, T,

XAR0...XAR7). This advisory does not apply if the register read is a FPU-to-FPU register

transfer.

In the example below, the 2p instruction, MPYF32, uses R6H as its destination. The

FPU register read, MOV32, uses the same register, R6H, as its source, and a CPU

register as the destination. If a stall occurs in the E3 pipeline phase, then MOV32 will

read the value of R6H before the MPYF32 instruction completes.

Example of Problem:

MPYF32 R6H, R5H, R0H ; 2p FPU instruction that writes to R6H

|| MOV32 *XAR7++, R4H

F32TOUI16R R3H, R4H ; delay slot

ADDF32 R2H, R2H, R0H

|| MOV32 *--SP, R2H ; alignment cycle

MOV32 @XAR3, R6H ; FPU register read of R6H

Figure 4 shows the pipeline diagram of the issue when there are no stalls in the pipeline.

Figure 4. Pipeline Diagram of the Issue When There are no Stalls in the Pipeline

Loading...

Loading...