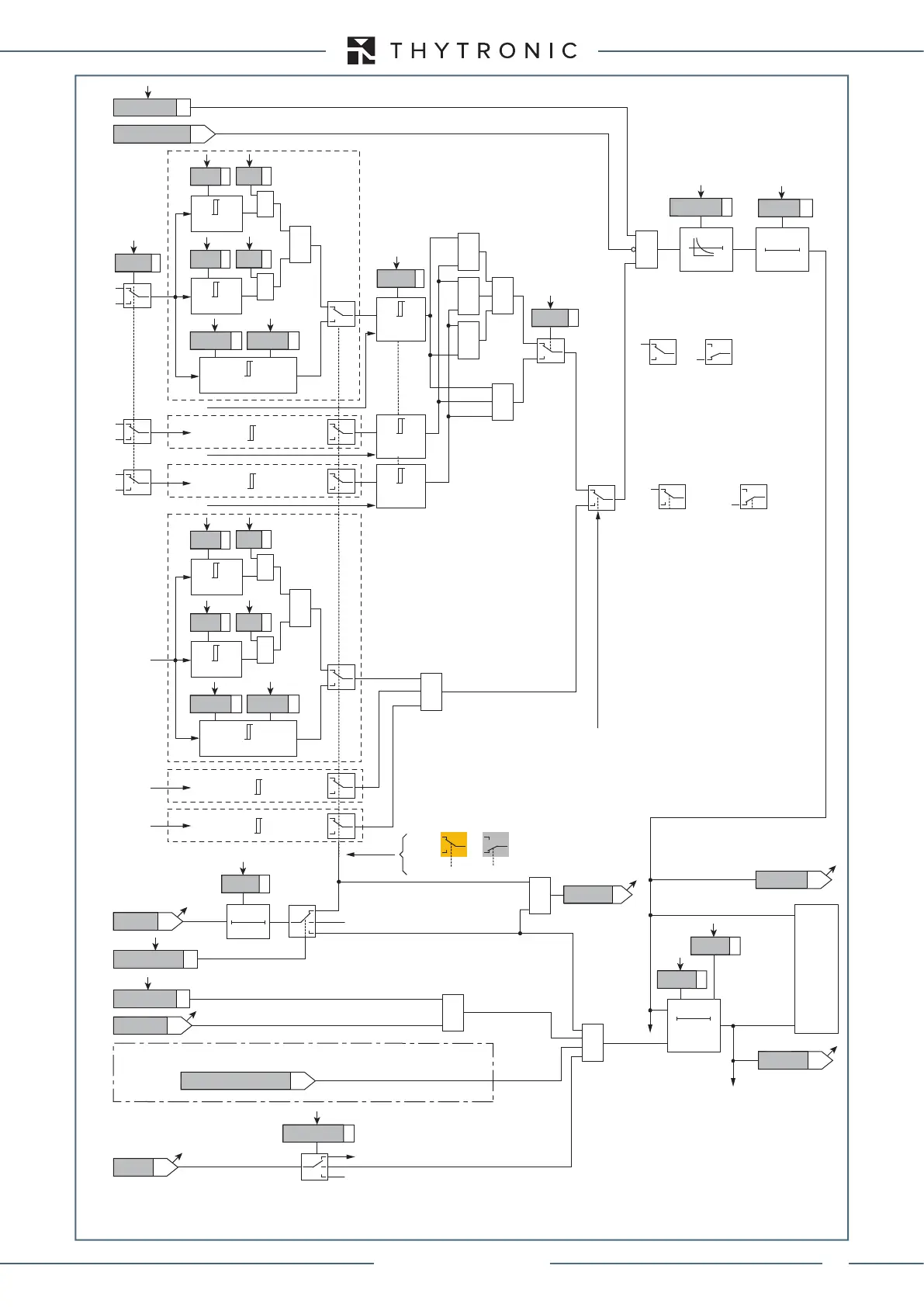

Fun_67S1.ai

I

L1

I

L1

∙cos

≥1

≥1

≥1

ON≡Inhibit (from IP>>, IPD>>> and/or IPD>>>> element)

ON≡Enable IPD> directional overcurrent element

IPD> inhibition

&

&

&

&

I

PDCLP>def

I

PDCLP>inv

≥

I

PDCLP>

A

B

C =“2/3”

C

Non-directional

(from 74VT)

Non-directional

D =“1/3”

A = Directional

B = Non-directional

Logic67

C

D

IPD> Enable

≥1

CB-State

Start I

2ndh>

Block1, Block2, Block4

T 0

t

PDCLP

>

&

2nd harmonic restraint enable (ON≡Enable)

I>2ndh-REST

IPDCLP>Mode

t

PDCLP

>

A

B

C

A =“1”A =“0 or OFF”

IPD> overcurrent directional element (67) block diagram

A = ON - Change setting within CLP

B = OFF - CLP disabled

C = ON - Element blocking within CLP

≥1

CLP IPD>

&

State

I

PD>inv

≥

I

PD>def

≥

I>

inv

I

PD>def

Settore

ThetaP>

Settore

Settore

&

State

Mode67

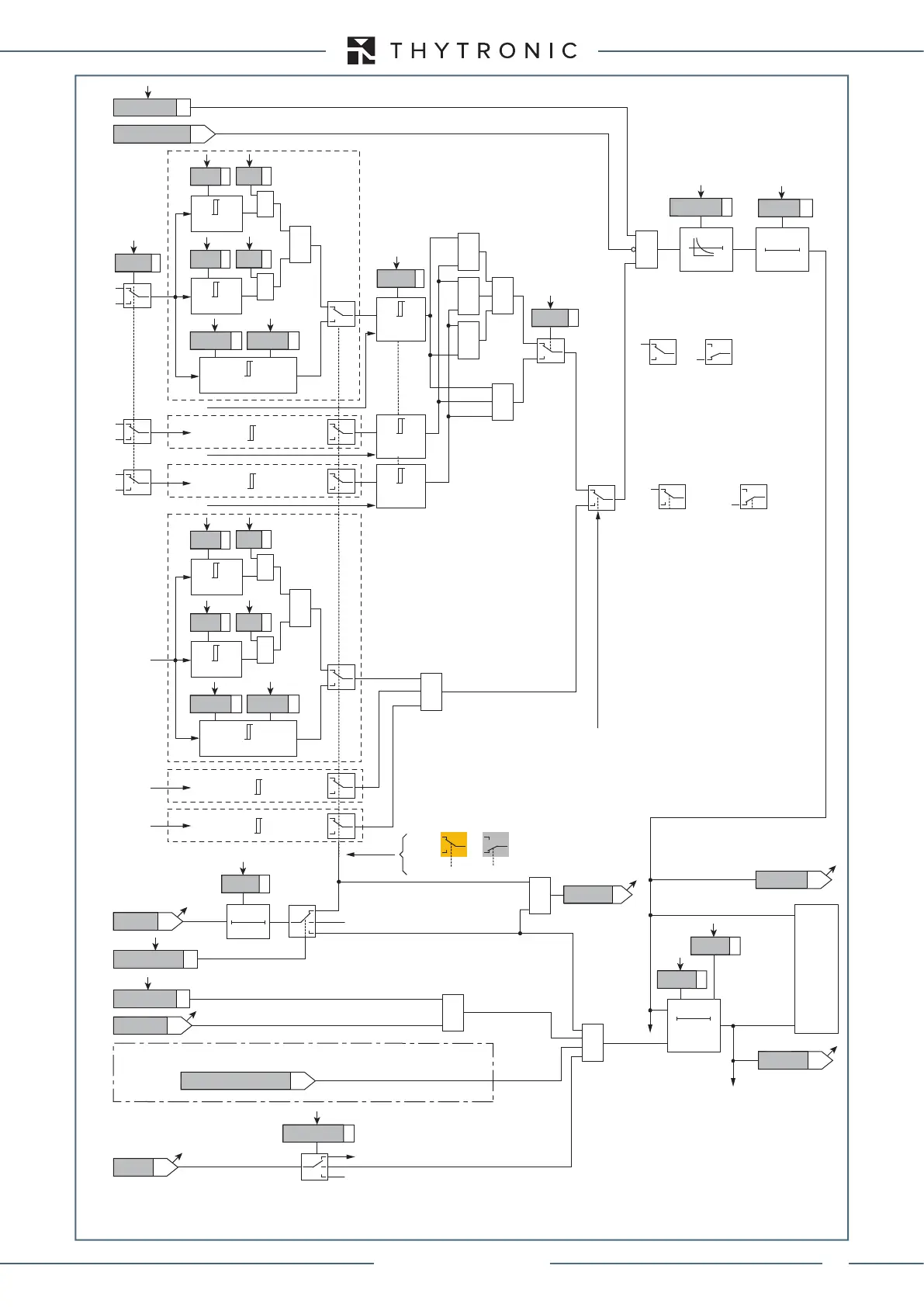

I

L2

Input U

31

I

L2

∙cos

Input U

23

Input U

12

I

L3

I

L3

∙cos

I

L1

I

L2

I

L3

≥1

I

PDCLP>def

I

PDCLP>inv

≥

I

PDCLP>

&

State

I

PD>inv

≥

I

PD>def

≥

I>

inv

I

PD>def

&

State

≥1

Block by 74VT (ON≡Block)

Internal or external

OFF

74VT

74VTint/ext67

t

PD>RES

T0

RESET

t

PD>

0T

t

PD>inv

t

PD>RES

Start IPD>

Trip IPD>

TRIPPING MATRIX

(LED+RELAYS)

I

PD>

Curve

0T

IPD>TR-K

IPD>TR-L

IPD>ST-L

IPD>ST-K

t

PD>def

D

A

B

Phase directional overcurrent (67) - First element logic diagram (IPD>)

Loading...

Loading...