19

ViewSonic Corporation Confidential - Do Not Copy PJ503D-1

1. EE Assembly and Alignment Concern:

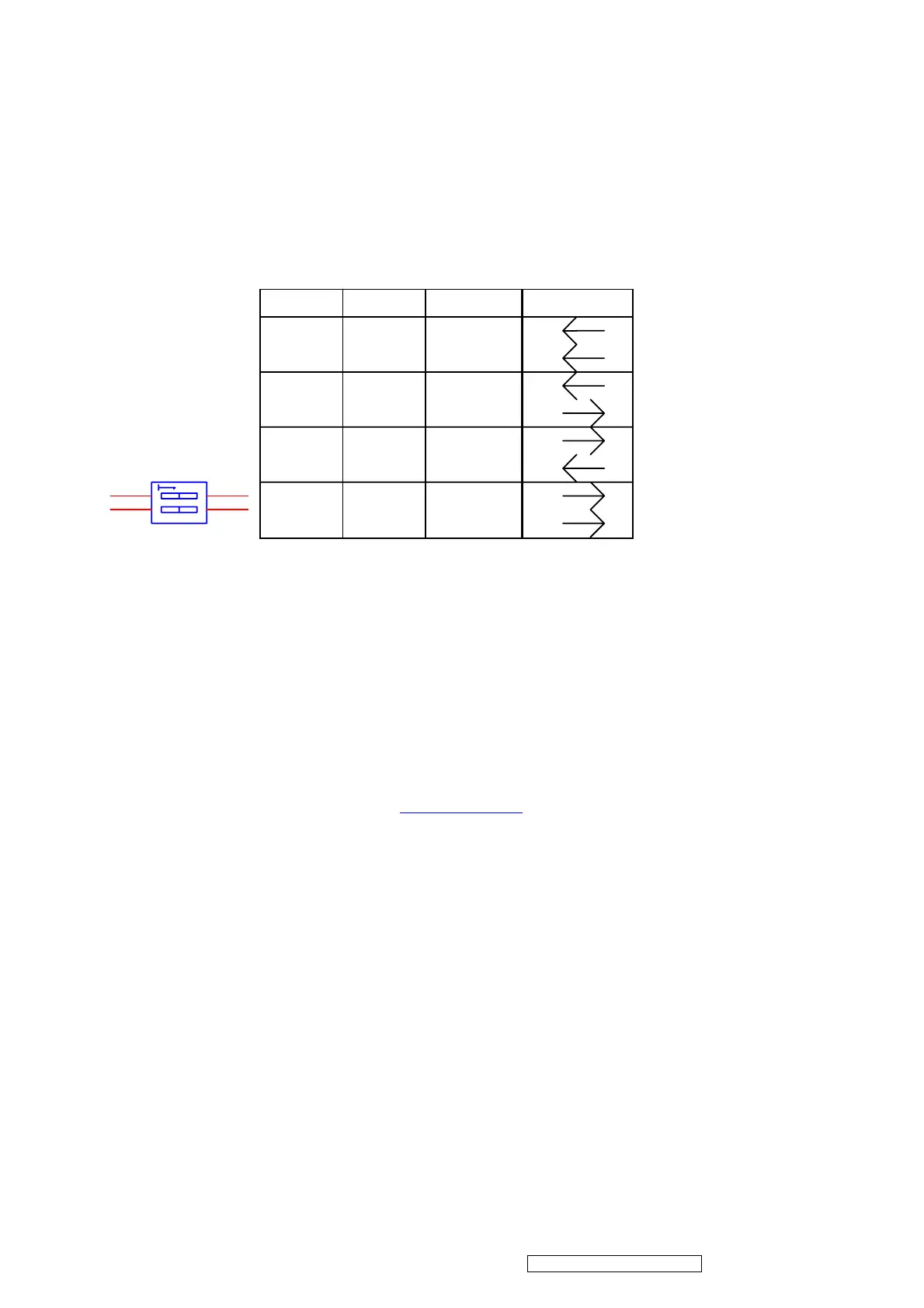

1.1 DMD Bias Voltage Alignment

Equipment:

- None

Procedure:

1. Watch DMD chip Label (Example: 9477000 0234B)

2. Switch the DIP switch on DMD board according to the red character on the DMD chip

3.

H1

6240019001

1

2

4

3

BINSEL1 BINSEL0 DMD Bin

1 0 D

1 1 E

0 1 C

0 0 B

Direction

1.2 Formatter board check procedure

Equipment:

- Pattern generator

Procedure:

1. Connect power, D-sub, into projector.

2. Light on projector.

3. Testing below patterns and resolution is 854*480@60Hz

(480P)

(1) General-1 pattern. (Pattern 1)

(2) 32 grays pattern. (Pattern 48)

(3) White pattern. (Pattern 41)

(4) SMPTE pattern. (Pattern 5)

4. The formatter board would be note fail if above three image-quality is not good.

5. Test the connection between formatter board to keypad board and IR board.

6. The formatter board would be note fail if there are some wires is broken in formatter board.

Loading...

Loading...