Spartan-6 FPGA GTP Transceiver SIS Kit (HyperLynx) www.xilinx.com 21

UG396 (v1.0) June 10, 2010

Appendix B

HSPICE and HyperLynx/Eldo

Correlation Results

Introduction

The results generated by the HyperLynx and Eldo simulators are validated by executing a

set of the same simulations in both simulators and plotting the waveform results on top of

each other to verify identical outcomes.

Note:

HSPICE version A-2009.03 was used for the S-parameter/circuit correlation and the GTP

REFCLK and GTP transceiver simulations.

For this correlation, only the silicon models for the GTP transmitter and receiver are used.

Package and channel models are not used, except for the GTP reference clock, where the

package model is included.

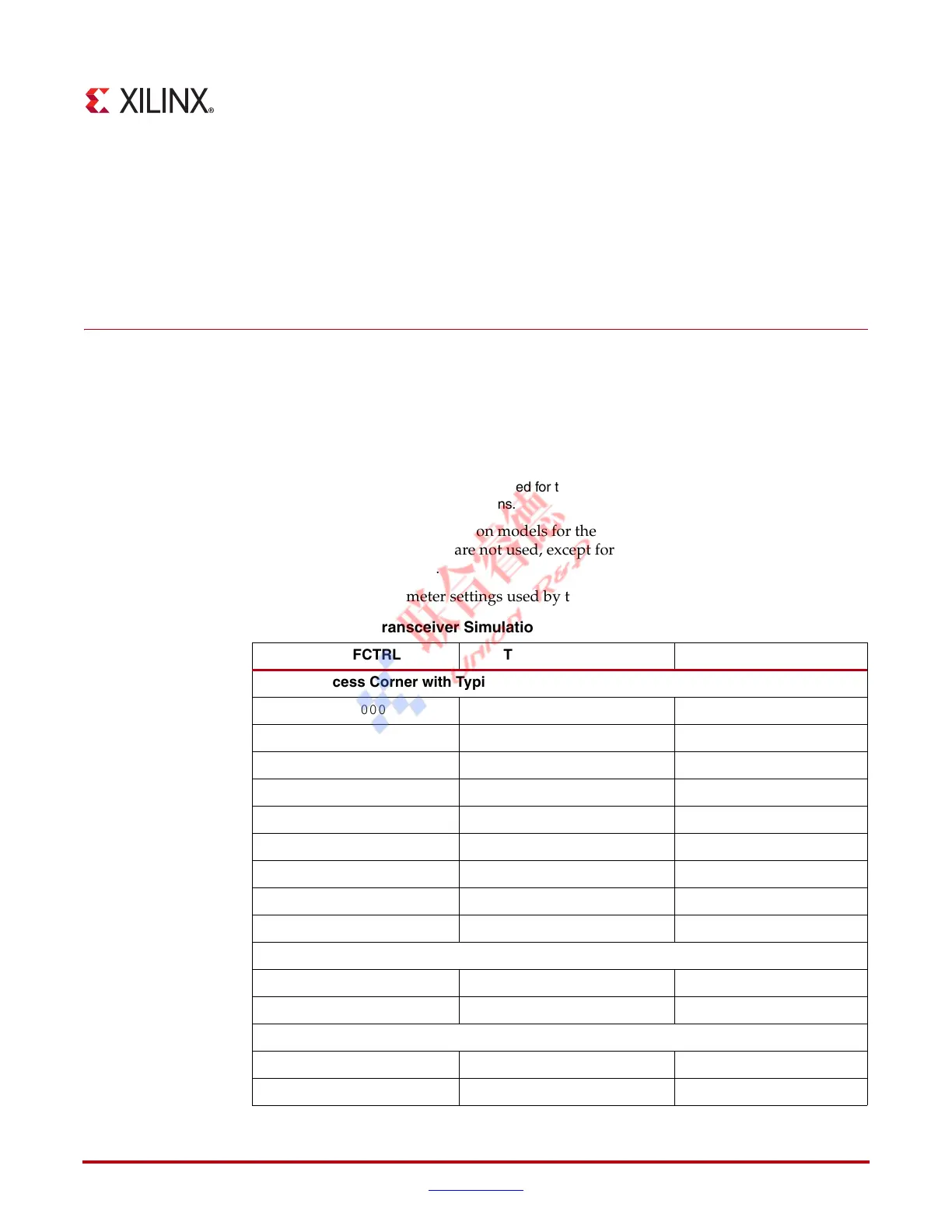

Table B-1 lists the parameter settings used by the GTP transceiver simulations.

Table B -1: GTP Transceiver Simulations Parametric Settings

TXDIFFCTRL TXPREEMPHASIS RXEQMIX

Typical Process Corner with Typical Voltage and Typical Temperature

4'b0000 3'b000 2'b00

4'b0100 3'b000 2'b00

4'b1010 3'b000 2'b00

4'b1010 3'b010 2'b00

4'b1010 3'b100 2'b00

4'b1010 3'b111 2'b00

4'b1010 3'b000 2'b01

4'b1010 3'b000 2'b10

4'b1010 3'b000 2'b11

Fast Process Corner with Maximum Voltage and Cold Temperature

4'b1010 3'b000 2'b00

4'b1010 3'b011 2'b00

Slow Process Corner with Minimum Voltage and Hot Temperature

4'b1010 3'b000 2'b00

4'b1010 3'b011 2'b00

Loading...

Loading...