34 www.xilinx.com VC7203 IBERT Getting Started Guide

UG847 (v3.0) July 10, 2013

Chapter 1: VC7203 IBERT Getting Started Guide

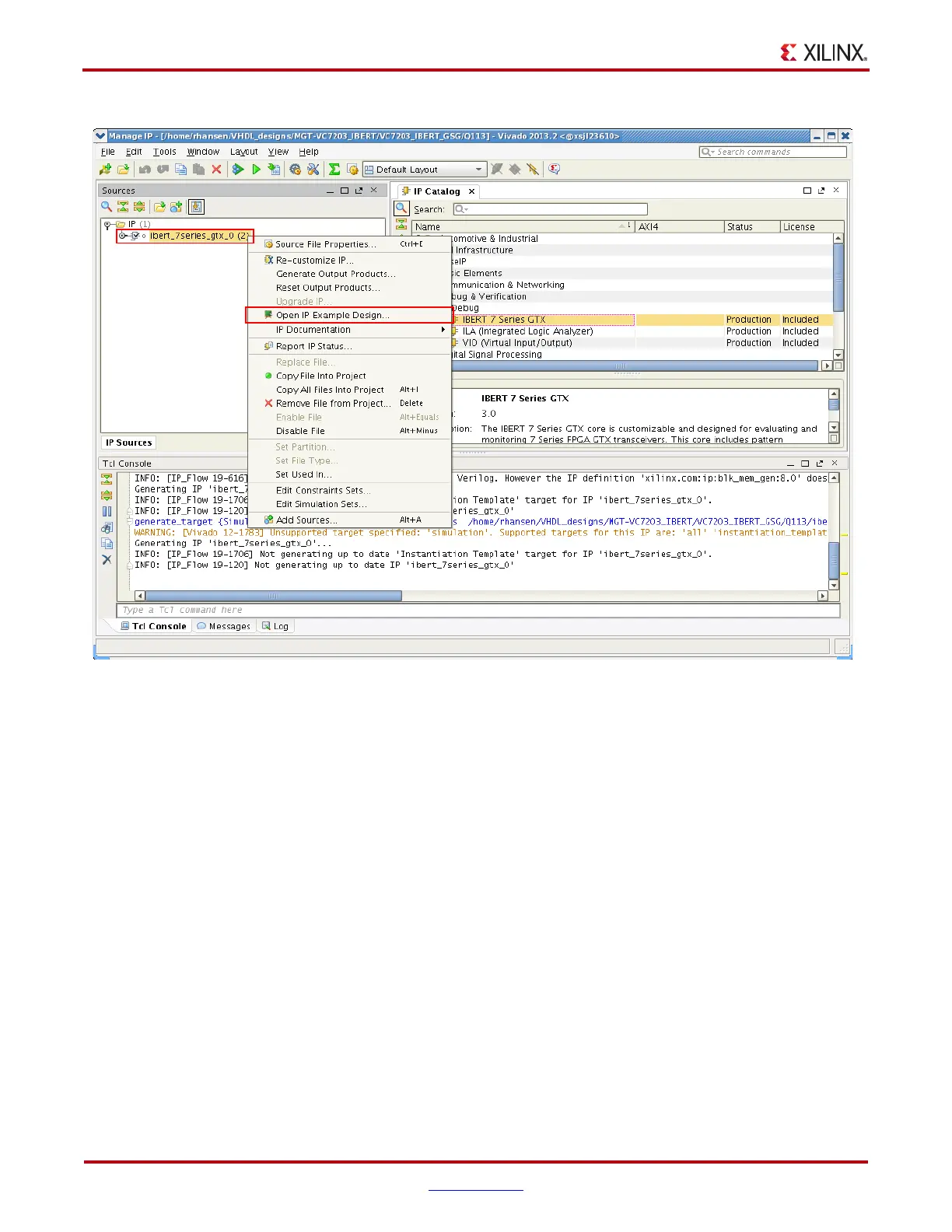

11. In the new window, select Tools > Run Tcl Script. In the Run Script window, navigate

to add_scm2.tcl in the extracted files and press OK. The SuperClock-2 Module

Design Sources and Constraints are automatically added to the example design

(Figure 1-28).

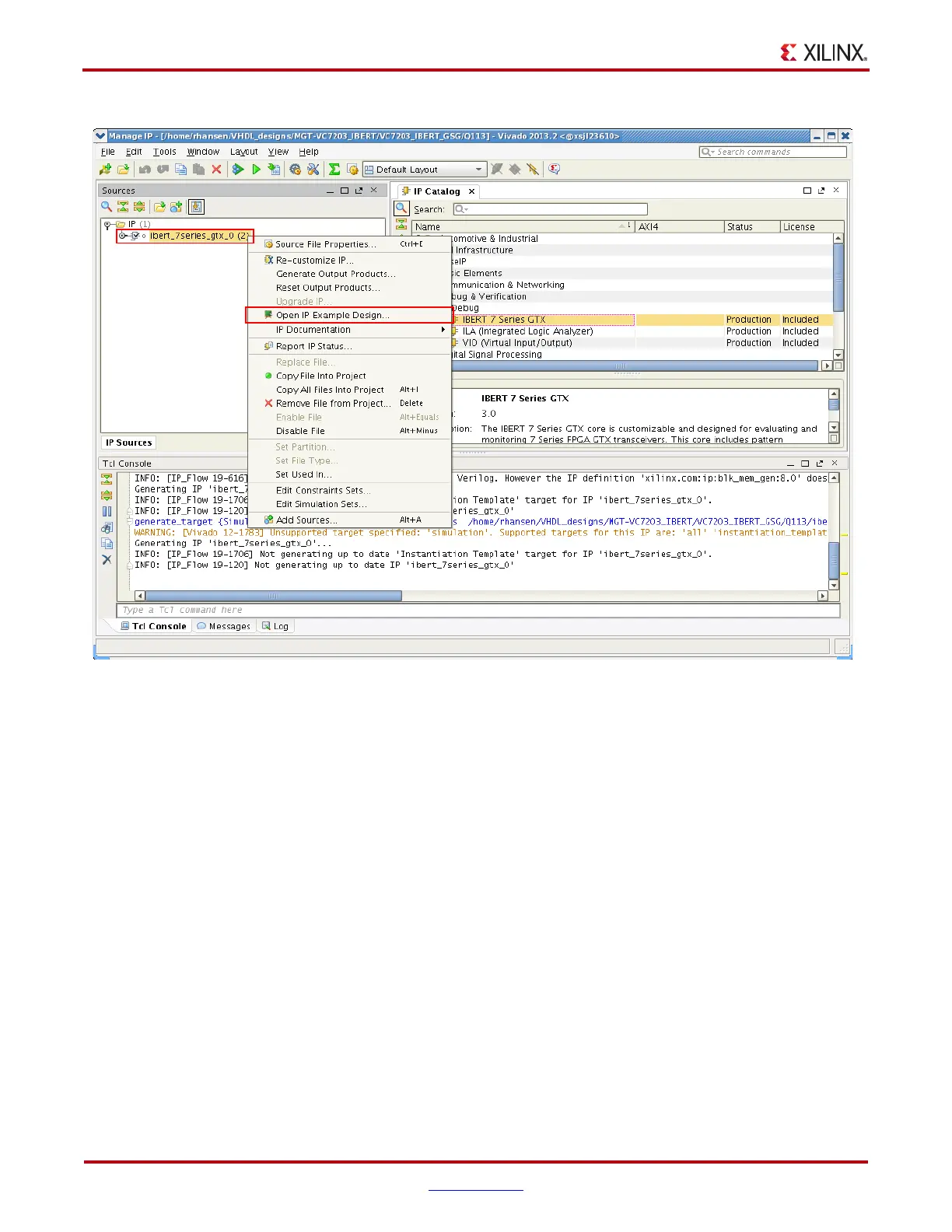

X-Ref Target - Figure 1-27

Figure 1-27: Open Example Design

Loading...

Loading...