VC7203 IBERT Getting Started Guide www.xilinx.com 35

UG847 (v3.0) July 10, 2013

Creating the GTX IBERT Core

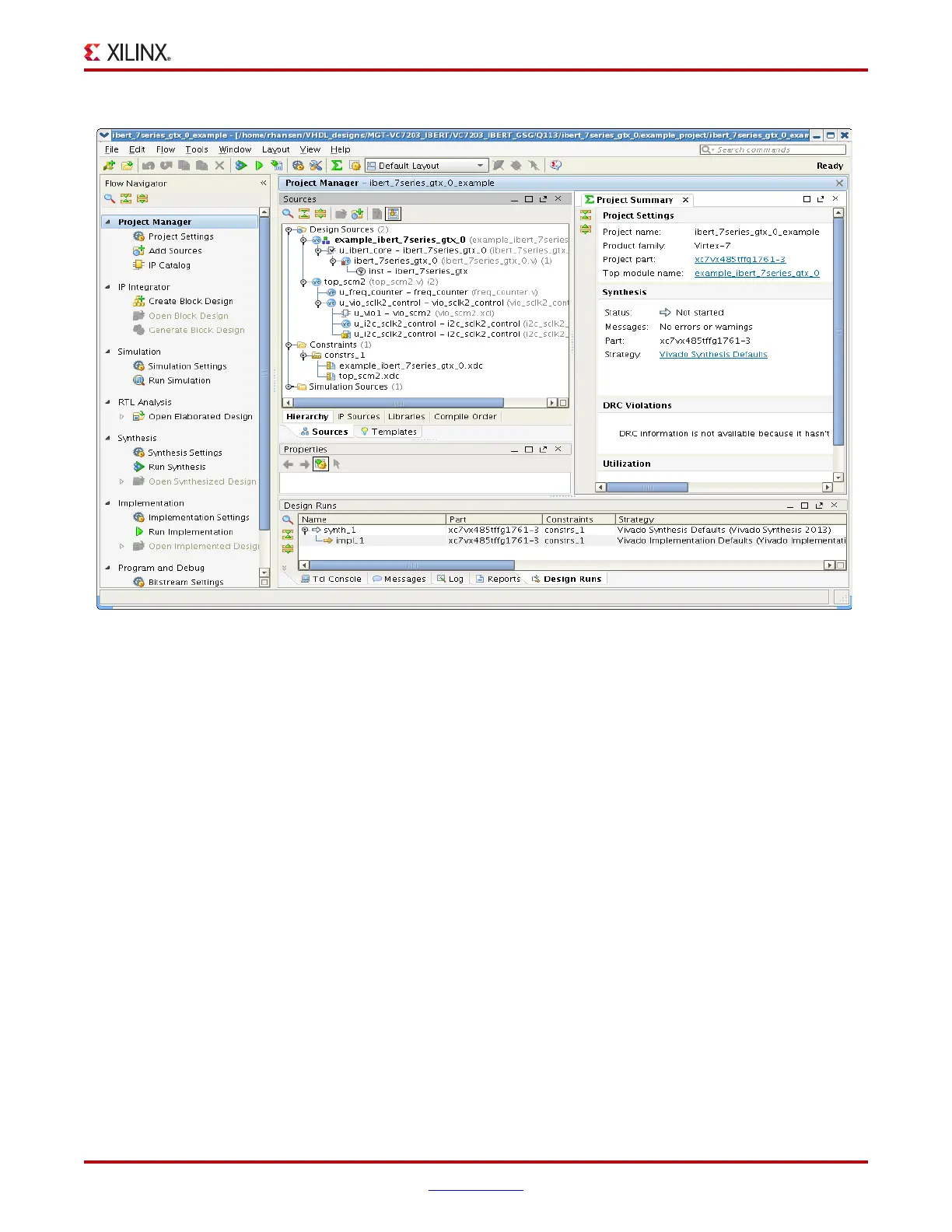

12. The SuperClock-2 source code now needs to be added to the example ibert wrapper.

Double-click example_ibert_7series_gtx_0 in the Design Sources to open the verilog

code. Add the top level ports from top_scm2.v to the module declaration and

instantiate the top_scm2 module in the example ibert wrapper (Figure 1-29). Click

File > Save File.

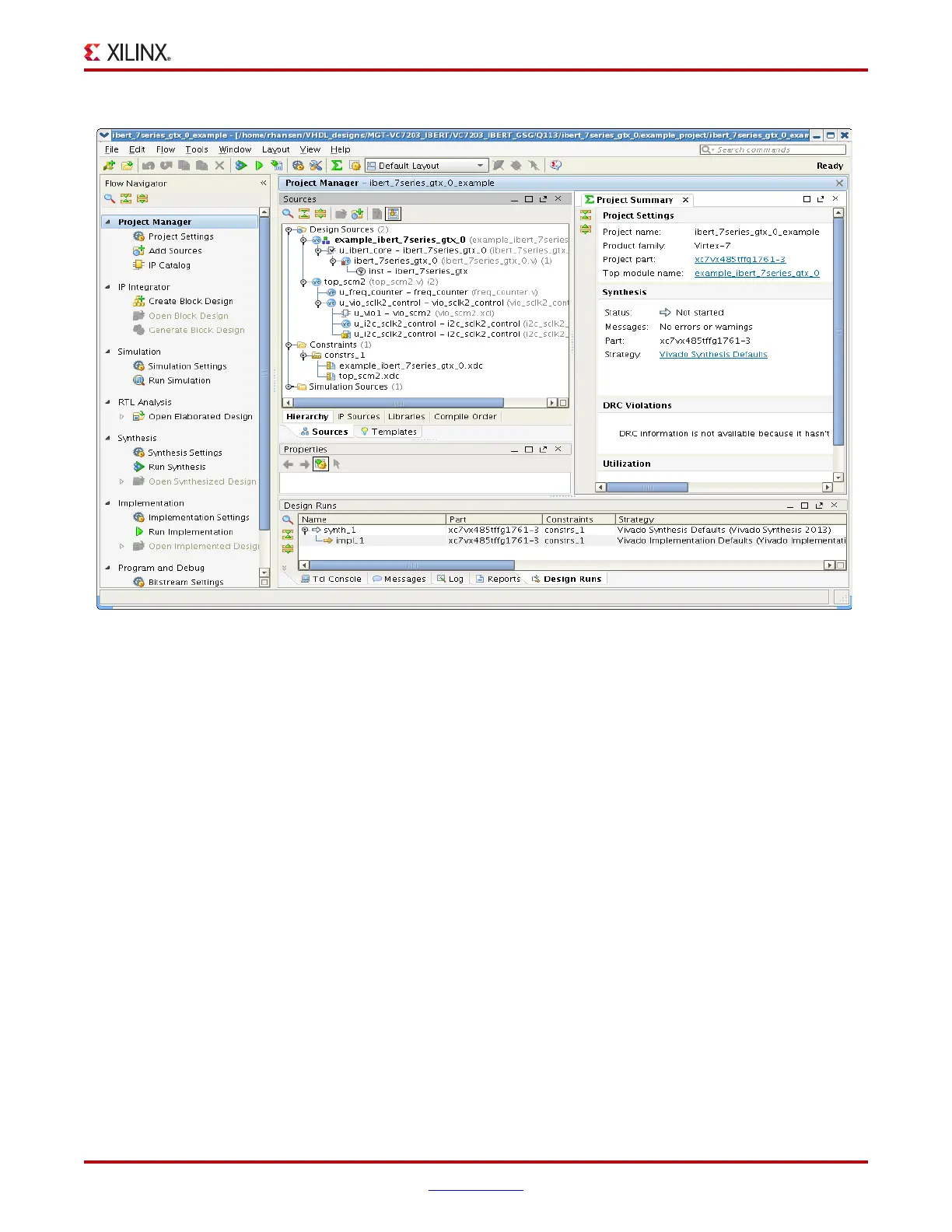

X-Ref Target - Figure 1-28

Figure 1-28: Sources after Running add_scm2.tcl

Loading...

Loading...