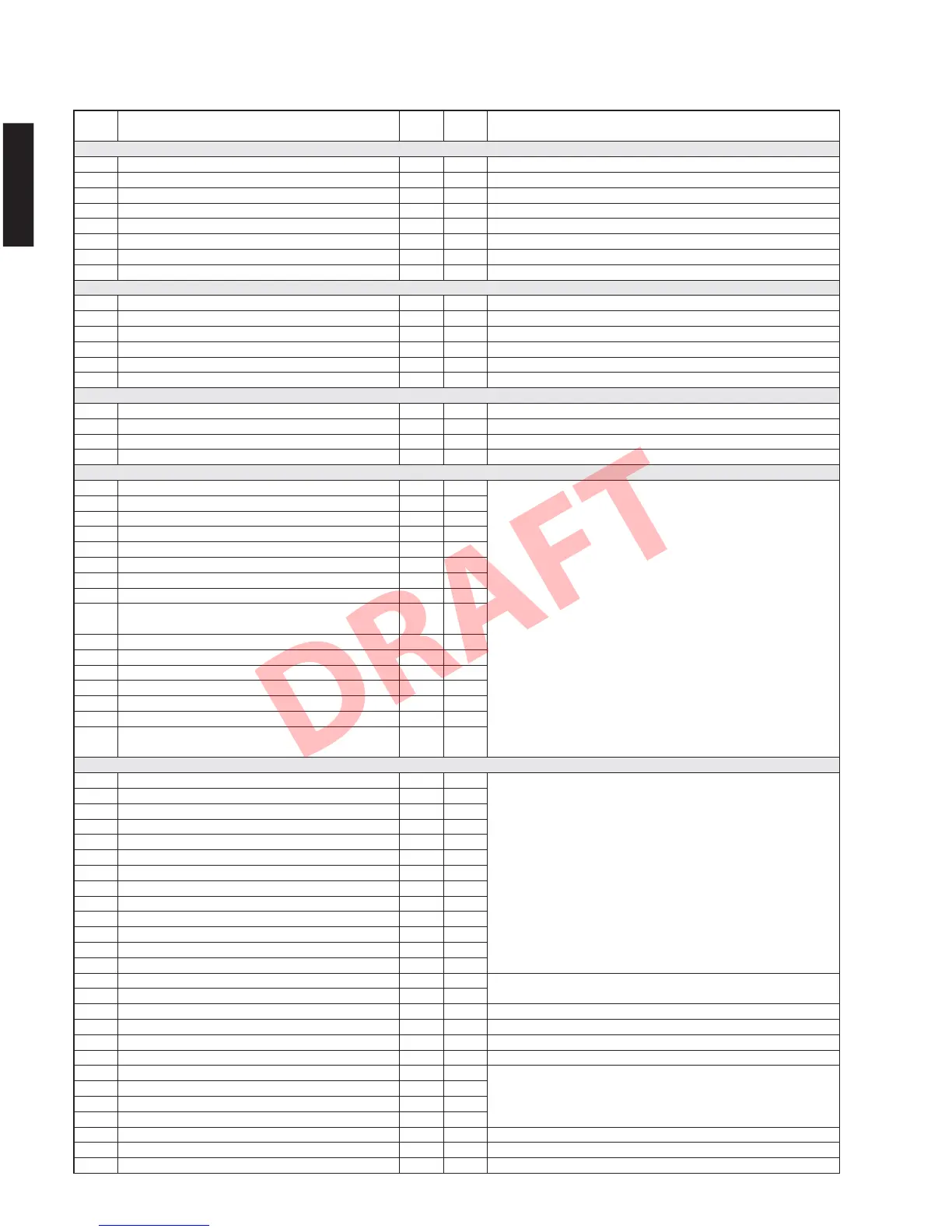

Pin

No.

Function Name

TYPE

(1)

PULL

(2)

Detail of Function

Device Reset and JTAG

G3 RESET I EMIFA Async chip select

L4 AMUTE0/ RESETOUT O (3) IPD Reset output. Multiplexed with McASP0 mute output.

J1 TMS I IPU JTAG test mode select

J2 TDI I IPU JTAG test data input

J3 TDO O IPD JTAG test data output

H3 TCK I IPU JTAG test clock

J4 TRST I IPD JTAG test reset

J5 EMU[0]/GP7[15] I/O IPU Miscellaneous emulation pin.

High-Frequency Oscillator and PLL

R12 EMA_CLK/OBSCLK/AHCLKR2/ GP1[15] O IPU PLL Observation Clock

F2 OSCIN I Oscillator input

F1 OSCOUT O Oscillator output

E2 OSCVSS GND Oscillator ground (for filter only)

D1 PLL0_VDDA PWR PLL analog VDD (1.2-V filtered supply)

E1 PLL0_VSSA GND PLL analog VSS (for filter)

Real-Time Clock and 32-kHz Oscillator

G1 RTC_CVDD PWR RTC module core power ( isolated from rest of chip CVDD)

H1 RTC_XI I Low-frequency (32-kHz) oscillator receiver for real-time clock

H2 RTC_XO O Low-frequency (32-kHz) oscillator driver for real-time clock

G2 RTC_VSS GND Oscillator ground (for filter)

External Memory Interface A (ASYNC, SDRAM)

M16 EMA_D[15]/UHPI_HD[15]/ GP0[15] I/O IPD EMIFA data bus

N14 EMA_D[14]/UHPI_HD[14]/GP0[14] I/O IPD

N16 EMA_D[13]/UHPI_HD[13]/GP0[13] I/O IPD

P14 EMA_D[12]/UHPI_HD[12]/GP0[12] I/O IPD

P16 EMA_D[11]/UHPI_HD[11]/GP0[11] I/O IPD

R14 EMA_D[10]/UHPI_HD[10]/GP0[10] I/O IPD

T14 EMA_D[9]/UHPI_HD[9]/GP0[9] I/O IPD

N12 EMA_D[8]/UHPI_HD[8]/GP0[8] I/O IPD

M15 EMA_D[7]/MMCSD_DAT[7]/UHPI_HD[7]/GP0[7]/ I/O IPU

BOOT[13]

N13 EMA_D[6]/MMCSD_DAT[6]/UHPI_HD[6]/GP0[6] I/O IPU

N15 EMA_D[5]/MMCSD_DAT[5]/UHPI_HD[5]/GP0[5] I/O IPU

P13 EMA_D[4]/MMCSD_DAT[4]/UHPI_HD[4]/GP0[4] I/O IPU

P15 EMA_D[3]/MMCSD_DAT[3]/UHPI_HD[3]/GP0[3] I/O IPU

R13 EMA_D[2]/MMCSD_DAT[2]/UHPI_HD[2]/GP0[2] I/O IPU

R15 EMA_D[1]/MMCSD_DAT[1]/UHPI_HD[1]/GP0[1] I/O IPU

T13 EMA_D[0]/MMCSD_DAT[0]/UHPI_HD[0]/GP0[0]/ I/O IPU

BOOT[12]

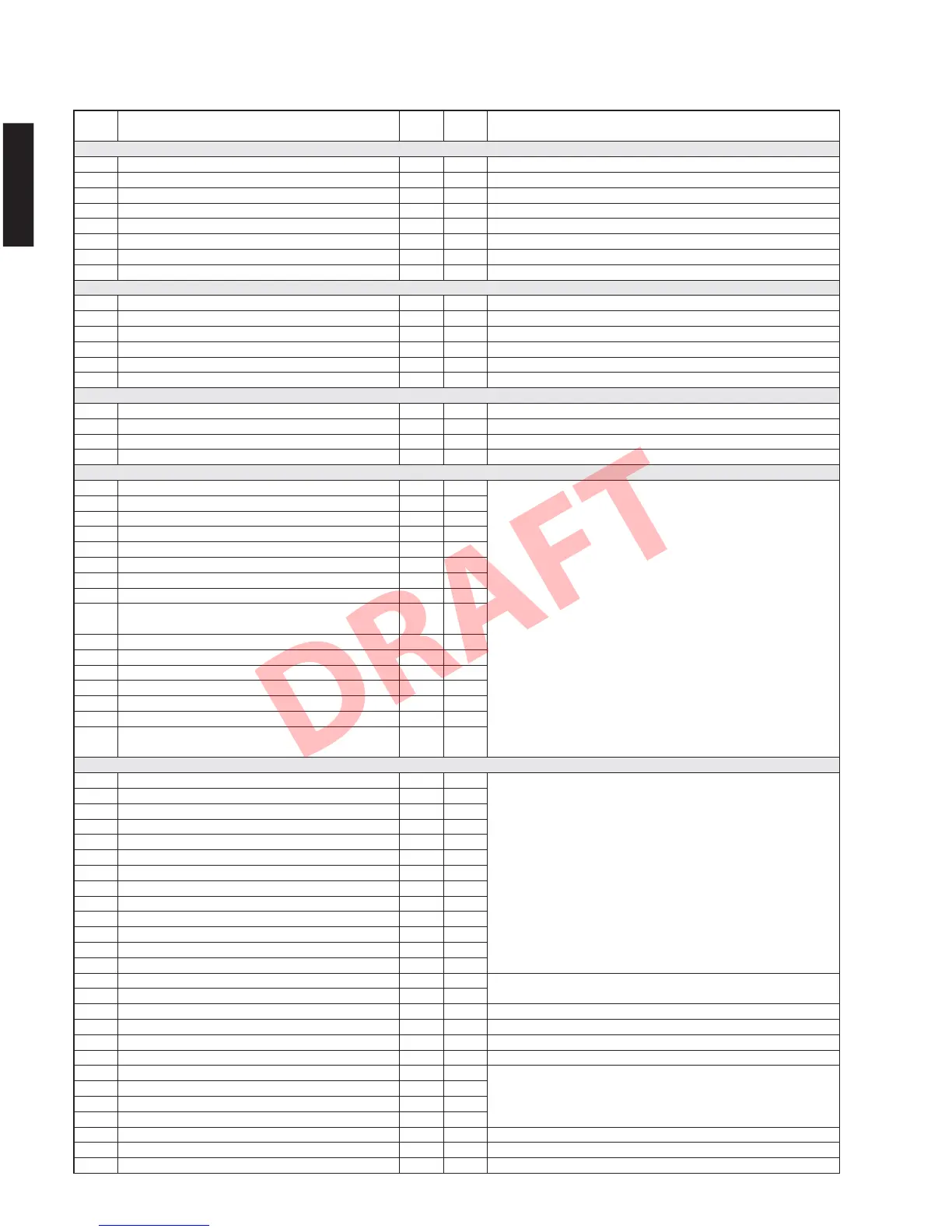

External Memory Interface A (EMIFA) Terminal Functions (continued)

N11 EMA_A[12]/ GP1[12] O IPU EMIFA address bus

P11 EMA_A[11]/ GP1[11] O IPU

N8 EMA_A[10]/ GP1[10] O IPU

R11 EMA_A[9]/ GP1[9] O IPU

T11 EMA_A[8]/ GP1[8] O IPU

N10 EMA_A[7]/ GP1[7] O IPD

P10 EMA_A[6]/ GP1[6] O IPD

R10 EMA_A[5]/ GP1[5] O IPD

T10 EMA_A[4]/ GP1[4] O IPD

N9 EMA_A[3]/ GP1[3] O IPD

P9 EMA_A[2]/MMCSD_CMD/UHPI_HCNTL1/GP1[2] O IPU

R9 EMA_A[1]/MMCSD_CLK/UHPI_HCNTL0/GP1[1] O IPU

T9 EMA_A[0]/ GP1[0] O IPD

P8 EMA_BA[1]/ UHPI_HHWIL/GP1[13] O IPU EMIFA bank address

R8 EMA_BA[0]/ GP1[14] O IPU

R12 EMA_CLK/OBSCLK/AHCLKR2/GP1[15] O IPU EMIFA clock

T12 EMA_SDCKE/GP2[0] O IPU EMIFA SDRAM clock enable

N7 EMA_RAS /EMA_CS[5]/GP2[2] O IPU EMIFA SDRAM row address strobe

L16 EMA_CAS /EMA_CS[4]/GP2[1] O IPU EMIFA SDRAM column address strobe

N7 EMA_RAS/ EMA_CS[5] /GP2[2] O IPU EMIFA Async chip select

L16 EMA_CAS/ EMA_CS[4] /GP2[1] O IPU

T7 EMA_CS[3] /AMUTE2/GP2[6] O IPU

P7 EMA_CS[2] /UHPI_HCS/GP2[5]/BOOT[15] O IPU

T8 EMA_CS[0] /UHPI_HAS/GP2[4] O IPU EMIFA SDRAM chip select

M13

EMA_WE /UHPI_HRW/AXR0[12]/GP2[3]/BOOT[14]

O IPU EMIFA SDRAM write enable

P12

EMA_WE_DQM[1] /UHPI_HDS2/AXR0[14]/GP2[8]

O IPU EMIFA write enable/data mask for EMA_D[15:8]

92

YSP-CU4300/YSP-CU3300/NS-WSW160

YSP-CU4300/YSP-CU3300/

NS-WSW160

Loading...

Loading...