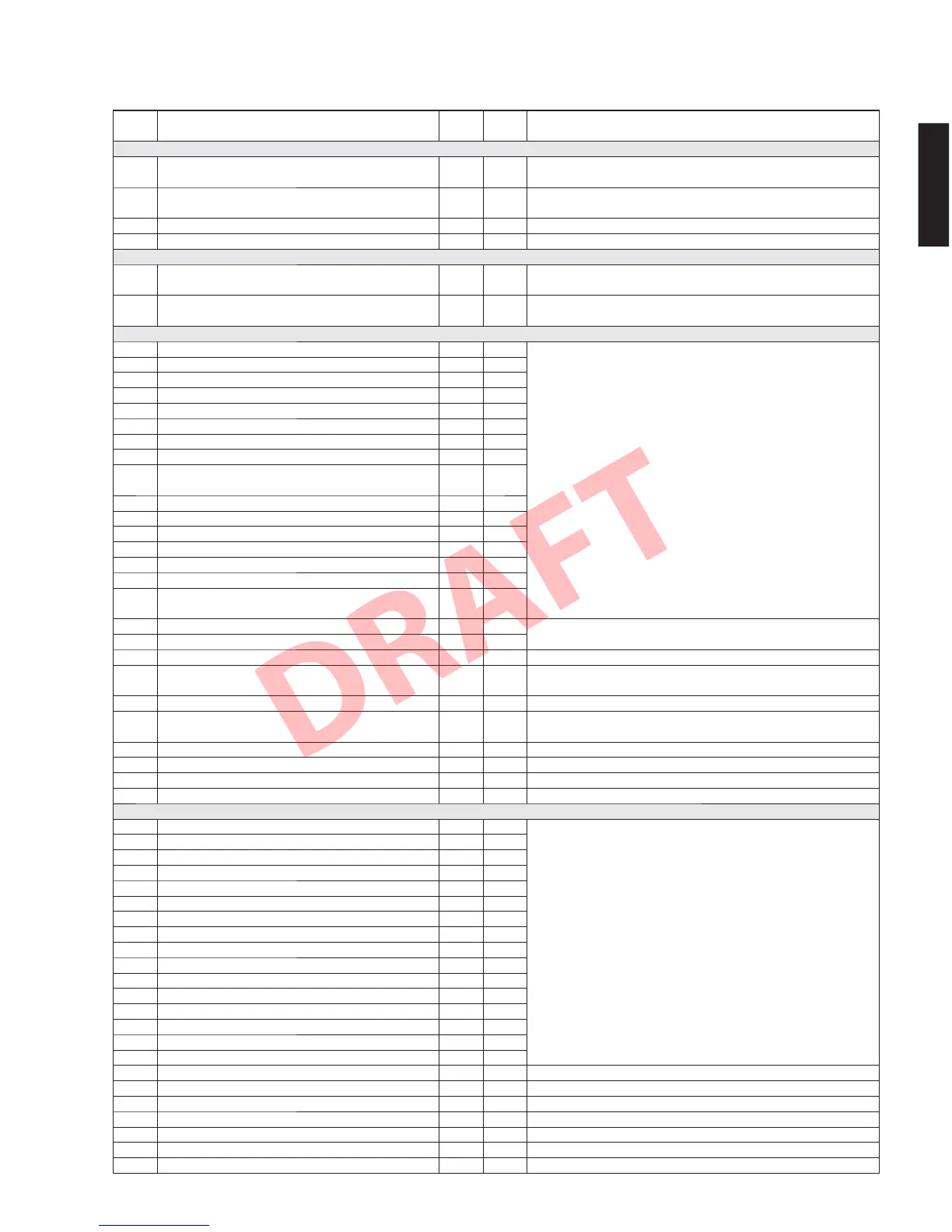

Pin

No.

Function Name

TYPE

(1)

PULL

(2)

Detail of Function

Inter-Integrated Circuit Modules(I2C0, I2C1)

R3 UART0_RXD/I2C0_SDA/TM64P0_IN12/GP5[8]/ I/O IPU I2C0 serial data

BOOT[8]

P3 UART0_TXD/I2C0_SCL/TM64P0_OUT12/GP5[9]/ I/O IPU I2C0 serial clock

BOOT[9]

N5 SPI1_SIMO[0]/I2C1_SDA/GP5[6]/BOOT[6] I/O IPU I2C1 serial Data

P5 SPI1_SOMI[0]/I2C1_SCL/GP5[5]/BOOT[5] I/O IPU I2C1 serial clock

Timers

R3 UART0_RXD/I2C0_SDA/TM64P0_IN12/GP5[8]/ I IPU Timer0 lower input

BOOT[8]

P3 UART0_TXD/I2C0_SCL/TM64P0_OUT12/GP5[9]/ O IPU Timer0 lower output

BOOT[9]

Universal Host-Port Interface (UHPI)

M16 EMA_D[15]/UHPI_HD[15]/GP0[15] I/O IPD UHPI data bus

N14 EMA_D[14]/UHPI_HD[14] /GP0[14] I/O IPD

N16 EMA_D[13]/UHPI_HD[13] /GP0[13] I/O IPD

P14 EMA_D[12]/UHPI_HD[12] GP0[12] I/O IPD

P16 EMA_D[11]/UHPI_HD[11] /GP0[11] I/O IPD

R14 EMA_D[10]/UHPI_HD[10] GP0[10] I/O IPD

T14 EMA_D[9]/UHPI_HD[9] /GP0[9] I/O IPD

N12 EMA_D[8]/UHPI_HD[8] /GP0[8] I/O IPD

M15 EMA_D[7]/MMCSD_DAT[7]/UHPI_HD[7]/GP0[7]/ I/O IPU

BOOT[13]

N15 EMA_D[6]/MMCSD_DAT[6]/UHPI_HD[6]/GP0[6] I/O IPU

N15 EMA_D[5]/MMCSD_DAT[5]/UHPI_HD[5]/GP0[5] I/O IPU

P13 EMA_D[4]/MMCSD_DAT[4]/UHPI_HD[4]/GP0[4] I/O IPU

P15 EMA_D[3]/MMCSD_DAT[3]/UHPI_HD[3]/GP0[3] I/O IPU

R13 EMA_D[2]/MMCSD_DAT[2]/UHPI_HD[2]/GP0[2] I/O IPU

R15 EMA_D[1]/MMCSD_DAT[1]/UHPI_HD[1]/GP0[1] I/O IPU

T13 EMA_D[0]/MMCSD_DAT[0]/UHPI_HD[0]/GP0[0]/ I/O IPU

BOOT[12]

P9 EMA_A[2]/MMCSD_CMD/UHPI_HCNTL1/GP1[2] I/O IPU UHPI access control

R9 EMA_A[1]/MMCSD_CLK/UHPI_HCNTL0/GP1[1] I/O IPU

P8 EMA_BA[1]/UHPI_HHWIL/GP1[13] I/O IPU UHPI half-word identification control

M13 EMA_WE/UHPI_HRW /AXR0[12]/GP2[3]/ I/O IPU UHPI read/write

BOOT[14]

P7 EMA_CS[2]/ UHPI_HCS /GP2[5]/BOOT[15] I/O IPU UHPI chip select

P12 EMA_WE_DQM[1]/ UHPI_HDS2 /AXR0[14]/ I/O IPU UHPI data strobe

GP2[8]

R7 EMA_OE/ UHPI_HDS1 /AXR0[13]/GP2[7] I/O IPU

M14 EMA_WE_DQM[0]/ UHPI_HINT /AXR0[15]/GP2[9] I/O IPU UHPI host interrupt

N6 EMA_WAIT[0]/ UHPI_HRDY /GP2[10] I/O IPU UHPI ready

T8 EMA_CS[0]/ UHPI_HAS /GP2[4] I/O IPU UHPI address strobe

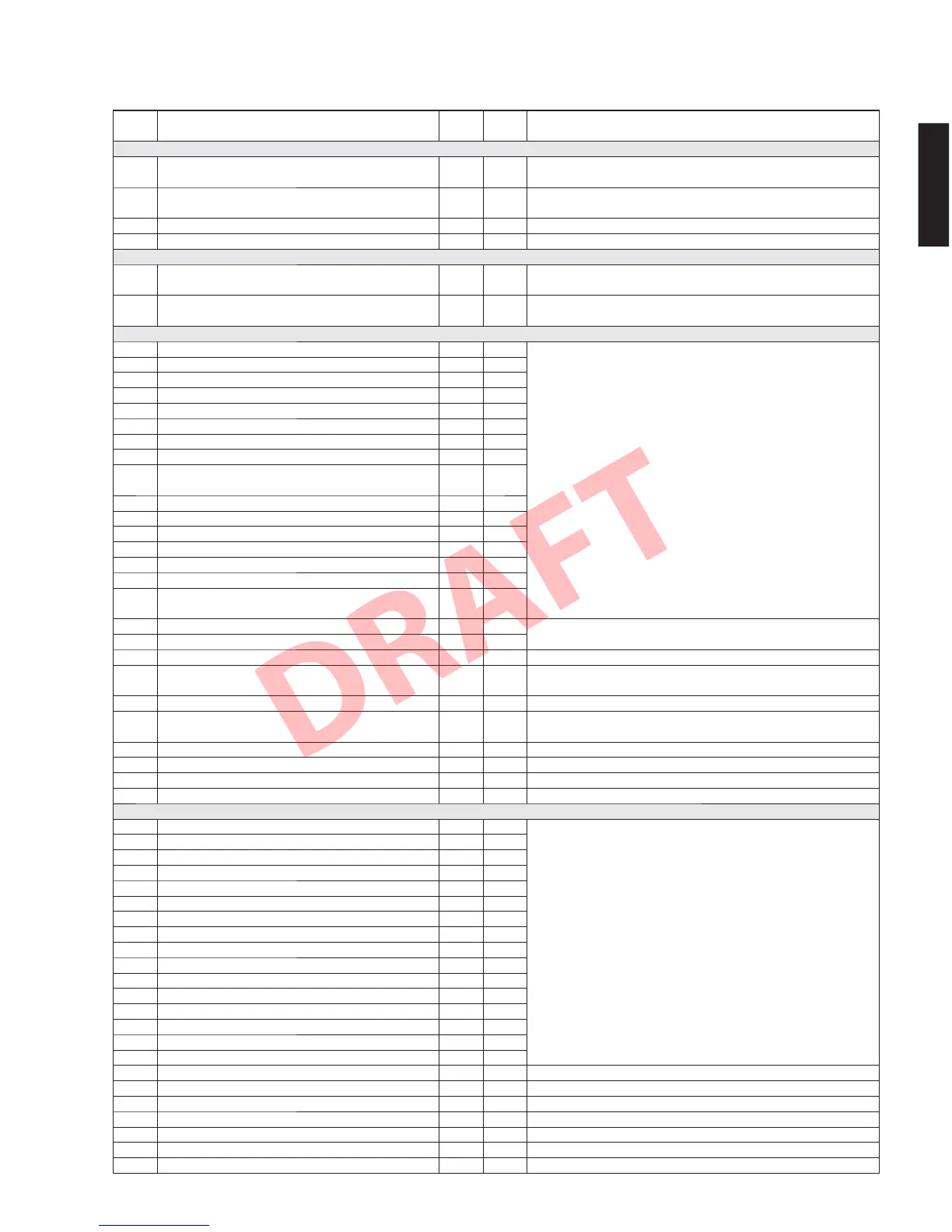

Multichannel Audio Serial Ports (McASP0, McASP1, McASP2)

M14 EMA_WE_DQM[0]/UHPI_HINT/AXR0[15]/GP2[9] I/O IPU McASP0 serial data

P12 EMA_WE_DQM[1]/UHPI_HDS2/AXR0[14]/GP2[8] I/O IPU

R7 EMA_OE/UHPI_HDS1/AXR0[13]/GP2[7] I/O IPU

M13

EMA_WE/UHPI_HRW/AXR0[12]/GP2[3]/BOOT[14]

I/O IPU

A5 AXR0[11]/ AXR2[0]/GP3[11] I/O IPD

D6 AXR0[10]/GP3[10] I/O IPD

C6 UART1_RXD/AXR0[9]/GP3[9] I/O IPD

B6 AXR0[8]/GP3[8] I/O IPU

A6 AXR0[7]/GP3[7] I/O IPD

D7 AXR0[6]/ACLKR2/GP3[6] I/O IPD

C7 AXR0[5]/AFSX2/GP3[5] I/O IPD

B7 AXR0[4]/ AXR2[1]/GP3[4] I/O IPD

A7 AXR0[3]/AXR2[2]/GP3[3] I/O IPD

D8 AXR0[2]/AXR2[3]/GP3[2] I/O IPD

C8 AXR0[1]/ACLKX2/GP3[1] I/O IPD

B8 AXR0[0]/AFSR2/GP3[0] I/O IPD

B5 AHCLKX0/AHCLKX2/USB_REFCLKIN/GP2[11] I/O IPD McASP0 transmit master clock

C5 ACLKX0/ECAP0/APWM0/GP2[12] I/O IPD McASP0 transmit bit clock

D5 AFSX0/GP2[13]/BOOT[10] I/O IPD McASP0 transmit frame sync

A4 AHCLKR0/GP2[14]/BOOT[11] I/O IPD McASP0 receive master clock

B4 ACLKR0/ECAP1/APWM1/GP2[15] I/O IPD McASP0 receive bit clock

C4 AFSR0/GP3[12] I/O IPD McASP0 receive frame sync

L4 AMUTE0/RESETOUT - O IPD McASP0 mute output

95

YSP-CU4300/YSP-CU3300/NS-WSW160

YSP-CU4300/YSP-CU3300/

NS-WSW160

Loading...

Loading...