eZ80

®

CPU

User Manual

UM007714-0908 CPU Instruction Set

270

OUT0 (n), r

Output to I/O

Operation

({UU, 00h, n}) ← r

Description

The

r

operand is any of A, B, C, D, E, H, or L. The

n

operand is placed on the lower byte

of the address bus, ADDR[7:0], while the High byte of the address bus, ADDR[15:8], is

forced to 0. The upper byte of the address bus, ADDR[23:16] is undefined for I/O

addresses. The CPU next outputs the contents of the

r

register to the I/O address {UU,

00h,

n

}.

Condition Bits Affected

None.

Attributes

jj identifies the A, B, C, D, E, H, or L register and is assembled into one of the opcodes

indicated in Table 77.

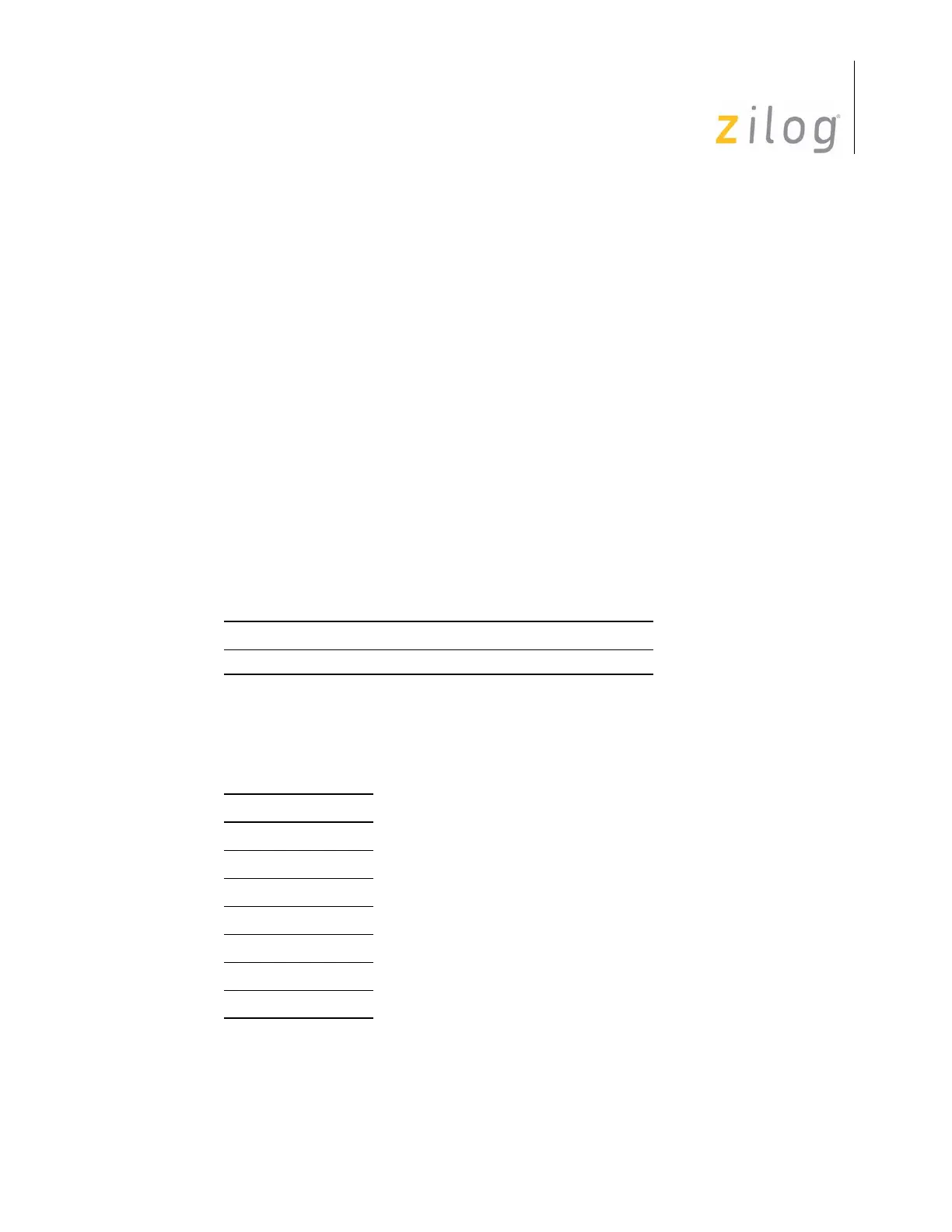

Mnemonic Operand ADL Mode Cycle Opcode (hex)

OUT0 (n),r X4ED, jj, nn

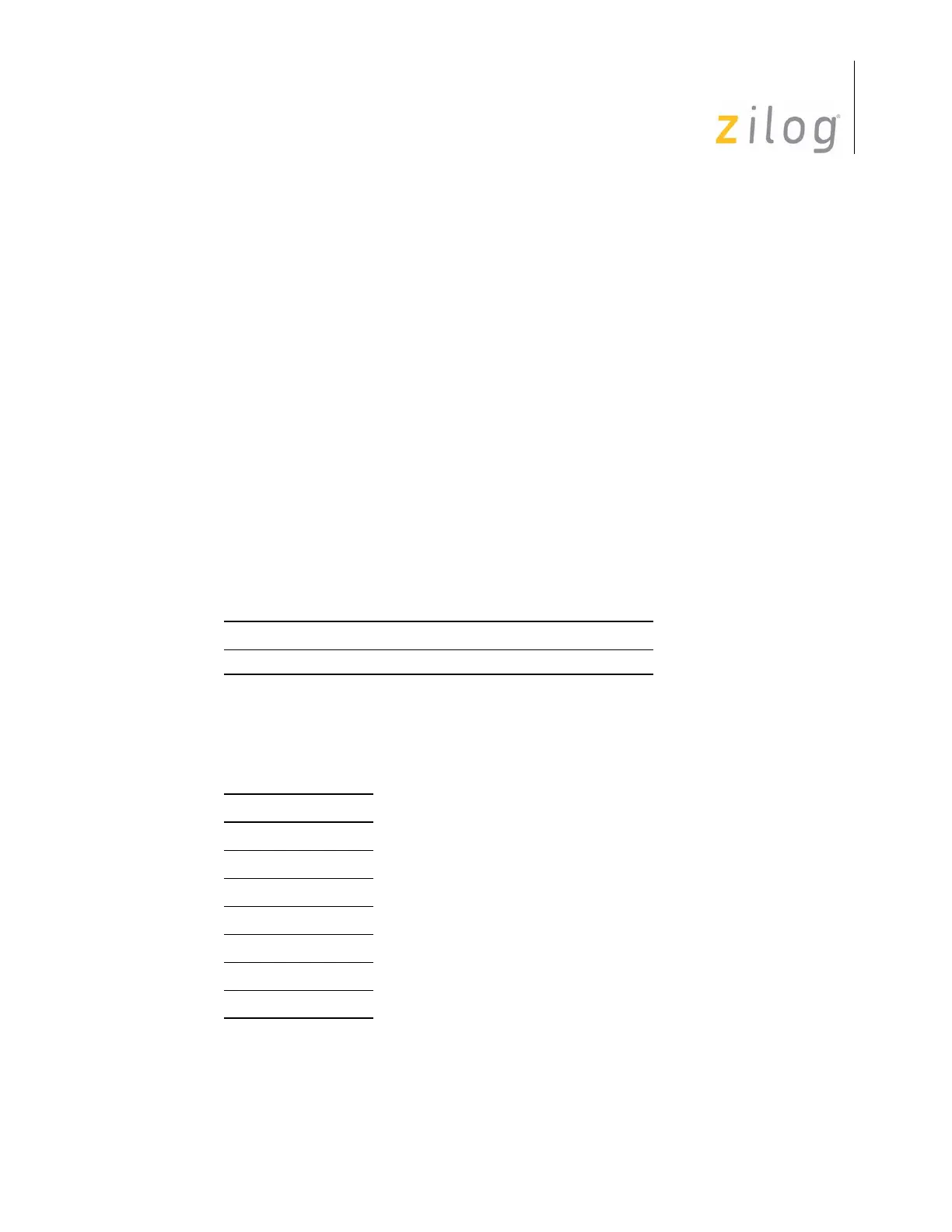

Table 77. Register and jj Opcodes for OUT0 (n), r Instruction (hex)

Register jj

A 39

B 01

C 09

D 11

E 19

H 21

L 29

Loading...

Loading...