Appendix

260

1SVC 440 795 M0100

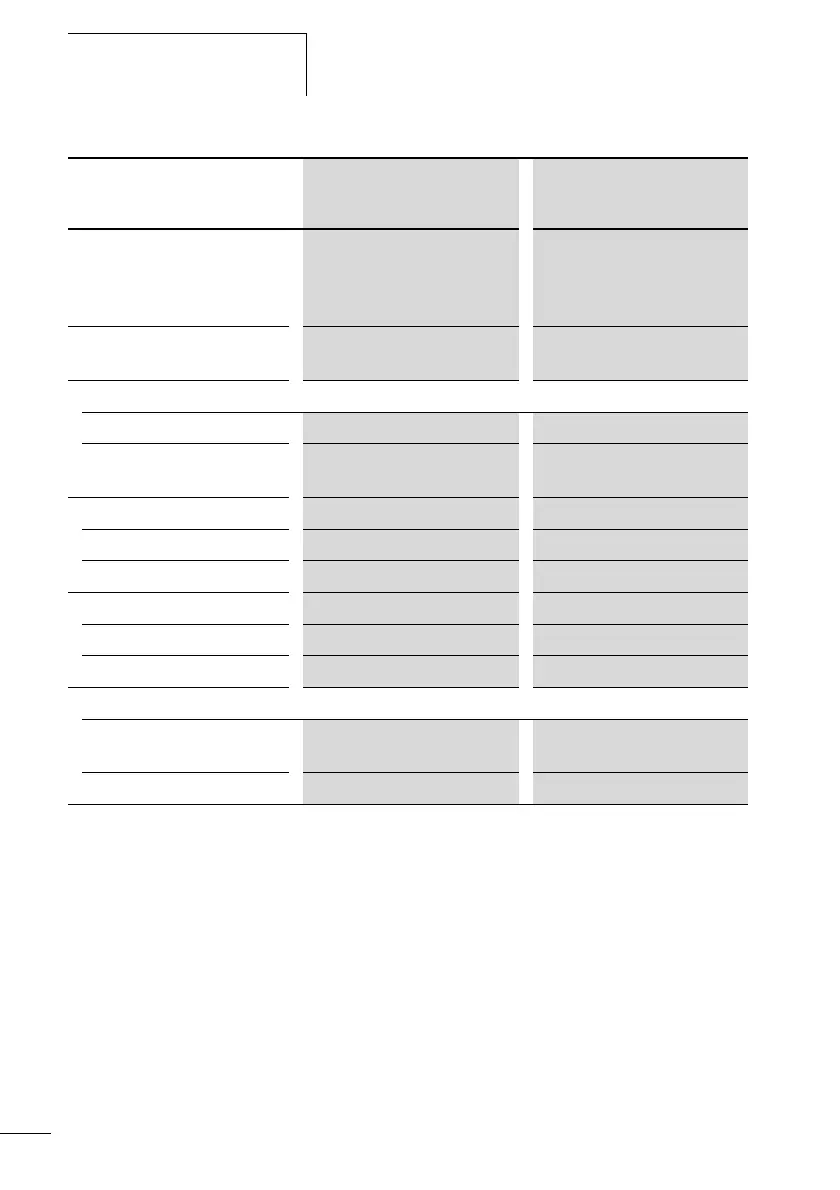

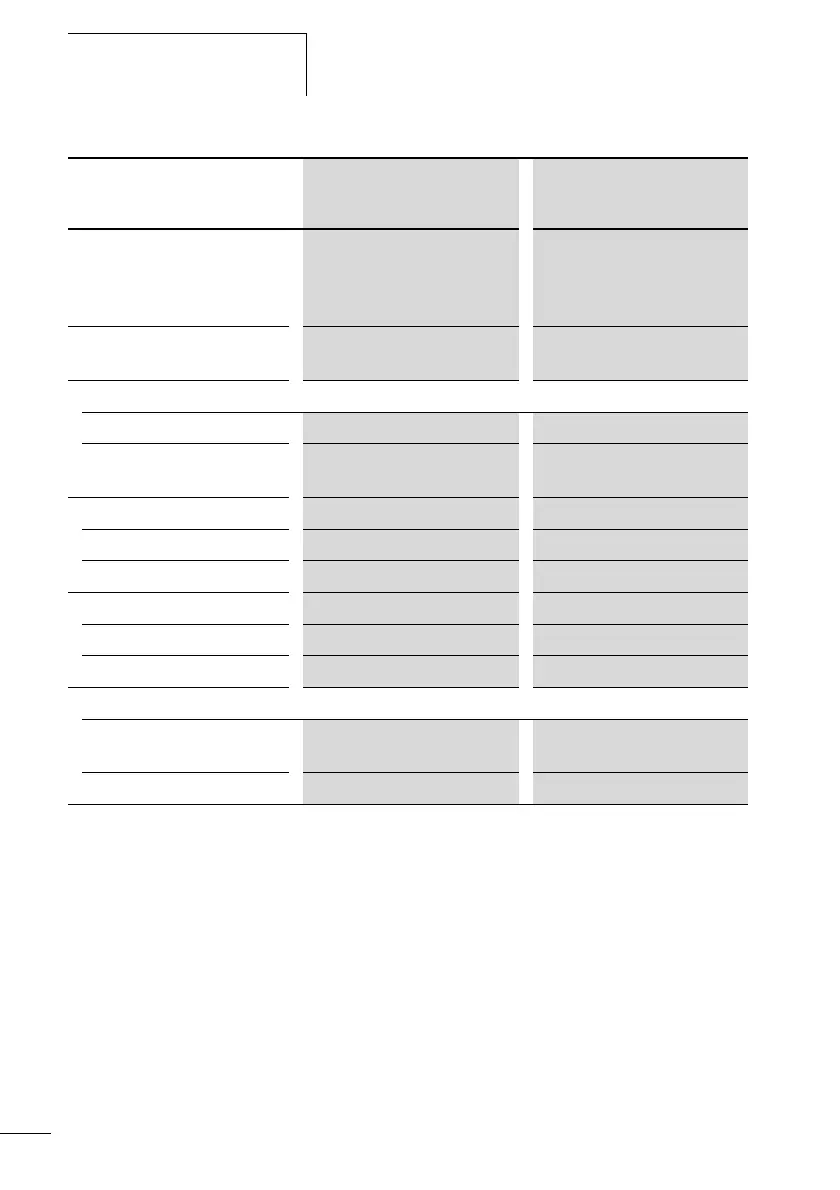

Input current for state „1“

R1 to R12, I1 to I6

(CL-LMR also I9 to I12)

6

x

0.5 mA at 230 V AC 50 Hz

6

x

0.25 mA at 115 V AC 60 Hz

10 (12) x 0.5 mA at

230 V AC 50 Hz

10 (12) x 0.25 mA at

115 V AC 60 Hz

Input current for state “1”

I7, I8

2 x 6 mA at 230 V AC 50 Hz,

2 x 4 mA at 115 V AC 60 Hz

2 x 6 mA at 230 V AC 50 Hz,

2 x 4 mA at 115 V AC 60 Hz

Delay time for 0 to 1 and 1 to 0 for I1 to I6, I9 to I12

Debounce ON 80 ms (50 Hz), 66B/c ms (60 Hz) 80 ms (50 Hz), 66B/c ms (60 Hz)

Debounce OFF

(also R1 to R12)

20 ms (50 Hz), 16B/c ms (60 Hz) 20 ms (50 Hz), 16B/c ms (60 Hz)

Delay time I7, I8 for 1 to 0

Debounce ON 160 ms (50 Hz), 150 ms (60 Hz) 80 ms (50 Hz),66B/c ms (60 Hz)

Debounce OFF 100 ms (50 Hz/60 Hz) 20 ms (50 Hz), 16B/c ms (60 Hz)

Delay time I7, I8 for 0 to 1

Debounce ON 80 ms (50 Hz), 66B/c ms (60 Hz) 80 ms (50 Hz), 66B/c ms (60 Hz)

Debounce OFF 20 ms (50 Hz), 16B/c ms (60 Hz) 20 ms (50 Hz), 16B/c ms (60 Hz)

Max. permissible cable length (per input)

I1 to I6, R1 to R12

(CL-LMR also I9 to I12)

Normally 40 m Normally 40 m

I7, I8 Normally 100 m Normally 100 m

CL-LSR...AC2 CL-LER.18AC2,

CL-LMR...AC2

Loading...

Loading...