Publication 1762-RM001C-EN-P

13-4 Move Instructions

•

Valid constants for the mask are -32768 to 32767 (word) and

-2,147,483,648 to 2,147,483,647 (long word). The mask is displayed as

a hexadecimal unsigned value from 0000 0000 to FFFF FFFF.

Addressing Modes and File Types can be used as shown in the following

table:

Updates to Math Status Bits

After a MVM instruction is executed, the arithmetic status bits in the status

file are updated. The arithmetic status bits are in word 0 bits 0-3 in the

processor status file (S2).

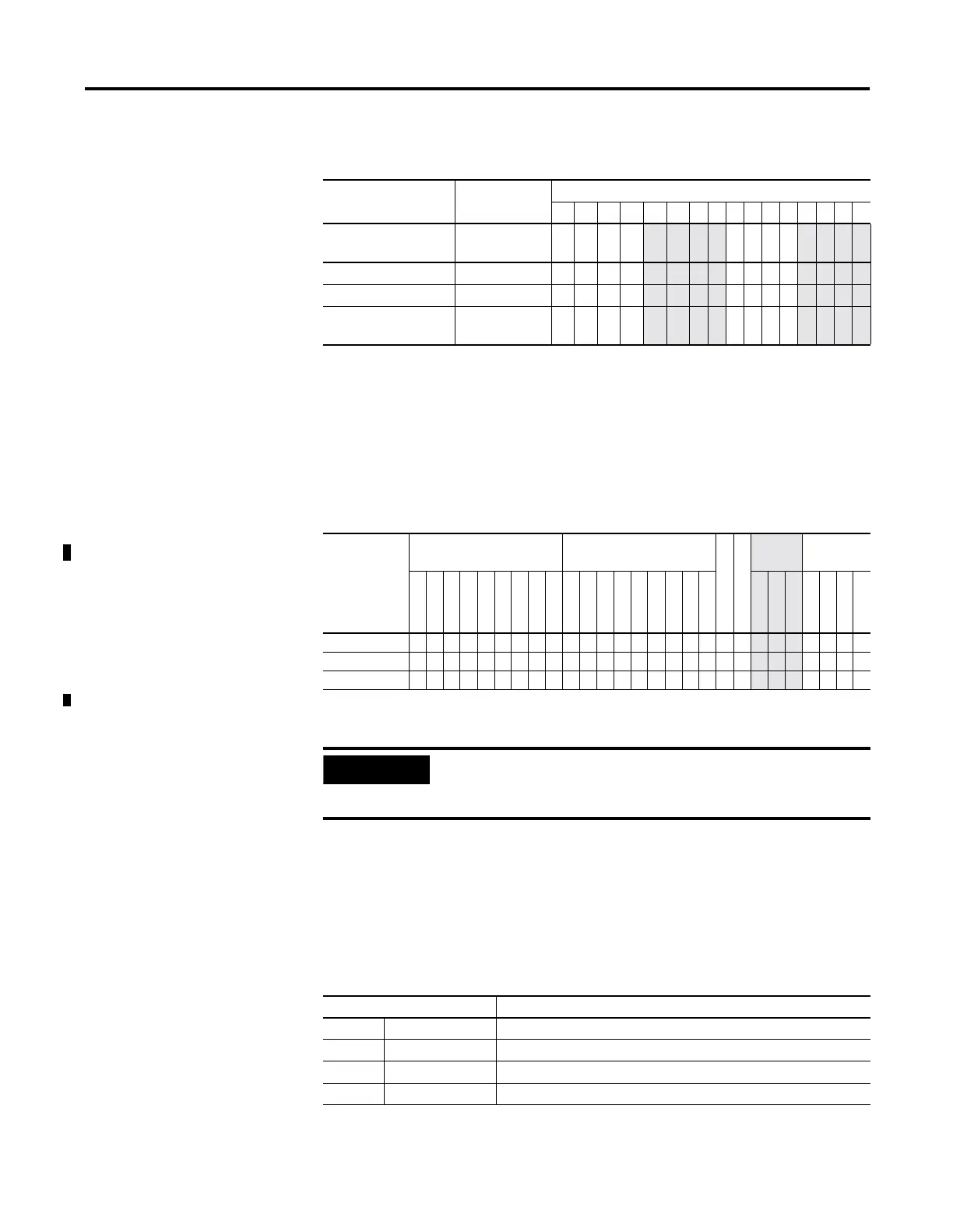

Table 13.6 Mask Example (Word Addressing Level)

Word Value in

Hexadecimal

Value in Binary

1514131211109876543210

Value in Destination

Before Move

FFFF 1111

1 1 1 1 11111 1 1 1

Source Value 5555 0 1 0 1 0 1 0 101010 1 0 1

Mask F0F0 1111

0 0 0 0 11110 0 0 0

Value in Destination

After Move

5F5F 0 1 0 1

1 1 1 1 01011 1 1 1

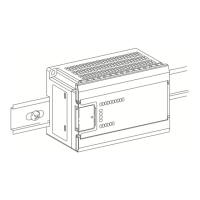

Table 13.7 MVM Instruction Valid Addressing Modes and File Types

For definitions of the terms used in this table see Using the Instruction Descriptions on page 4-2.

Parameter

Data Files

(1)

(1) The ST file is not valid for MicroLogix 1500 1764-LSP Series A processors.

Function Files

CS - Comms

IOS - I/O

Address

Mode

(2)

(2) See Important note about indirect addressing.

Address

Level

O

I

S

B

T, C, R

N

ST

L

MG, PD

RTC

HSC

PTO, PWM

STI

EII

BHI

MMI

DAT

TPI

Immediate

Direct

Indirect

Bit

Word

Long Word

Element

Source •• ••••• • •••

Mask •• •••••

• • •••

Destination •• •••••

• •••

IMPORTANT

You cannot use indirect addressing with: S, ST, MG, PD, RTC,

HSC, P TO , PWM, STI, E I I, BHI, MMI, D AT, T P I, CS, IOS , and

DLS files.

Table 13.8 Math Status Bits

With this Bit: The Controller:

S:0/0 Carry always resets

S:0/1 Overflow always resets

S:0/2 Zero Bit sets if destination is zero, otherwise resets

S:0/3 Sign Bit sets if the MSB of the destination is set, otherwise resets

Loading...

Loading...