43

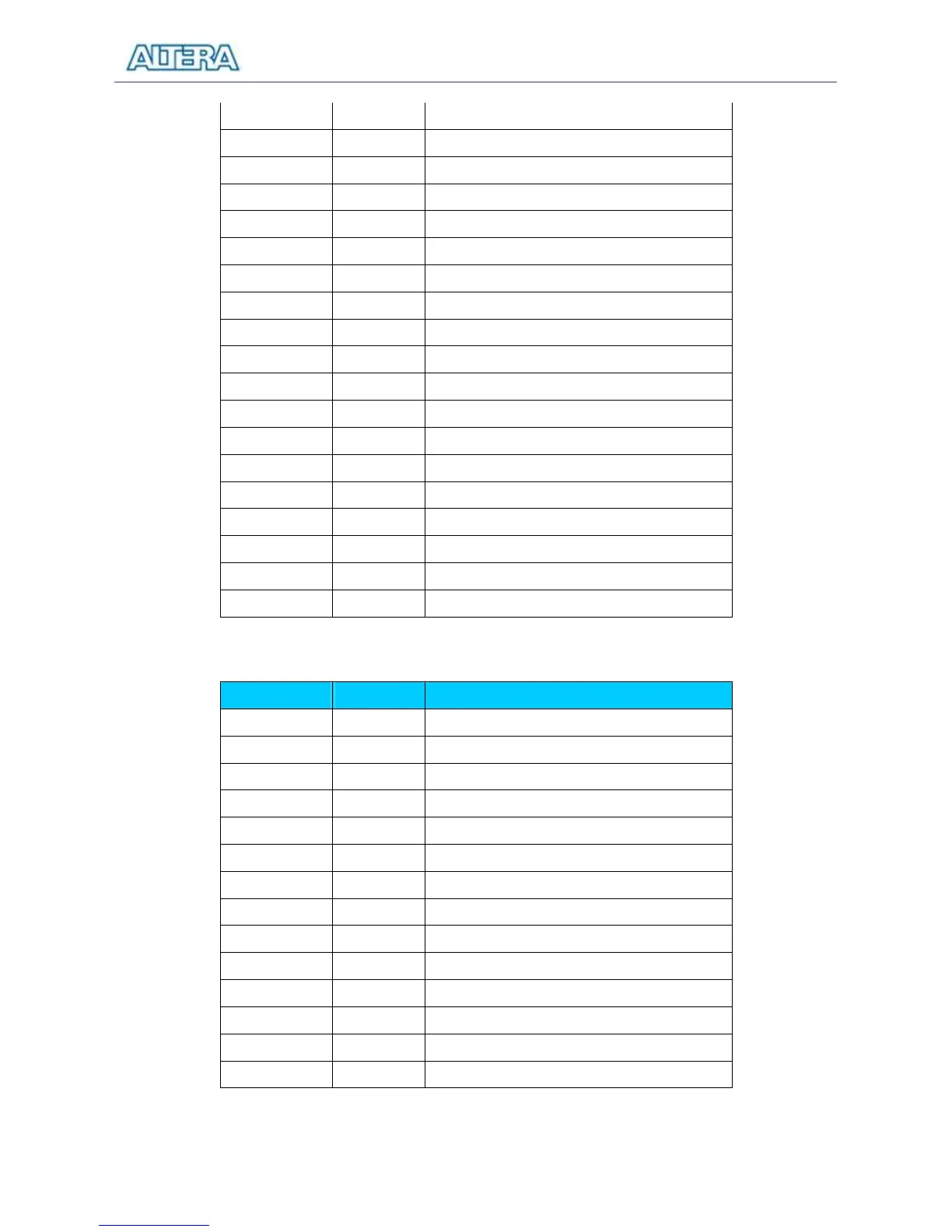

DRAM_DQ[7] PIN_Y2 SDRAM Data[7]

DRAM_DQ[8] PIN_N1 SDRAM Data[8]

DRAM_DQ[9] PIN_N2 SDRAM Data[9]

DRAM_DQ[10] PIN_P1 SDRAM Data[10]

DRAM_DQ[11] PIN_P2 SDRAM Data[11]

DRAM_DQ[12] PIN_R1 SDRAM Data[12]

DRAM_DQ[13] PIN_R2 SDRAM Data[13]

DRAM_DQ[14] PIN_T1 SDRAM Data[14]

DRAM_DQ[15] PIN_T2 SDRAM Data[15]

DRAM_BA_0 PIN_U3 SDRAM Bank Address[0]

DRAM_BA_1 PIN_V4 SDRAM Bank Address[1]

DRAM_LDQM PIN_R7 SDRAM Low-byte Data Mask

DRAM_UDQM PIN_M5 SDRAM High-byte Data Mask

DRAM_RAS_N PIN_T5 SDRAM Row Address Strobe

DRAM_CAS_N PIN_T3 SDRAM Column Address Strobe

DRAM_CKE PIN_N3 SDRAM Clock Enable

DRAM_CLK PIN_U4 SDRAM Clock

DRAM_WE_N PIN_R8 SDRAM Write Enable

DRAM_CS_N PIN_T6 SDRAM Chip Select

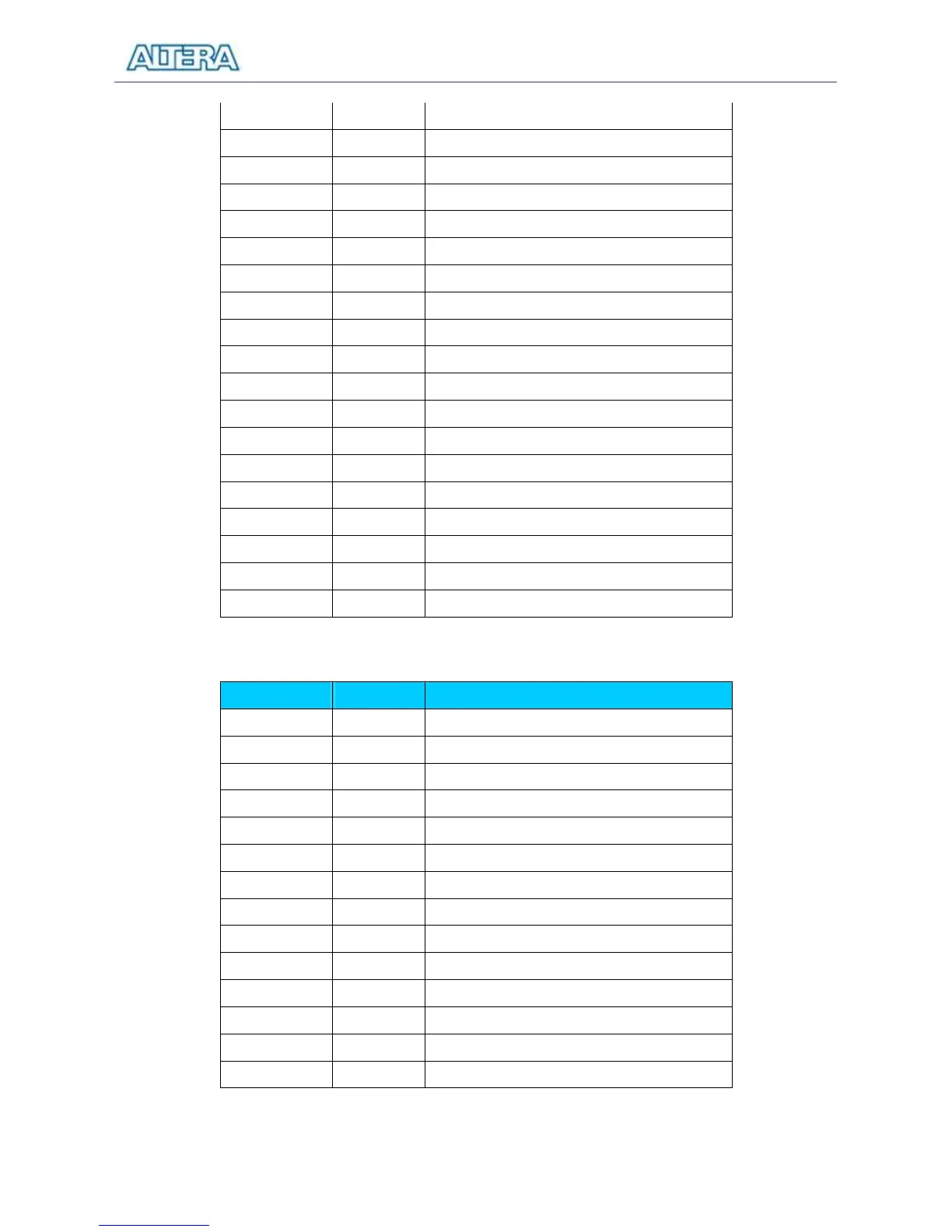

Table 4.16. SDRAM pin assignments.

Signal Name FPGA Pin No.

Loading...

Loading...