Chapter 3 Hardware

CoreModule 420 Reference Manual 27

IDE Interface (J6)

The IDE device signals are provided through the standard 44-pin, 2mm connector (J6).

The IDE interface supports the following features:

• Master mode PCI supporting Enhanced IDE devices

• Supports two EIDE devices

• Full scatter-gather capability

• Supports ATAPI compliant devices including DVD

• Supports IDE native and ATA compatibility modes

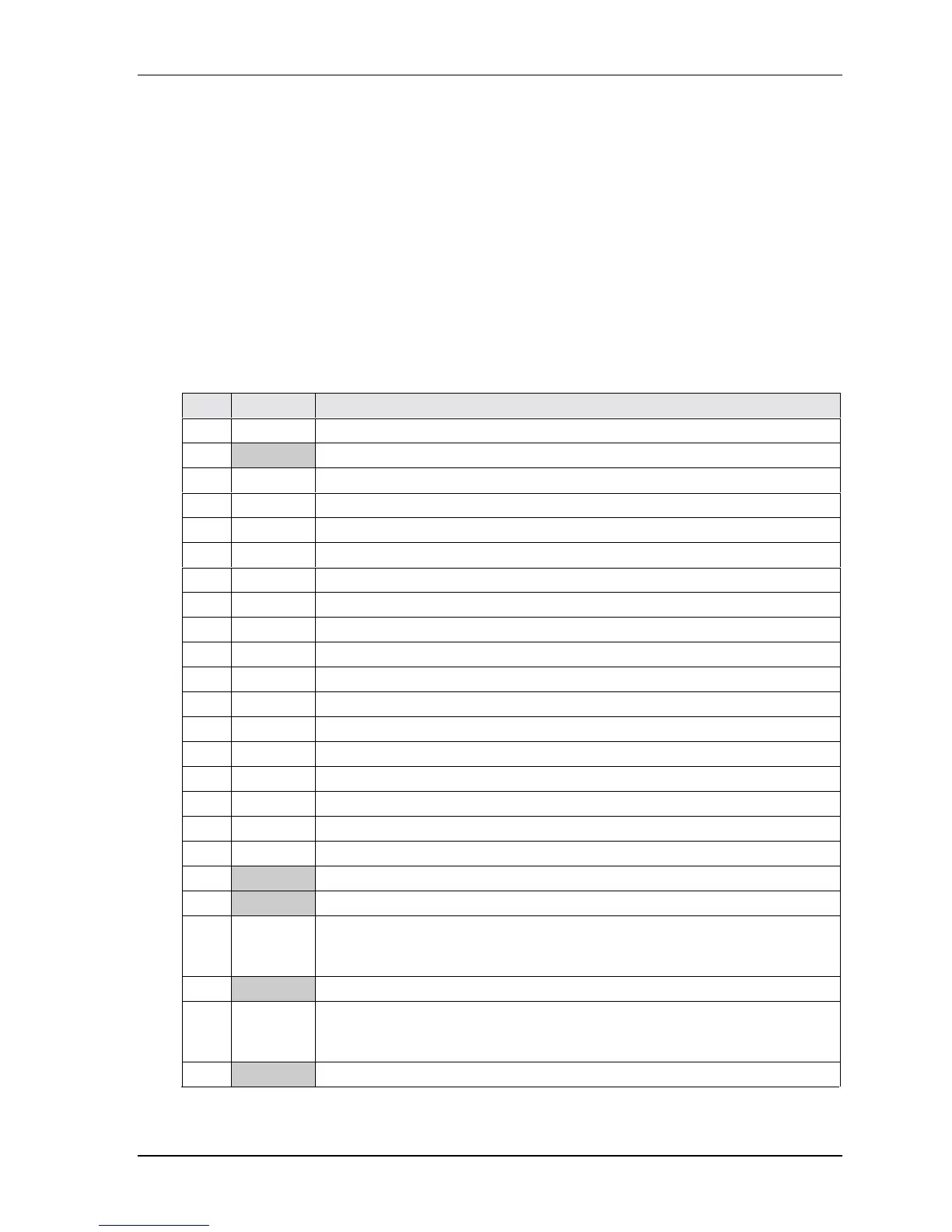

Table 3-9 gives the signals for the 44-pins of the IDE 2mm header.

Table 3-9. IDE Interface Pin/Signal Descriptions (J6)

Pin # Signal Description

1 RESET* Low active hardware reset (RSTDRV inverted)

2 GND Digital Ground

3 D7 Disk Data 7– These pins (0 to 15) provide disk data.

4 D8 Disk Data 8 – Refer to pin 3, D7, for more information.

5 D6 Disk Data 6– Refer to pin 3, D7, for more information.

6 D9 Disk Data 9 – Refer to pin 3, D7, for more information.

7 D5 Disk Data 5– Refer to pin 3, D7, for more information.

8 D10 Disk Data 10– Refer to pin 3, D7, for more information.

9 D4 Disk Data 4 – Refer to pin 3, D7, for more information.

10 D11 Disk Data 11 – Refer to pin 3, D7, for more information.

11 D3 Disk Data 3 – Refer to pin 3, D7, for more information.

12 D12 Disk Data 12 – Refer to pin 3, D7, for more information.

13 D2 Disk Data 2 – Refer to pin 3, D7, for more information.

14 D13 Disk Data 13 – Refer to pin 3, D7, for more information.

15 D1 Disk Data 1 – Refer to pin 3, D7, for more information.

16 D14 Disk Data 14– Refer to pin 3, D7, for more information.

17 D0 Disk Data 0 – Refer to pin 3, D7, for more information.

18 D15 Disk Data 15 – Refer to pin 3, D7, for more information.

19 GND Digital Ground

20 Key/GND Key pin plug/Ground

21 PDRQ

DMA Request – Used for DMA transfers between host and drive (direction of

transfer controlled by PIOR* and PIOW*). Also used in an asynchronous mode

with PDACK*. Drive asserts PIRQ when ready to transfer or receive data.

22 GND Digital Ground

23 PIOW* Drive I/O Write – Strobe signal for write functions. Negative edge enables data

from a register or data port of the drive onto the host data bus. Positive edge

latches data at the host.

24 GND Digital Ground

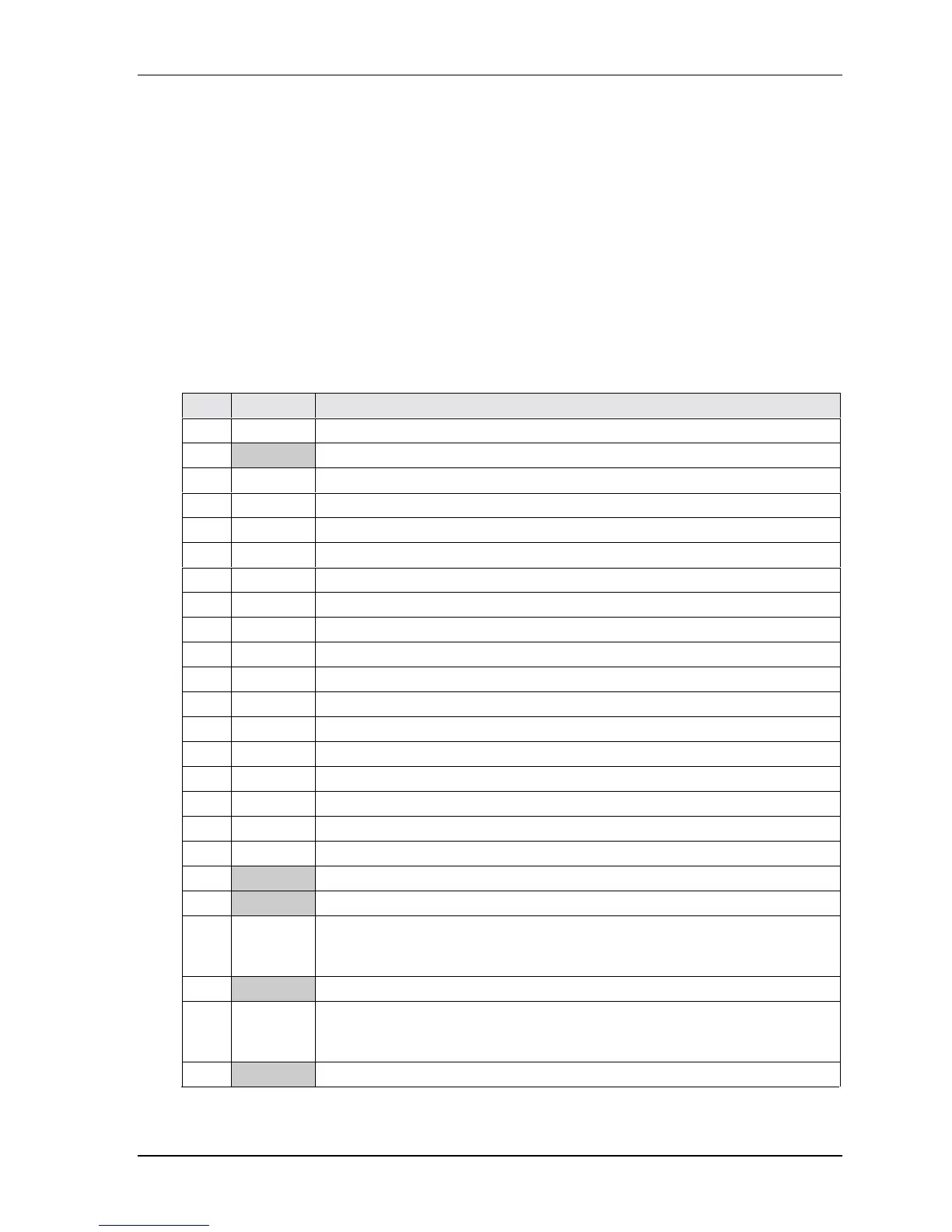

Loading...

Loading...