Do you have a question about the Atmel 8051 and is the answer not in the manual?

Details the Program Status Word (PSW) register, its bits, and their functions.

Describes the various addressing modes used by the 8051 instruction set.

Lists and explains the arithmetic instructions available on the 8051.

Details the bitwise logical operations performed by the 8051 instruction set.

Covers instructions for moving data between registers and memory.

Details instructions for accessing external data memory.

Describes instructions for reading data from program memory tables.

Covers the 8051's single-bit processor and its instructions.

Explains instructions that alter program flow, including jumps and calls.

Explains instructions that read, modify, and write back data.

Provides a comprehensive list of 8051 instructions with byte and cycle counts.

Lists instructions that modify the status flags in the PSW register.

Presents a table of 8051 instructions with hex values and execution times.

Provides detailed descriptions and operation of individual 8051 instructions.

Introduces the chapter on on-chip hardware features of 8051 microcontrollers.

Details the Special Function Register (SFR) map and key registers.

Explains the on-chip oscillator and clock generation system.

Details the CPU's fetch/execute cycles and timing characteristics.

Details the structure and operation of the 8051's I/O ports.

Explains accessing external program and data memory via 8051 pins.

Explains the Address Latch Enable (ALE) signal for address multiplexing.

Introduces the two general-purpose 16-bit timers/counters in the 80C51.

Details the four operating modes of Timer 0.

Details Timer 1's operation, similar to Timer 0 but with mode 3 differences.

Details Timer 2 features: capture, auto-reload, and baud rate generation.

Describes the Universal Asynchronous Receiver/Transmitter (UART) features.

Explains the feature for detecting framing errors in asynchronous serial modes.

Describes hardware feature for multiprocessor communication address matching.

Covers interrupt handling, priority levels, and response times.

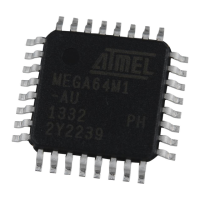

| Architecture | 8-bit |

|---|---|

| Serial Communication | UART |

| CPU | 8051 |

| Program Memory | Up to 64 KB Flash |

| Timers/Counters | 2 or 3 (16-bit) |

| SPI | Yes |

| I2C | Yes |

| ADC | Yes (some variants) |

| Operating Voltage | 2.7V to 5.5V |

| Operating Temperature | -40°C to +85°C |

| Package | DIP, PLCC, TQFP |