48

ATtiny15L

1187H–AVR–09/07

channel must be selected before entering Free Running mode. Selecting an active

channel after entering Free Running mode may result in undefined operation from the

ADC.

• Bit 4 – ADIF: ADC Interrupt Flag

This bit is set (one) when an ADC conversion completes and the Data Registers are

updated. The ADC Conversion Complete Interrupt is executed if the ADIE bit and the I-

bit in SREG are set (one). ADIF is cleared by hardware when executing the correspond-

ing interrupt handling vector. Alternatively, ADIF is cleared by writing a logical “1” to the

flag. Beware that if doing a read-modify-write on ADCSR, a pending interrupt can be dis-

abled. This also applies if the SBI and CBI instructions are used.

• Bit 3 – ADIE: ADC Interrupt Enable

When this bit is set (one) and the I-bit in SREG is set (one), the ADC Conversion Com-

plete Interrupt is activated.

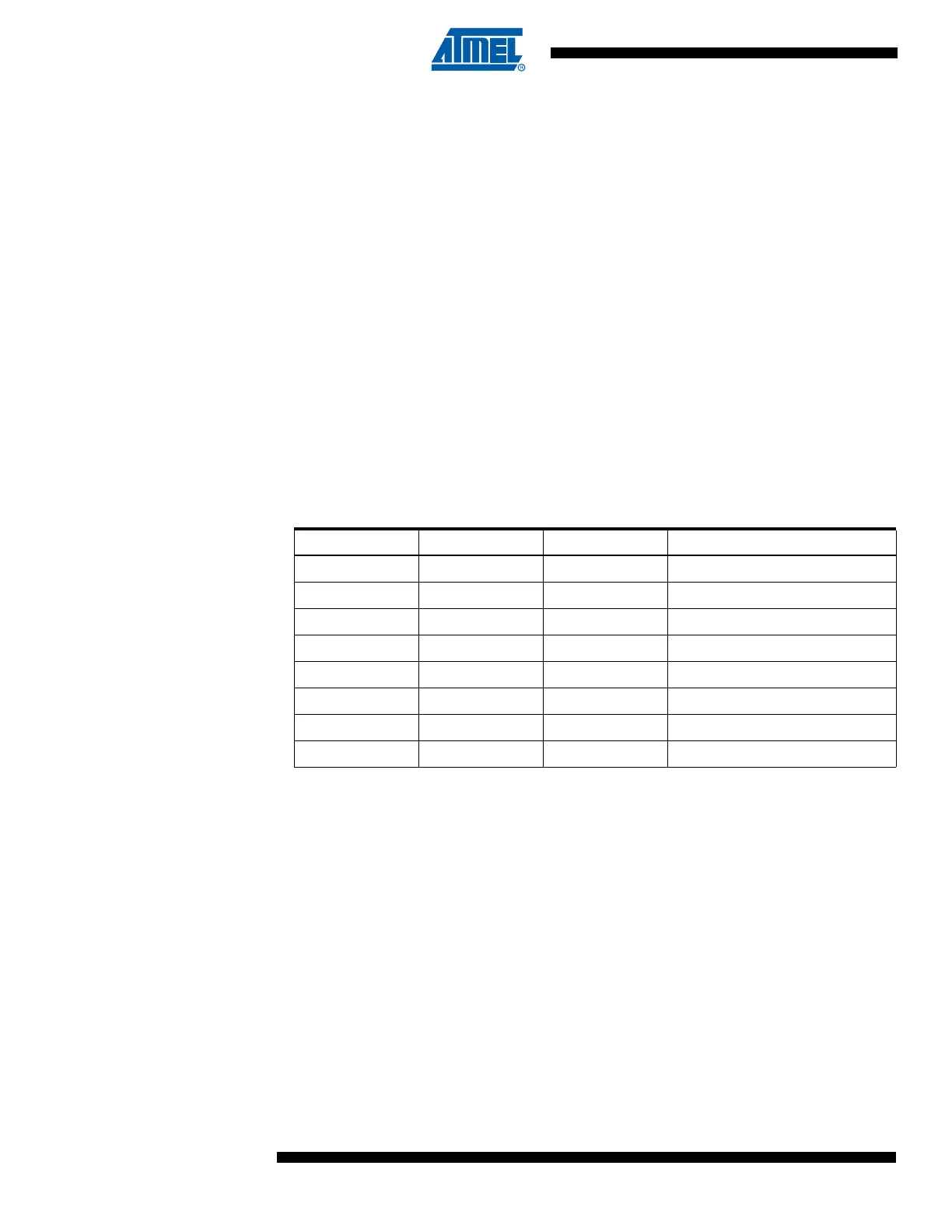

• Bits 2..0 – ADPS2..ADPS0: ADC Prescaler Select Bits

These bits determine the division factor between the CK frequency and the input clock

to the ADC. See Table 21.

Table 21. ADC Prescaler Selections

ADPS2 ADPS1 ADPS0 Division Factor

000 2

001 2

010 4

011 8

100 16

101 32

110 64

1 1 1 128

Loading...

Loading...