6

8068C–AVR–06/08

XMEGA A3

6. AVR CPU

6.1 Features

• 8/16-bit high performance AVR RISC Architecture

– 138 instructions

– Hardware multiplier

• 32x8-bit registers directly connected to the ALU

• Stack in RAM

• Stack Pointer accessible in I/O memory space

• Direct addressing of up to 16M bytes of program and data memory

• True 16/24-bit access to 16/24-bit I/O registers

• Support for 8-, 16- and 32-bit Arithmetic

• Configuration Change Protection of system critical features

6.2 Overview

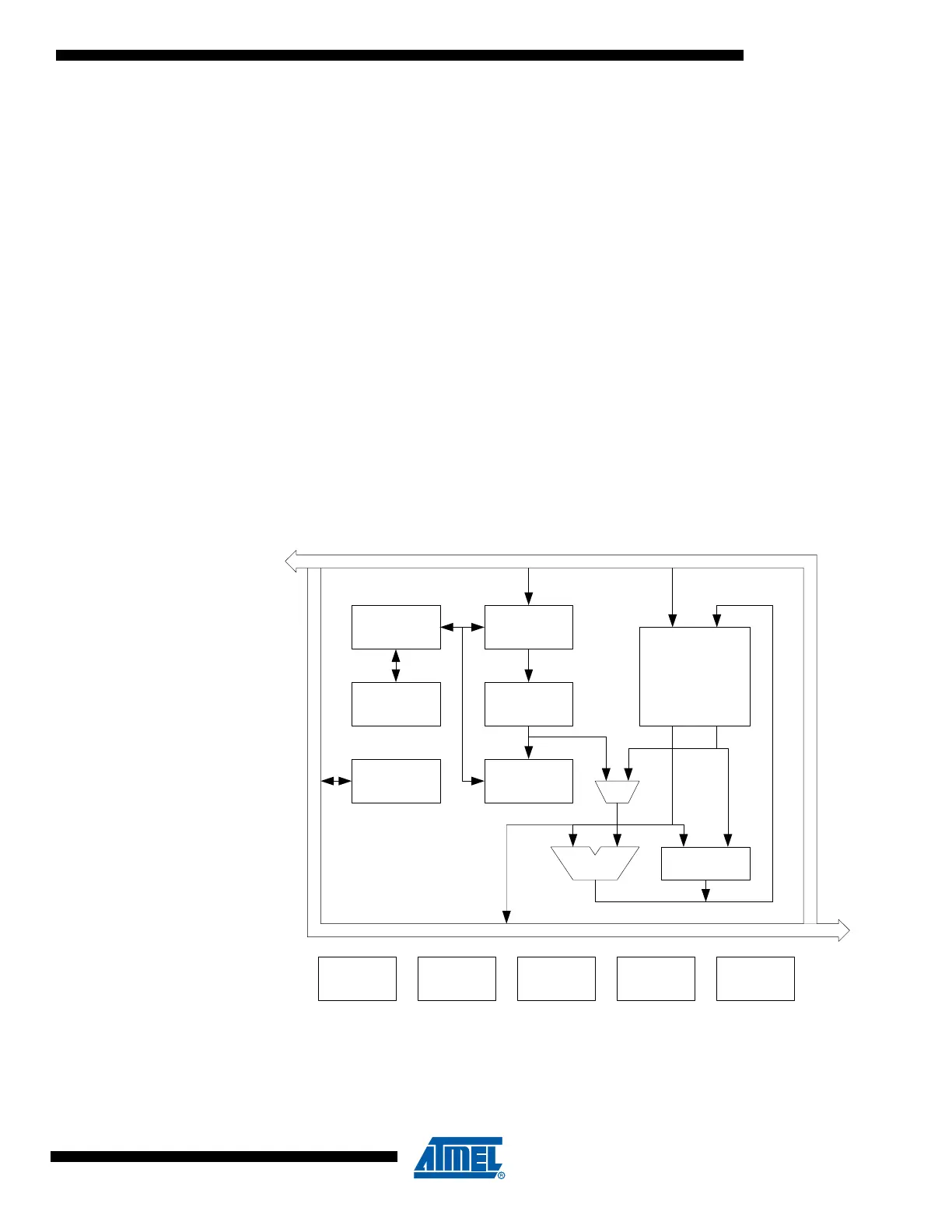

The XMEGA A3 uses an 8/16-bit AVR CPU. The main function of the AVR CPU is to ensure cor-

rect program execution. The CPU must therefore be able to access memories, perform

calculations and control peripherals. Interrupt handling is described in a separate section. Figure

6-1 on page 6 shows the CPU block diagram.

Figure 6-1. CPU block diagram

The AVR uses a Harvard architecture - with separate memories and buses for program and

data. Instructions in the program memory are executed with a single level pipeline. While one

instruction is being executed, the next instruction is pre-fetched from the program memory.

Flash

Program

Memory

Instruction

Decode

Program

Counter

OCD

32 x 8 General

Purpose

Registers

ALU

Multiplier/

DES

Instruction

Register

STATUS/

CONTROL

Peripheral

Module 1

Peripheral

Module 2

EEPROM PMICSRAM

DATA BUS

DATA BUS

Loading...

Loading...