5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

(Default)

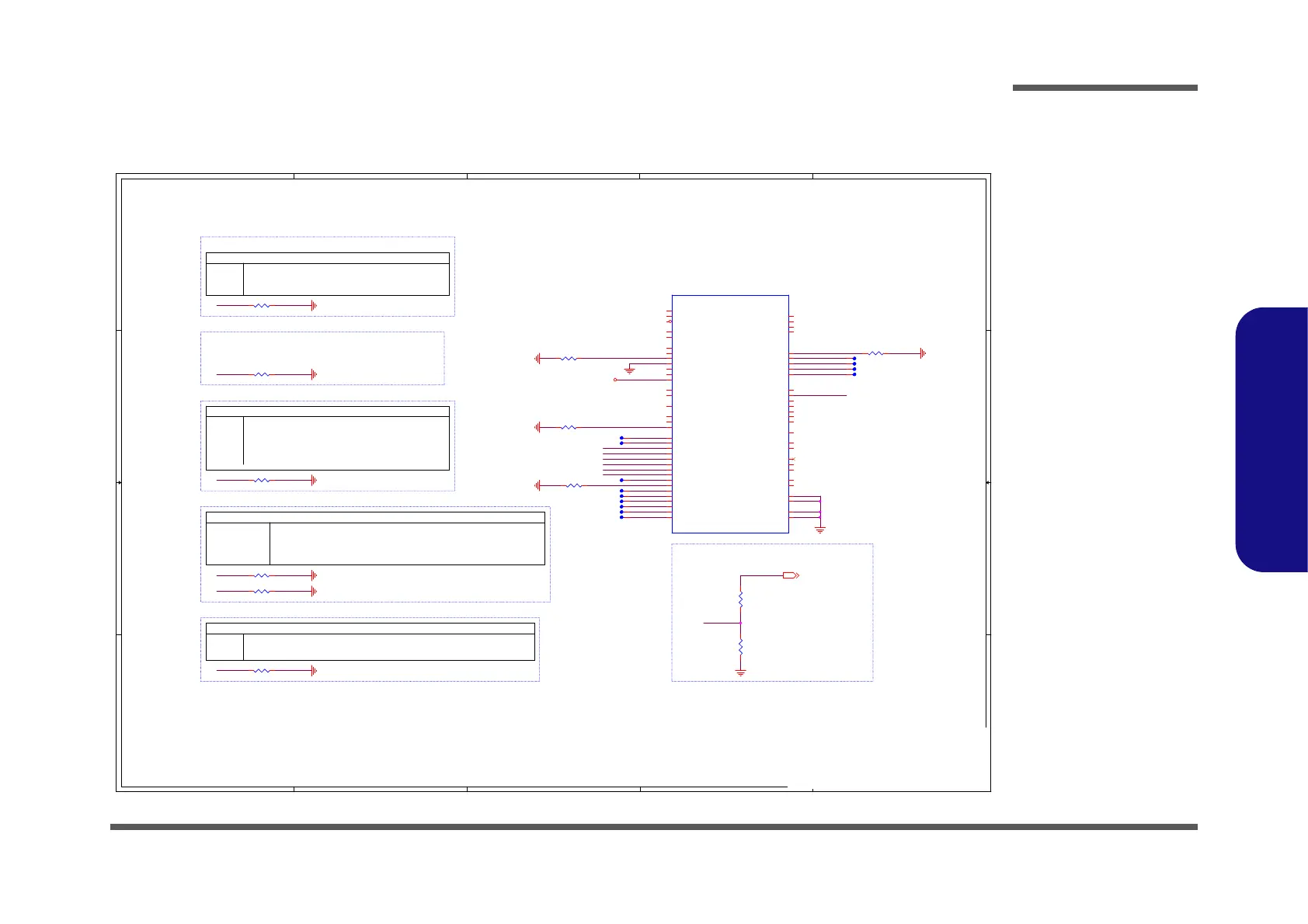

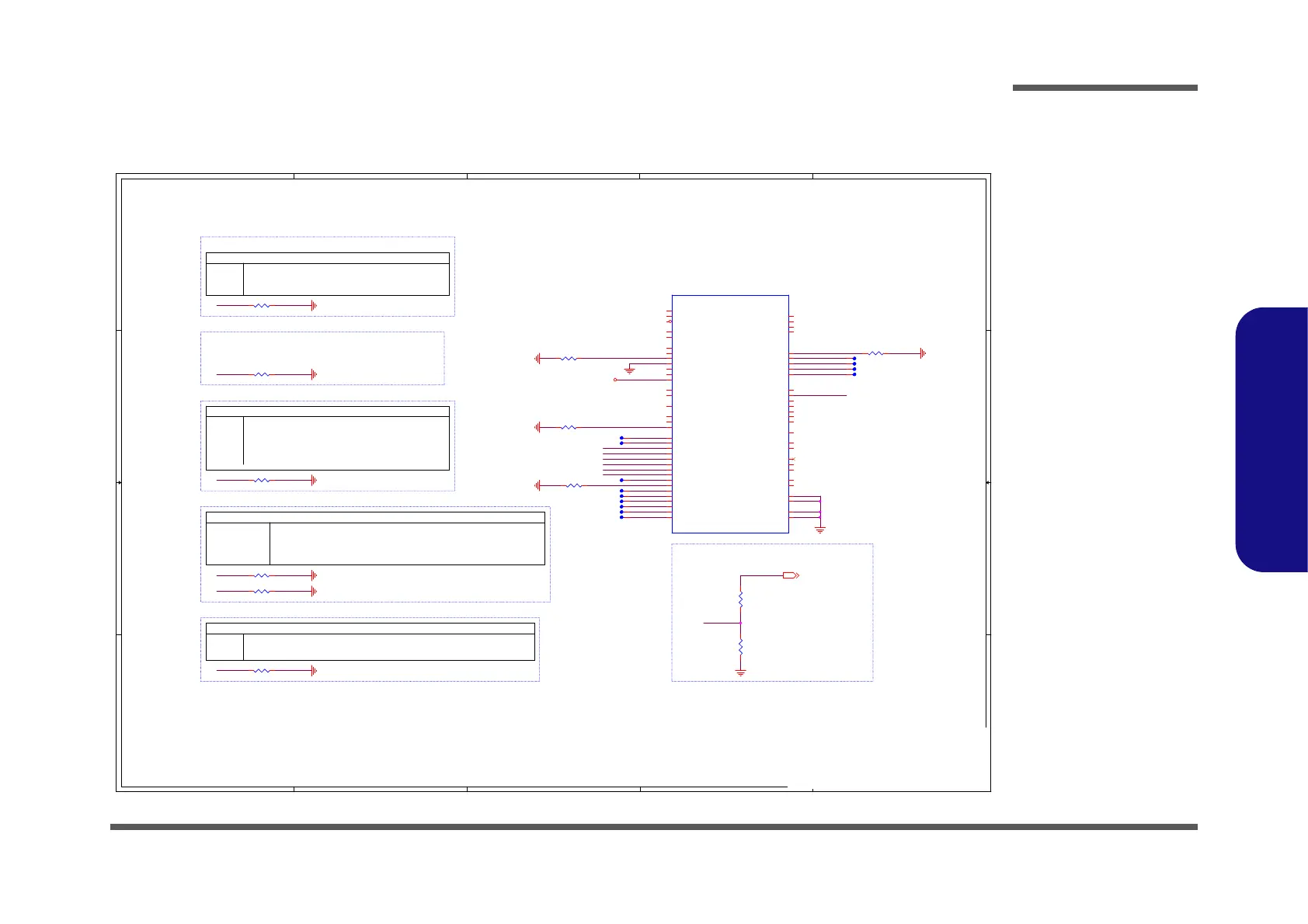

Haswell Processor 7/7 ( RESERVED )

CFG7

DEFENSIVE PULL DOWN SITE

1: (Default) PEG Train immediately following xxRESETB de assertion

0: PEG Wait for BIOS for training

(Default)

CFG2

1: (DEFAULT)NORMAL OPERATION;

LANE# DEFINITION MATCHES

0: LANE REVERSAL

PCI EXPRESS STATIC LANE REVERSAL FOR ALL PEG PORTS

CFG[6:5]

11: DEVICE1 FUNTION 1, DEVICE 1 FUNCTION2 DISABLED

10: DEVICE1 FUNCTION1 ENABLED DEVICE1 FUNCTION 2 DISABLED

01: DEVICE 1 FUNCTION 1 DISABLED, DEVICE 1 FUNCTION 2 ENABLED

00: DEVICE 1 FUNCTION 1 ENABLED, DEVICE 1 FUNCTION 2 ENABLED

PCIE Port Bifurcation Straps

CFG Straps for Processor

CFG4

1: DISABLED;

NO PHYSICAL DISPLAY PORT ATTACHED

TO EMBEDDED DISPLAY PORT

0: ENABLED; AN EXTERNAL DISPLAY PORT DEVICE

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

DISPLAY PORT PRESENCE STRAP

NOTE:

RESERVE THIS CIRCUIT FOR FUTURE COMPATIBILITY

NOTE:

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

0 : ENABLED SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

1 : DISABLED

FC_G6

CFG7

H_CPU_RSVD40

CFG3

CFG2

CFG4

CFG5

CFG7

CFG6

CFG16

CFG17

CFG18

CFG19

CFG2

CFG4

CFG5

CFG6

CFG0

CFG1

CFG_RCOMP

FC_G6

H_CPU_RSVD30

CFG3

CFG9

CFG10

CFG8

CFG11

CFG12

CFG13

CFG14

CFG15

+VCCIN

PM_PWROK 17,30

Title

Size Document Number Rev

Date: Sheet

of

6-71-W2W50-D02

2.0

[08] Haswell Processor 7/7

A3

844Friday, October 25, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: Sheet

of

6-71-W2W50-D02

2.0

[08] Haswell Processor 7/7

A3

844Friday, October 25, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: Sheet

of

6-71-W2W50-D02

2.0

[08] Haswell Processor 7/7

A3

844Friday, October 25, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Haswell rPGA EDS

9 OF 9

U25I

RSVD

P10

RSVD

U10

NC

B1

VSS

AR26

VSS

AP27

RSVD_TP

E20

RSVD_TP

E21

RSVD

A2

RSVD

E18

RSVD_TP

AR1

RSVD

K6

RSVD

AM2

RSVD

F5

RSVD

AM26

RSVD

AM27

CFG_19

AP23

CFG_17

AP21

CFG_18

AR23

CFG_16

AR21

CFG_RCOMP

AT31

RSVD_TP

D23

RSVD_TP

D24

RSVD_TP

B23

RSVD_TP

C23

CFG_15

AP25

CFG_14

AN26

CFG_13

AN25

CFG_9

AT23

CFG_8

AR24

CFG_7

AN23

CFG_6

AT25

RSVD_TP

B35

RSVD_TP

C35

VCC

F25

RSVD

AL29

RSVD

AL30

RSVD

W33

RSVD_TP

A35

RSVD_TP

A34

RSVD

AD10

RSVD_TP

AT2

RSVD_TP

AT1

CFG_12

AP26

CFG_11

AP24

CFG_10

AN20

RSVD_TP

W29

RSVD_TP

W28

TESTLO

G26

RSVD

AR33

FC

G6

RSVD_TP

AL25

RSVD_TP

W30

RSVD_TP

W31

TESTLO

W34

CFG_0

AT20

CFG_1

AR20

CFG_4

AT22

CFG_5

AN22

CFG_3

AP22

CFG_2

AP20

VSS

AL31

VSS

AL32

R141 *1K_04

R99

*1K_1%_04

R420 *1K_04

R419 1K_04

R100 49.9_1%_04

R432 49.9_1%_04

R140 *1K_04

R117 49.9_1%_04

R98

*2K_1%_04

R421 *1K_1%_04

R155 *1K_04

R146 *1K_04

Loading...

Loading...