5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

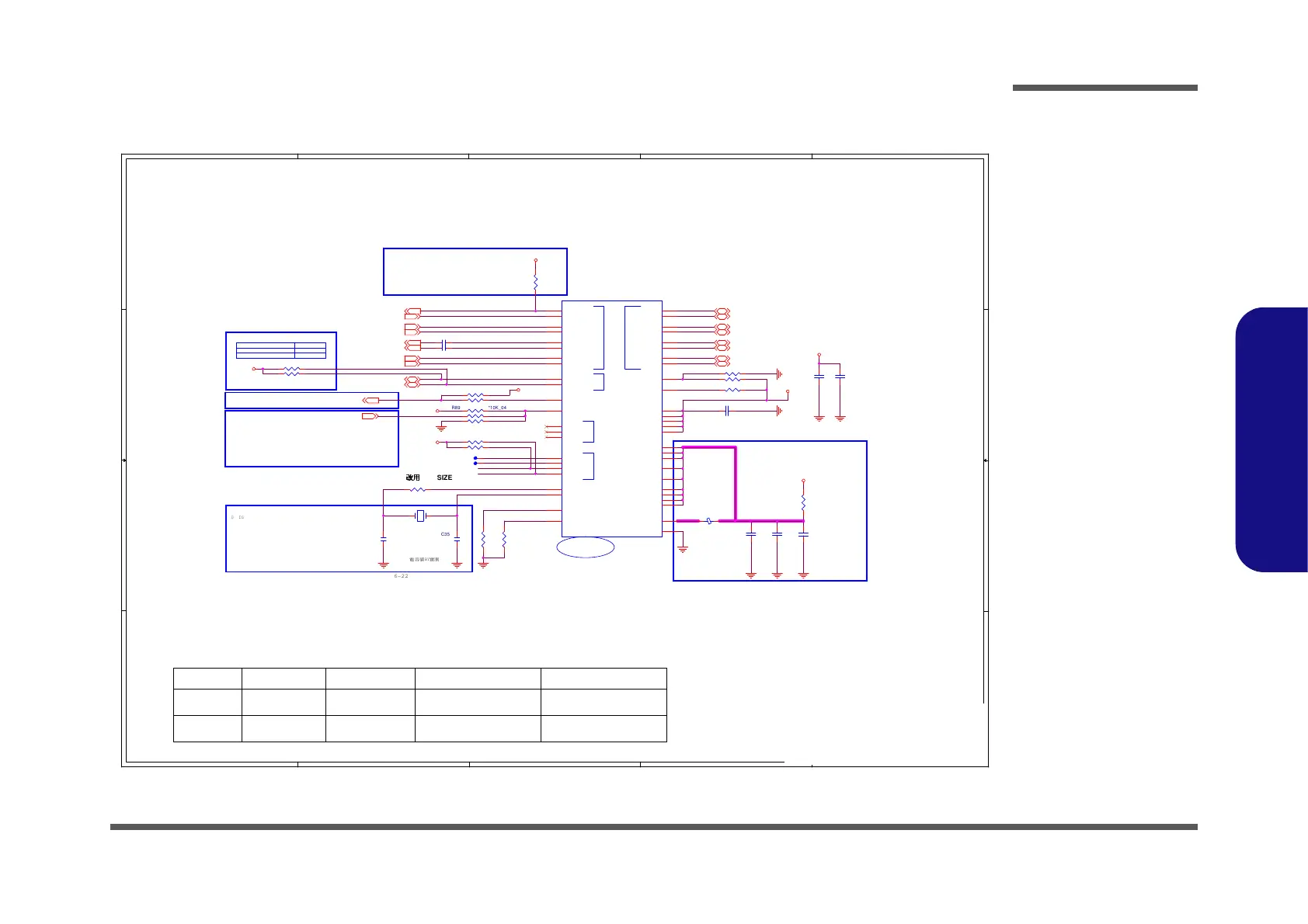

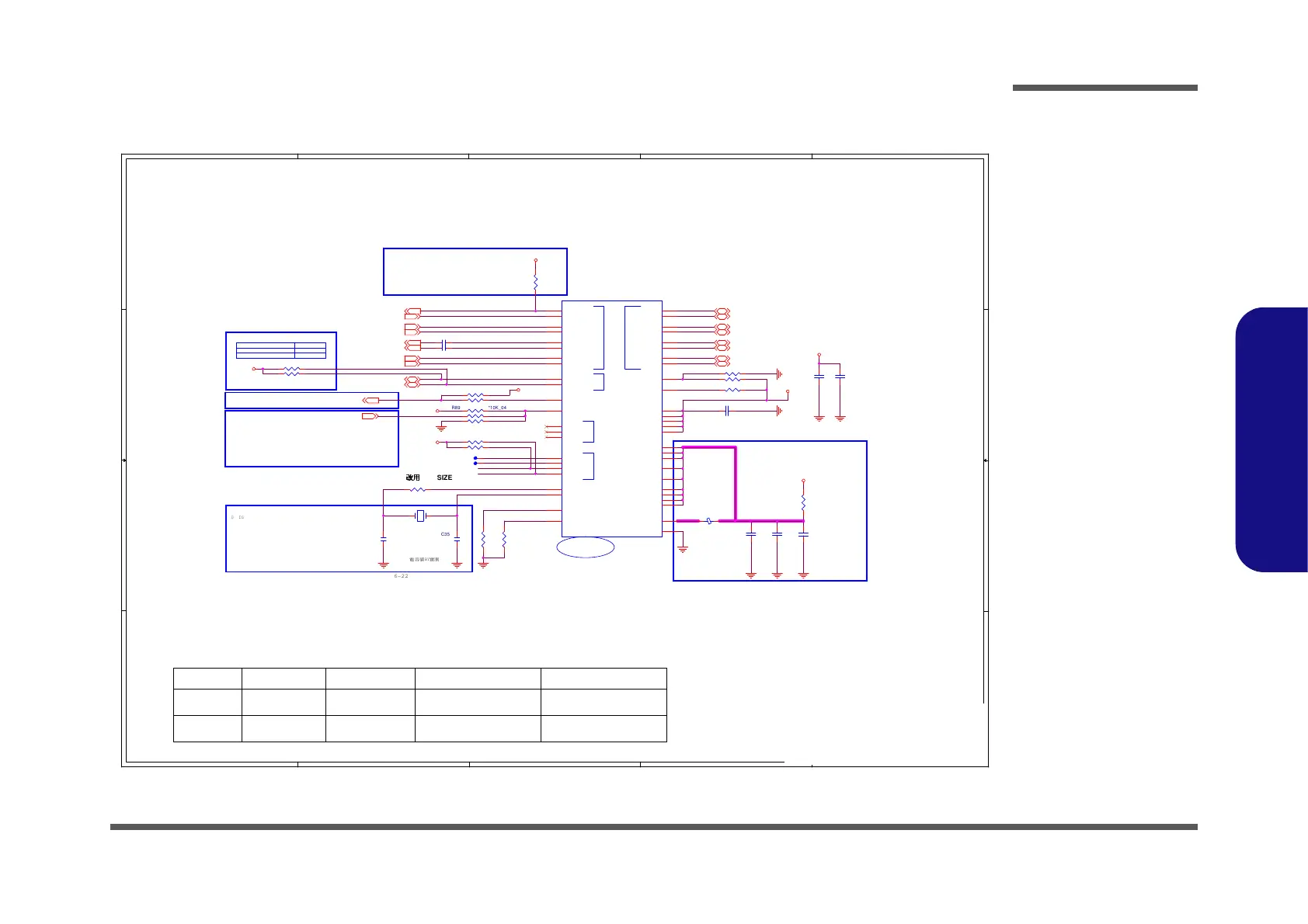

non-VPRO

U27

6-S03-00217-030

6-03-00217-030

QM87

HM87

U6

i217-LM

i217-V

VPRO

U16 U15

GIGA LAN (INTEL LAN I217)

6-S03-00087-0S3

6-03-00087-0S2

SB LAN ME Bios+EC

EON 64M EN25QH64

6-04-02564-A70

EON EN25QH32 32M

6-04-02532-493

LAN i217

The 10Kohm pull-up resistor of CLK_REQ_N is required

to either 3.3V Suspend (5, 6, 7) or Core (2) rail,

depending on the power well of PCH's input PCIECLKRQx#

buffer. See Platform Design Guide for more details

SMBUS PULL-UP OPTIONS

100KHz/400KHz 2.2Kohm

SMBUS SPEED

1MHz(Defaul setting) 499ohm

NOTE: Default SMBus

Address is 0xC8

NOTE: LANWAKE_N must be

connected to PCH's GPIO27.

NOTE: LAN_DISABLE_N must be connected

to PCH's GPIO12/LAN_PHY_PWR_CTRL.

This GPIO12 pin must be set as

"LAN_PHY_PC" function through FITC

tool.

DESIGN NOTE: PCH's LANPHYPC output

does not require pull-up. Resistors are no-stuff (for testing

purpose only).

ሽ୲ଖ

BY

ኔྒྷ

DESIGN NOTE: C7 & C8 value may vary depending on the

actual Cstray of the board. Cstray is varied because

specific board stack-up, layout, etc. For examples:

Using Cload=18pF Crystal part, if Cstray=7pF then

C7=C8=22pF and if Cstray=6pF then C7=C8=24pF.

Cload=[(C7*C8)/(C7+C8)] + Cstray.

Each design should measure the crystal’s ppm to make

sure it is within the I217 Specification.

Crystal

ޏ

ޏޏ

ޏش

شش

ش

5032 SIZE

6-22-25R00-1BV

6-22-25R00-1B4

6-22-25R00-1B5

Keep

short

and wide

NOTE: Total requirement Cout>=20uF. ESR<50mohm.

LAYOUT NOTE: Place L, C*3 and R close to PHY

M021011

EON 64M EN25QH64

6-04-02564-A70

EON EN25QH32 32M

6-04-02532-493

LAN_DISABLE_N

LANWAKE_N

LAN_JTAG_TDI

LAN_JTAG_TDO

LAN_XTAL_OUT

RES_BIAS

LAN_TEST_EN

LAN_XTAL_IN

PCIE_RXN5_C_GLAN

PCIE_RXP5_C_GLAN

CTRL_0P9

0.9V_LAN_M

LAN_MDIN0

LAN_MDIP0

LAN_MDIN1

LAN_MDIP1

LAN_MDIP2

LAN_MDIN2

LAN_MDIP3

LAN_MDIN3

SVR_EN_N

LAN_JTAG_TCK

LAN_JTAG_TMS

3.3V_LAN

VDD3

VDD3

VDD3

3.3V_LAN

3.3V_LAN

1.05V_LAN_M

3.3V_LAN

PM_LANPHY_EN19

LAN_WAKEUP#18,19,30

PCIE_RXP5_IGLAN20

SML0_DATA16,32

PCIE_RXN5_IGLAN20

PCIE_TXP5_IGLAN20

SML0_CLK16,32

IGLAN_CLKREQ#23

CLK_PCIE_IGLAN#23

PCIE_TXN5_IGLAN20

CLK_PCIE_IGLAN23

BUF_PLT_RST#18,29,30,32,34

LAN_MDIN3 25

LAN_MDIP2 25

LAN_MDIP3 25

LAN_MDIN1 25

LAN_MDIN0 25

LAN_MDIP1 25

LAN_MDIP0 25

LAN_MDIN2 25

Title

Size Document Number Rev

Date: Sheet

of

6-71-W2W50-D02

2.0

[24]INTEL LAN i217-LM

A3

24 44Friday, October 25, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: Sheet

of

6-71-W2W50-D02

2.0

[24]INTEL LAN i217-LM

A3

24 44Friday, October 25, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: Sheet

of

6-71-W2W50-D02

2.0

[24]INTEL LAN i217-LM

A3

24 44Friday, October 25, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

R89 *10K_04

C352

18p_50V_NPO_04

C83

0.1u_16V_X7R_04

C84 0.1u_10V_X7R_04

R69

*0_06

R91 4.7K_04

R68

3.01K_1%_04

R93 4.7K_04

R79

1K_04

R81 0_04

R90 0_04

C74 1u_6.3V_X5R_04

R84 *10K_04

R86 *10K_04

C85 0.1u_10V_X7R_04

R71 499_1%_04

.

L14

SWF2520CF-4R7M-M

X2

FSX5L_25MHZ

12

C72

22u_6.3V_X5R_08

C86

0.1u_16V_X7R_04

R76 0_04

R83 *10K_04

C88

0.1u_16V_X7R_04

C73

*10u_6.3V_X5R_06

PCIE

MDI

SMBUS

JTAG LED

U6

i217-LM

RSVD_VCC3P3

1

LANWAKE_N

2

LAN_DISABLE_N

3

VDD3P3_4

4

VDD3P3_5

5

SVR_EN_N

6

CTRL_0P9

7

VDD0P9_47

47

XTAL_OUT

9

XTAL_IN

10

VDD0P9_37

37

RBIAS

12

MDI_PLUS0

13

MDI_MINUS0

14

VDD3P3_15

15

VDD0P9_46

46

MDI_PLUS1

17

MDI_MINUS1

18

VDD3P3_19

19

MDI_PLUS2

20

MDI_MINUS2

21

VDD0P9_43

43

MDI_PLUS3

23

MDI_MINUS3

24

LED2

25

LED0

26

LED1

27

SMB_CLK

28

VDD3P3_29

29

TEST_EN

30

SMB_DATA

31

JTAG_TDI

32

JTAG_TMS

33

JTAG_TDO

34

JTAG_TCK

35

PE_RST_N

36

VDD0P9_16

16

PETp

38

PETn

39

VDD0P9_40

40

PERp

41

PERn

42

VDD0P9_22

22

PE_CLKP

44

PE_CLKN

45

VDD0P9_11

11

VDD0P9_8

8

CLK_REQ_N

48

GND_EPAD

49

R92

10K_04

R85 0_04

R82 499_1%_04

R80 *4.7K_04

C351

18p_50V_NPO_04

Loading...

Loading...