REV.-A

2.3.3

Operations

of

Slave

CPU

6303

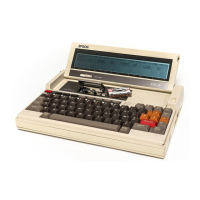

The slave

CPU

6303

is an

8-bit

CMOS CPU,

which

controls

the

microcassette

tape

(MCT), liquid

crystal

display

(LCD), ROM files, external speaker, and serial interface.

2.3.3.1

Operation

Modes

The operation

mode

of

the

6303

slave

CPU

is

determined

by

the

state

of

three

ports,

P20, P21,

and P22. Performance

of

mode

setting

is a hardware based

function,

occurring

immediately

after

power

up

or

whenever

the

reset

switch

is pressed.

When

the

reset signal goes high,

the

CPU

latches

the

state

of

the

three

ports

in

an

internal register.

When

the

reset signal is deactivated,

the

operation

mode

is

determined

according

to

the

information

latched.

The slave

CPU

performs

the

following

sequence

of

operations

after

each

deactivation

of

the

reset

signal:

• Latches

bits

2, 1, and 0

of

port

2 in

the

Program

Control

Register.

• Sets

the

vector

address

FFFE

and

the

contents

of

the

byte

location

addressed

by

FFFF

to

the

program

counter.

• Sets

the

interrupt

mask

bits.

• A data address is read

from

the

vector

address,

FFFF,

is

sent

to

the

program

counter,and

ini-

tiates

program

execution

from

that

address.

* Program

Control

Register

(0003H)

- stores

the

state

of

ports

20, 21,

and

22,

used

for

determin-

ing

the

operation

mode.

Fig.

2-40

illustrates a sample

CPU

operation

mode

selection,

mode

6

(multiplexed/partial

decode),

from

the

shown

combination

of

port

states.

Slave

CPU

6303

(130)

7

6 5 4

1

0

I PC2 I

PC1

I

PCO

11/041

~~

[

I/O

1

[

I/O

0 [

Port 2 data register

address

0003H

Mode

setting

port

stat

es

13E, pin

56

...................... · ......

Low

CN3, pin 8 ..............................

High

+5

...........................................

Fig.

2-40

Slave

CPU

Operation

Mode

Selection

Example

Mode

selection reults in

the

following

memory

mapping:

OOOOH

001FH

0080H

OOFFH

Internal External Internal

Not

used

register

RAM

memory

8000H

9800H

FOOOH

FFFFH

:

,

:

Internal

Not

used

:

ROM

:

...

V-RAM Slave

CPU

operation control

mask ROM

Fig.

2-41

Resultant

Memory

Mapping

Example

2-44

Loading...

Loading...