14.5. RTC self monitoring Detection

These bits are flag bit of each of functions of RTC.

It is a flag bit that detects the state of this product and holds the result.

- POR Power ON Reset detection

- VLF Detects Internal Voltage Low.

- XST Oscillation stop detection.

- EVIN Event input status.

- VCMP Battery Charge status.

- VLOW bit Battery Low.

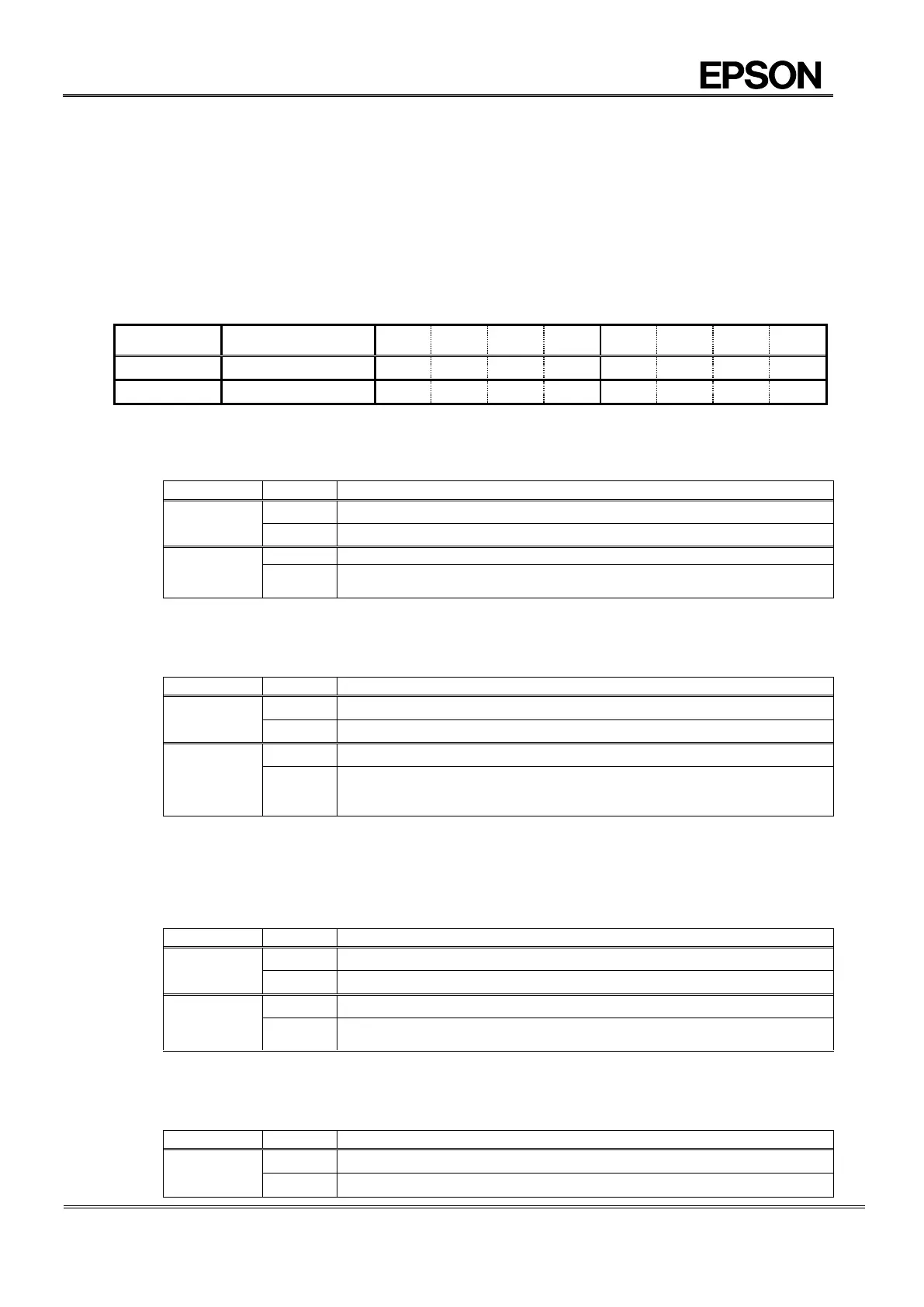

14.5.1. Related registers for RTC internal status detection

Table 35 RTC Internal status detection registers

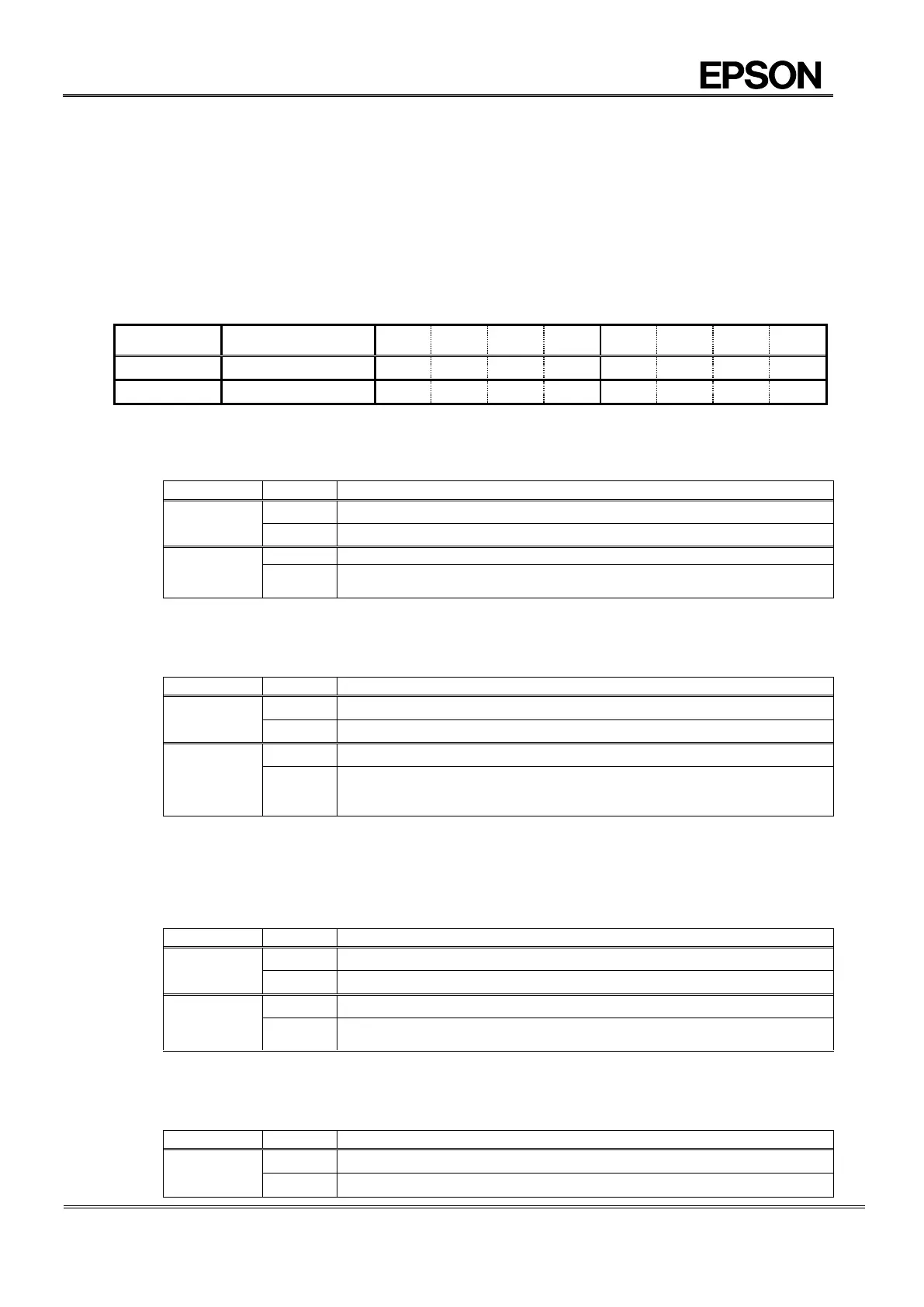

1) POR bit (Power On Reset)

This bit records power on reset operation.

Table 36 POR bit (Power On Reset)

The POR bit is cleared to 0 and waiting for the next power on reset detection

Invalid (writing “1” will be ignored)

No power on reset detection

Power on reset is detected. The result remains until clearing “0”.

All registers are set into default condition by power on rest.

2) VLF bit (Voltage Low Flag)

This bit is reflected with status of POR or XST.

Table 37 VLF bit (Voltage Low Flag)

The VLF is cleared to 0 and waiting for next low voltage detection.

Invalid (writing “1” will be ignored)

Oscillation status is normal, RTC register data are valid.

Either power on reset or X’tal oscillation stop is detected. The result remains

until clearing “0”. User can check the RTC status and initialize by software.(At

power on timing etc.)

3) XST bit (X’tal Oscillation Stop )

This bit records RTC internal crystal oscillation stop status.

Time stamp function is not active if there is no oscillation; it will be active once oscillation begins

when oscillation stopped longer than 10 ms, XST is set to 1. This bit is not cleared to “0” by power on reset.

Table 38 XST bit (X’tal Oscillation Stop)

The XST is cleared to 0 and waiting for next oscillation stop detection.

Invalid (writing “1” will be ignored)

No RTC internal crystal oscillation stop detection

RTC internal crystal oscillation stop is detected. The result remains until

clearing “0”.

4) EVIN bit (Input level monitor of EVIN terminal)

This bit monitored EVIN terminal input voltage High / Low.

Table 39 EVIN bit (EVIN Level)

EVIN terminal input voltage Low level

EVIN terminal input voltage High level

Loading...

Loading...