INTEGRATED CIRCUIT

M3030RFXPFP

GNOK-M3030RFXPFP-00 4/9

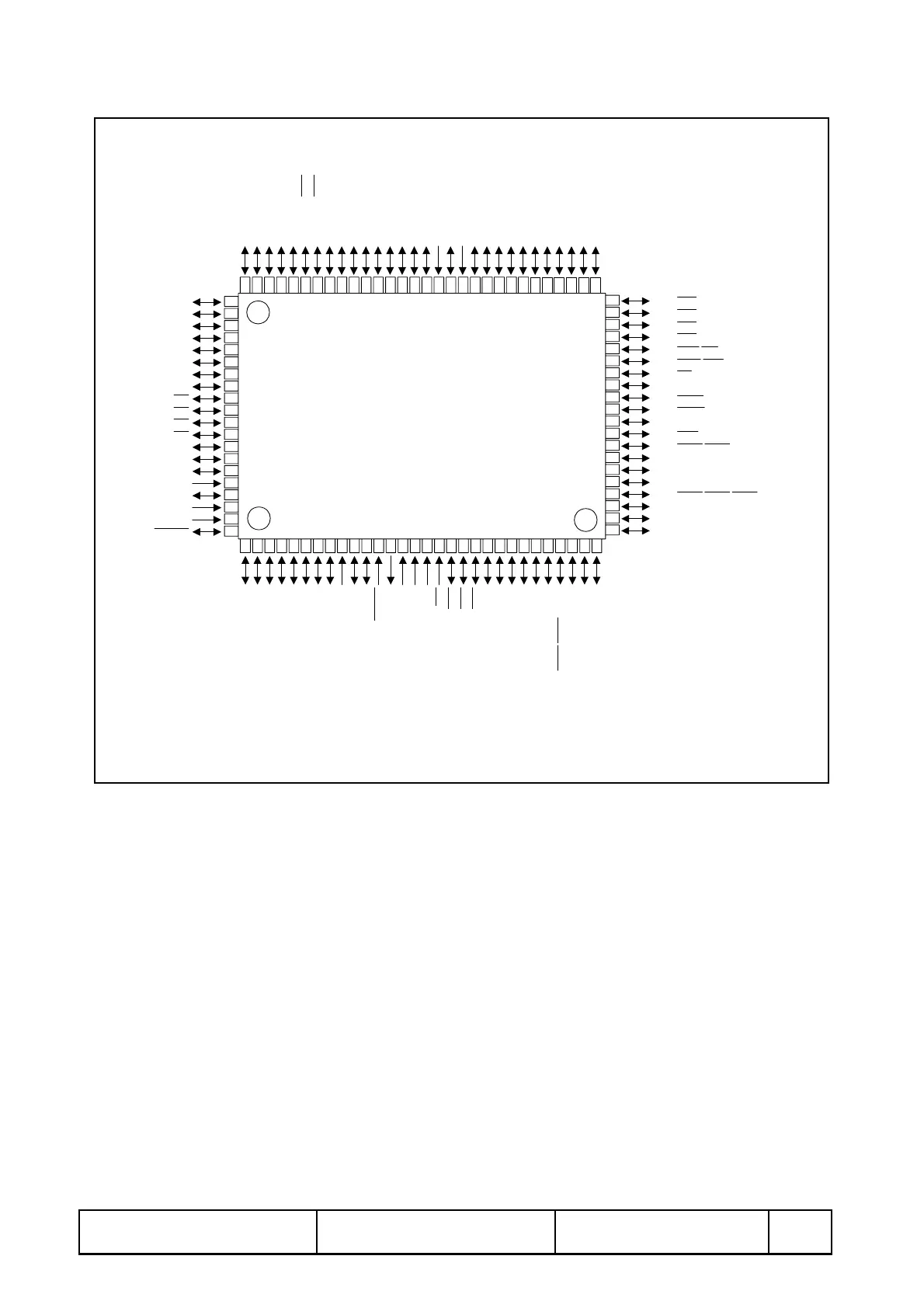

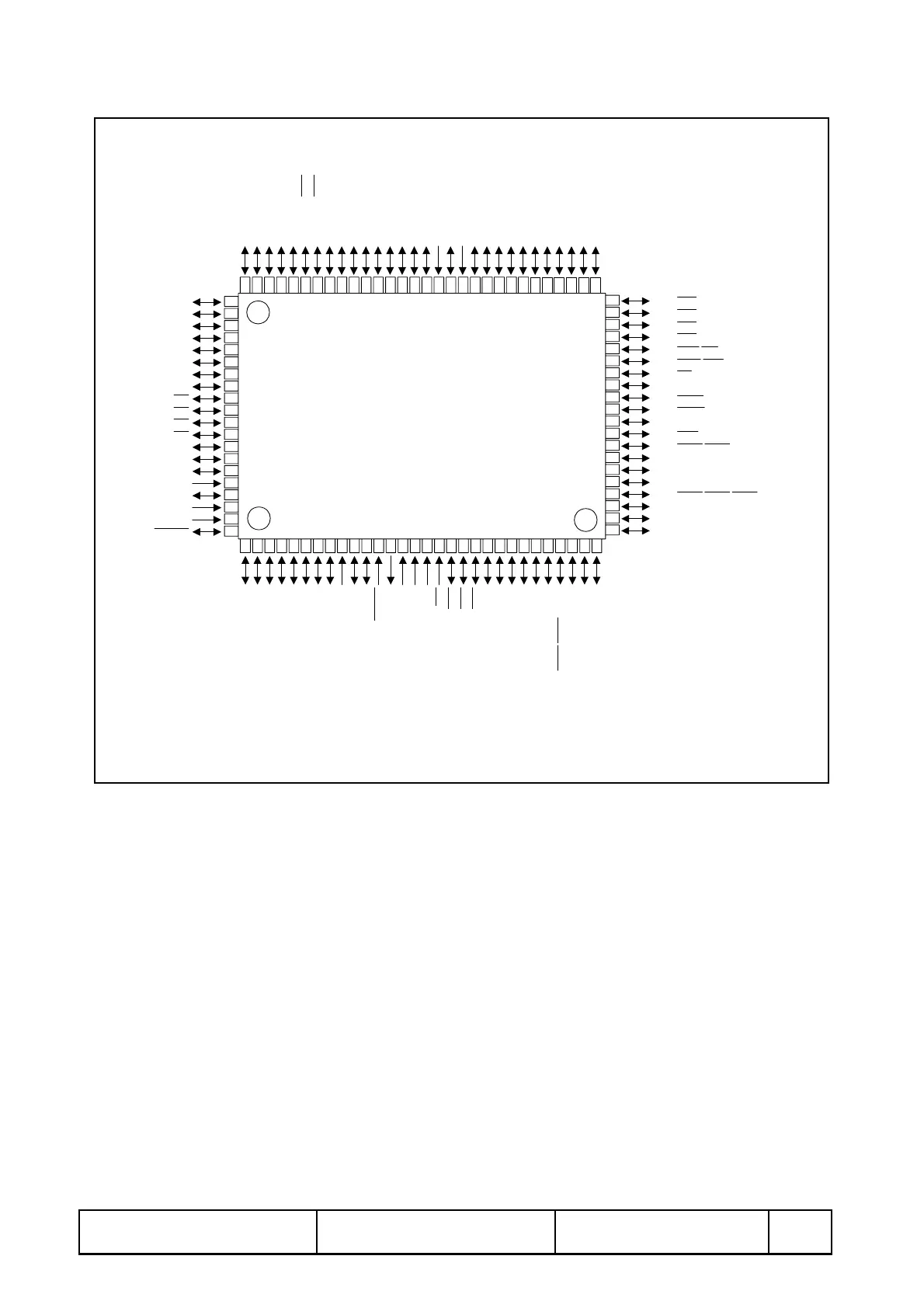

Figure 1.2 Pin Configuration (Top View)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

515253545556575859606162636465666768697071727374757677787980

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

1

00

P0_0/AN0_0/D0

P0_1/AN0_1/D1

P0_2/AN0_2/D2

P0_3/AN0_3/D3

P0_4/AN0_4/D4

P0_5/AN0_5/D5

P0_6/AN0_6/D6

P0_7/AN0_7/D7

P1_0/D8

P1_1/D9

P1_2/D10

P1_3/D11

P1_4/D12

VREF

AVSS

VCC1

XIN

XOUT

VSS

RESET

CNVSS

P8_7/XCIN

P8_6/XCOUT

BYTE

P3_0/A8

P3_1/A9

P3_2/A10

P3_3/A11

P3_4/A12

P3_5/A13

P3_6/A14

P3_7/A15

P4_0/A16

P4_1/A17

P4_2/A18

P4_3/A19

P7_4/TA2OUT

P7_6

P5_6/ALE

P7_7

P5_5/HOLD

P5_4/HLDA

P5_3/BCLK

P5_2/RD

VCC2

VSS

P5_7/RDY/CLKOUT

P4_5/CS1

P4_6/CS2

P4_7/CS3

AVCC

P6_3/TXD0/SDA0

P6_5/CLK1

P6_6/RXD1/SCL1

P6_7/TXD1/SDA1

P6_1/CLK0

P6_2/RXD0/SCL0

P10_0/AN0

P10_1/AN1

P10_2/AN2

P10_3/AN3

P9_3

P9_4

P9_5/ANEX0

P9_6/ANEX1

P9_1/TB1IN

P9_2/TB2IN

P8_0

P6_0/CTS0/RTS0

P6_4/CTS1/RTS1/CTS0/CLKS1

P7_2/CLK2/TA1OUT

P8_2/INT0

P7_1/RXD2/SCL2/TA0IN

(1)

P8_3/INT1

P8_5/NMI

P9_7/ADTRG

P4_4/CS0

P5_0/WRL/WR

P5_1/WRH/BHE

P9_0/TB0IN

P7_0/TXD2/SDA2/TA0OUT

(1)

P8_4/INT2

P8_1

P7_3/CTS2/RTS2/TA1IN

P7_5/TA2IN

P1_5/D13/INT3

P1_6/D14/INT4

P1_7/D15

P10_7/AN7/KI3

P10_6/AN6/KI2

P10_5/AN5/KI1

P10_4/AN4/KI0

P2_0/A0

P2_1/A1

P2_2/A2

P2_3/A3

P2_4/A4

P2_5/A5

P2_6/A6

P2_7/A7

0&3*URXS

Package : PRQP0100JB-A (100P6S-A)

PIN CONFIGURATION (top view)

NOTES:

1. P7_0 and P7_1 are N channel open-drain output pins.

2. Use the M16C/30P on VCC1=VCC2.

Loading...

Loading...