V

SS

V

SS

T

AXR1[0]/

GP4[0]

AXR1[11]/

GP5[11]

SPI0_CLK/

EQEP1I/

GP5[2]/

BOOT[2]

SPI1_CLK/

EQEP1S/

GP5[7]/

BOOT[7]

1 2 3 4 5 6

EMA_CS[3]/

AMUTE2/

GP2[6]

7

EMA_CS[0]

UHPI_HAS

/

/

GP2[4]

8

EMA_A[0]/

GP1[0]

9

EMA_A[4]/

GP1[4]

10

EMA_A[8]/

GP1[8]

1

1

EMA_SDCKE/

GP2[0]

12

EMA_D[0]/

MMCSD_DAT[0]/

UHPI_HD[0]/

GP0[0]/

BOOT[12]

13

EMA_D[9]/

UHPI_HD[9]/

GP0[9]

14

V

SS

V

SS

15 16

DV

DD

R

AXR1[1]/

GP4[1]

UART0_RXD/

I2C0_SDA/

TM64P0_IN12/

GP5[8]/

BOOT[8]

SPI1_ENA/

UART2_RXD/

GP5[12]

SPI0_ENA

UART0_CTS

/

/

EQEP0A/

GP5[3]/

BOOT[3]

SPIO_SOMI[0]/

EQEPOI/

GP5[0]/

BOOT[0]

EMA_OE

UHPI_HDS1

/

/

AXR0[13]/

GP2[7]

EMA_BA[0]/

GP1[14]

EMA_A[1]/

MMCSD_CLK/

UHPI_HCNTL0/

GP1[1]

EMA_A[5]/

GP1[5]

EMA_A[9]/

GP1[9]

EMA_CLK/

OBSCLK/

AHCLKR2/

GP1[15]

EMA_D[2]/

MMCSD_DAT[2]/

UHPI_HD[2]/

GP0[2]

EMA_D[10]/

UHPI_HD[10]/

GP0[10]

EMA_D[1]/

MMCSD_DAT[1]/

UHPI_HD[1]/

GP0[1]

DV

DD

P

AXR1[3]/

EQEP1A/

GP4[3]

AXR1[2]/

GP4[2]

UART0_TXD/

I2C0_SCL/

TM64P0_OUT12/

GP5[9]/

BOOT[9]

SPI1_SCS[0]/

UART2_TXD/

GP5[13]

SPI1_SOMI[0]/

I2C1_SCL/

GP5[5]/

BOOT[5]

SPI0_SIMO[0]/

EQEP0S/

GP5[1]/

BOOT[1]

EMA_CS[2]

UHPI_HCS

/

/

GP2[5]/

BOOT[15]

EMA_BA[1]/

UHPI_HHWIL/

GP1[13]

EMA_A[2]/

MMCSD_CMD/

UHPI_HCNTL1/

GP1[2]

EMA_A[6]/

GP1[6]

EMA_A[11]/

GP1[11]

EMA_WE_

DQM[1]

UHPI_HDS2

/

/

AXR0[14]/

GP2[8]

EMA_D[4]/

MMCSD_DAT[4]/

UHPI_HD[4]/

GP0[4]

EMA_D[12]/

UHPI_HD[12]/

GP0[12]

EMA_D[3]/

MMCSD_DAT[3]/

UHPI_HD[3]/

GP0[3]

EMA_D[11]/

UHPI_HD[11]/

GP0[11]

N

AXR1[5]/

EPWM2B/

GP4[5]

AXR1[4]/

EQEP1B/

GP4[4]

AXR1[10]/

GP5[10]

SPI0_SCS[0]

UART0_RTS

/

/

EQEP0B/

GP5[4]/

BOOT[4]

SPI1_SIMO[0]/

I2C1_SDA/

GP5[6]/

BOOT[6]

EMA_WAIT[0]/

/

GP2[10]

UHPI_HRDY

EMA_RAS/

EMA_CS[5]/

GP2[2]

EMA_A[10]/

GP1[10]

EMA_A[3]/

GP1[3]

EMA_A[7]/

GP1[7]

EMA_A[12]/

GP1[12]

EMA_D[8]/

UHPI_HD[8]/

GP0[8]

EMA_D[6]/

MMCSD_DAT[6]/

UHPI_HD[6]/

GP0[6]

EMA_D[14]/

UHPI_HD[14]/

GP0[14]

EMA_D[5]/

MMCSD_DAT[5]/

UHPI_HD[5]/

GP0[5]

EMA_D[13]/

UHPI_HD[13]/

GP0[13]

M

AXR1[9]/

GP4[9]

AXR1[8]/

EPWM1A/

GP4[8]

AXR1[7]/

EPWM1B/

GP4[7]

AXR1[6]/

EPWM2A/

GP4[6]

DV

DD

V

SS

V

SS

DV

DD

DV

DD

V

SS

V

SS

DV

DD

EMA_WE

W

/

UHPI_HR /

AXR0[12]/

GP2[3]/

BOOT[14]]

EMA_WE_

DQM[0]

UHPI_HINT

/

/

AXR0[15]/

GP2[9]

EMA_D[7]/

MMCSD_DAT[7]/

UHPI_HD[7]/

GP0[7]/

BOOT[13]

EMA_D[15]/

UHPI_HD[15]/

GP0[15]

L

AHCLKR1/

GP4[1

1]

ACLKR1/

ECAP2/

APWM2/

GP4[12]

AFSR1/

GP4[13]

AMUTE0/

RESETOUT

DV

DD

CV

DD

V

SS

V

SS

V

SS

V

SS

DV

DD

DV

DD

EMB_CAS EMB_D[22] EMB_D[23]

EMA_CAS

EMA_CS[4]

/

/

GP2[1]

K

GP7[14]

AHCLKX1/

EPWM0B/

GP3[14]

ACLKX1/

EPWM0A/

GP3[15]

AFSX1/

EPWMSYNCI/

EPWMSYNCO/

GP4[10]

DV

DD

CV

DD

V

SS

V

SS

CV

DD

CV

DD

DV

DD

EMB_D[20]

EMB_WE_

DQM[0]/

GP5[15]

EMB_WE EMB_D[21]CV

DD

TMS

J

TDI TDO TRST

EMU[0]/GP7[15]

CV

DD

CV

DD

V

SS

V

SS

CV

DD

CV

DD

CV

DD

EMB_D[5]/

GP6[5]

EMB_D[19]

EMB_D[6]/

GP6[6]

EMB_D[7]/

GP6[7]

RTC_XI

H

RTC_XO TCK

NC

USB0_

VDDA33

CV

DD

V

SS

V

SS

CV

DD

CV

DD

EMB_D[3]/

GP6[3]

EMB_D[17] EMB_D[18]

EMB_D[4]/

GP6[4]

RTC_CV

DD

G

RTC_V

SS

RESET USB0_DM

DV

DD

CV

DD

V

SS

V

SS

CV

DD

CV

DD

DV

DD

CV

DD

EMB_D[1]/

GP6[1]

EMB_D[31] EMB_D[16]

EMB_D[2]/

GP6[2]

OSCOUT

F

OSCIN NC USB0_DP

DV

DD

CV

DD

RSV1

V

SS

V

SS

V

SS

DV

DD

DV

DD

EMB_D[15]/

GP6[15]

EMB_D[29] EMB_D[30]

EMB_D[0]/

GP6[0]

PLL0_VSSA

E

OSCVSS

USB0_

VDDA18

USB0_

DRVVBUS/

GP4[15]

DV

DD

V

SS

V

SS

DV

DD

V

SS

V

SS

DV

DD

DV

DD

EMB_D[13]/

GP6[13]

EMB_D[27] EMB_D[28]

EMB_D[14]/

GP6[14]

PLL0_VDDA

D

USB0_ID USB0_VBUS

AMUTE1/

EHRPWMTZ/

GP4[14]

AFSX0/

GP2[13]/

BOOT[10]

UART1_TXD/

AXR0[10]/

GP3[10]

AXR0[6]/

ACLKR2/

GP3[6]

AXR0[2]/

AXR2[3]/

GP3[2]

EMB_CS[0]

EMB_A[0]/

GP7[2]

EMB_A[4]/

GP7[6]

EMB_A[8]/

GP7[10]

EMB_D[9]/

GP6[9]

EMB_D[10]/

GP6[10]

EMB_D[11]/

GP6[11]

EMB_D[12]/

GP6[12]

NC

C

NC

USB0_

VDDA12

AFSR0/

GP3[12]

ACLKX0/

ECAP0/

APWM0/

GP2[12]

UART1_RXD/

AXR0[9]/

GP3[9]

AXR0[5]/

AFSX2/

GP3[5]

AXR0[1]/

ACLKX2/

GP3[1]

EMB_BA[0]/

GP7[1]

EMB_A[1]/

GP7[3]

EMB_A[5]/

GP7[7]

EMB_A[9]/

GP7[11]

EMB_SDCKE EMB_CLK

EMB_WE_

DQM[1]/

GP5[14]

EMB_D[8]/

GP6[8]

B

RSV2 V

SS

ACLKR0/

ECAP1/

APWM1/

GP2[15]

AHLKX0/

AHCLKX2/

USB_

REFCLKIN/

GP2[11]

AXR0[8]/

GP3[8]

AXR0[4]/

AXR2[1]/

GP3[4]

AXR0[0]/

AFSR2/

GP3[0]

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

EMB_BA[1]/

GP7[0]

EMB_A[2]/

GP7[4]

EMB_A[6]/

GP7[8]

EMB_A[11]/

GP7[13]

EMB_WE_

DQM[2]

EMB_D[25]

EMB_A[12]/

GP3[13]

DV

DD

A

V

SS

V

SS

AHCLKR0/

GP2[14]/

BOOT[11]

AXR0[11]/

AXR2[0]/

GP3[11]

AXR0[7]/

GP3[7]

AXR0[3]/

AXR2[2]/

GP3[3]

EMB_RAS

EMB_A[10]/

GP7[12]

EMB_A[3]/

GP7[5]

EMB_A[7]/

GP7[9]

EMB_WE_

DQM[3]

EMB_D[24] EMB_D[26] V

SS

V

SS

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

CV

DD

CV

DD

V

SS

V

SS

TMS320DA810/808/807/805

www.ti.com

SPRS595–JANUARY 2010

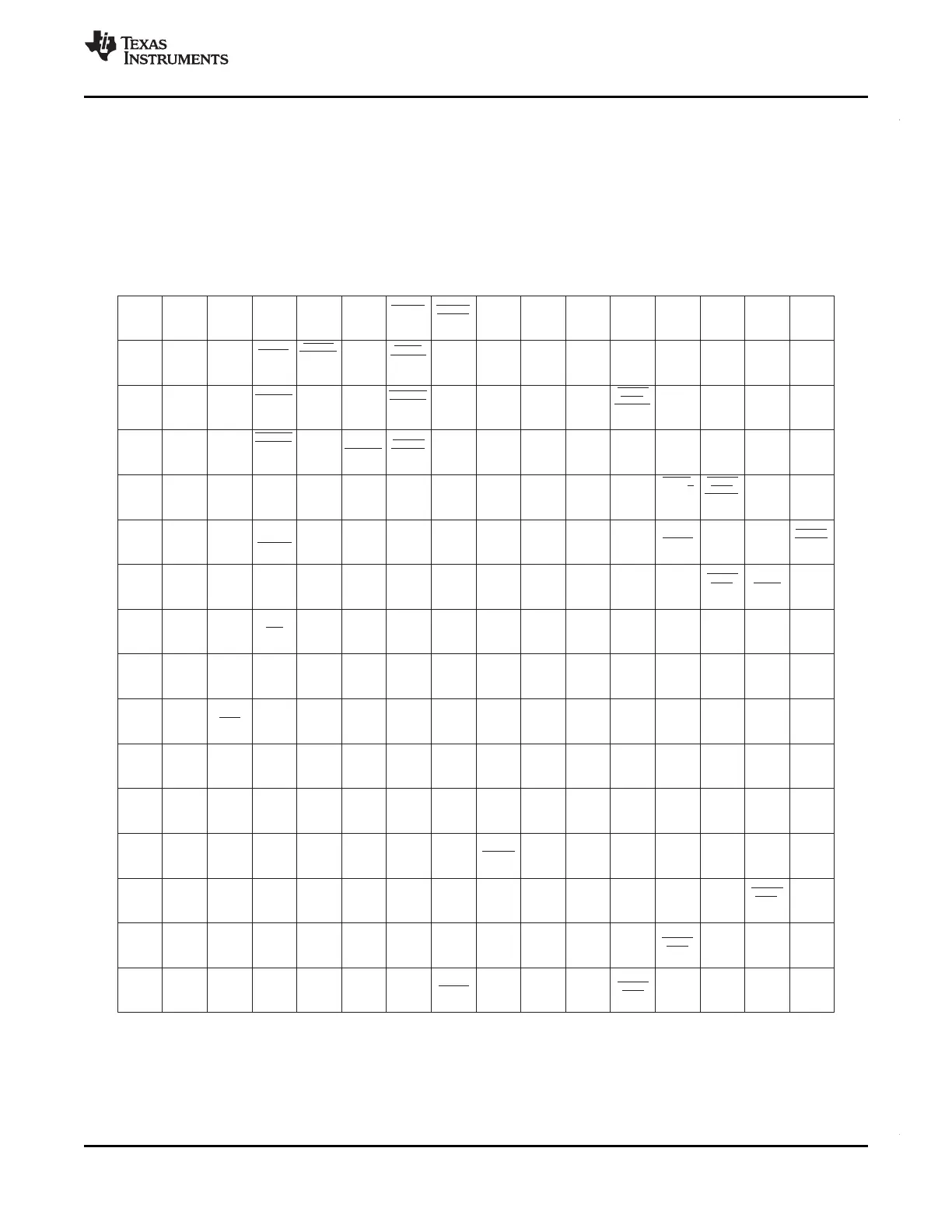

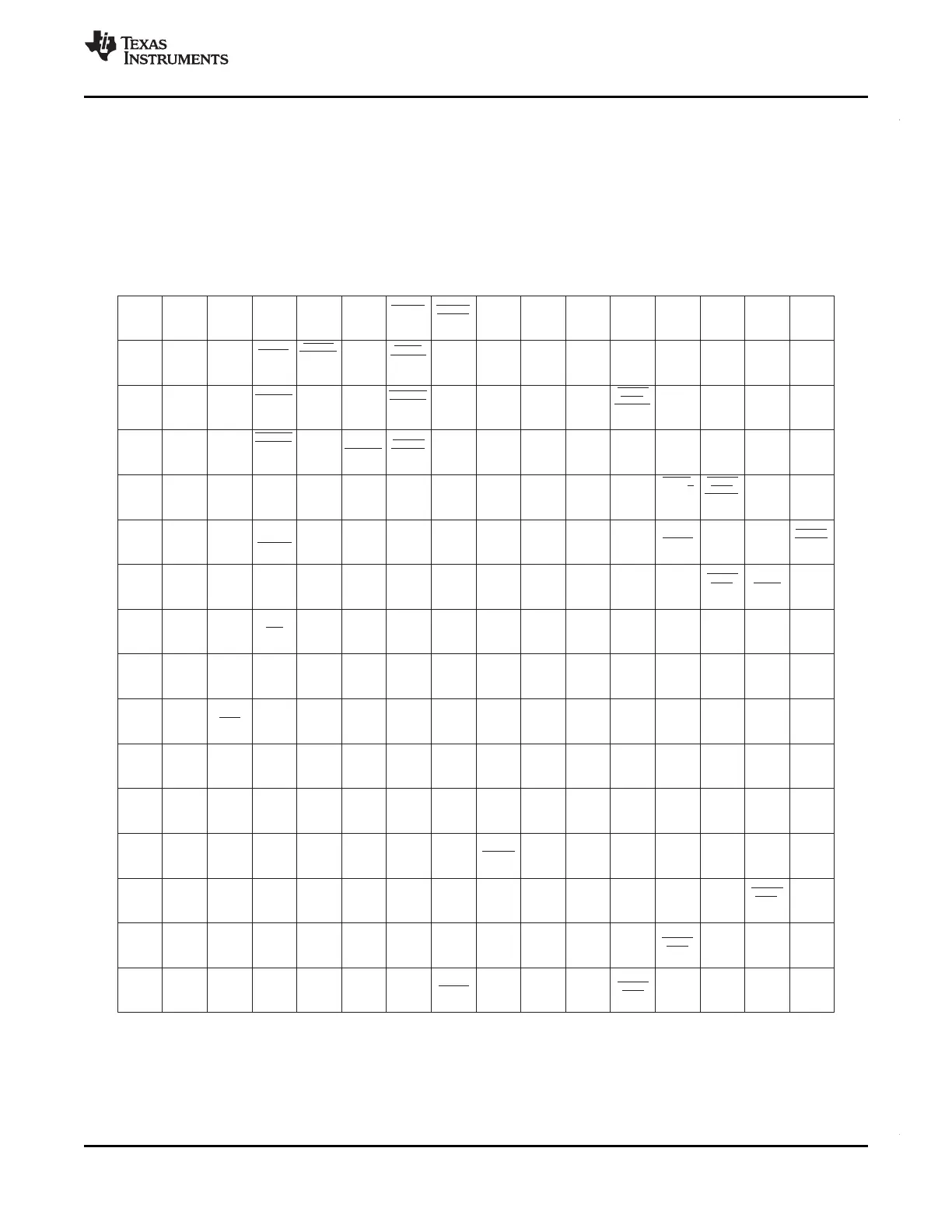

3.5 Pin Assignments

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in

the smallest possible package. Pin multiplexing is controlled using a combination of hardware

configuration at device reset and software programmable register settings.

3.5.1 Pin Map (Bottom View)

Figure 3-3 and Figure 3-4 show the pin assignments for ZKB package and PTP package respectively.

Figure 3-3. Pin Map (ZKB)

Copyright © 2010, Texas Instruments Incorporated Device Overview 25

Submit Documentation Feedback

Product Folder Link(s): TMS320DA810/808/807/805

Loading...

Loading...