x Organized as 1 block of 256 bytes (1 x 256 x 8)

x 2-wire serial interface bus, I

2

C™ compatible

x Schmitt Trigger inputs for noise suppression

x Output slope control to eliminate ground bounce

x 100 kHz (24AA02) and 400 kHz (24LC02B) compatibility

x Self-timed write cycle (including auto-erase)

x Page write buffer for up to 8 bytes

x 2ms typical write cycle time for page write

x Hardware write-protect for entire memory

x Can be operated as a serial ROM

x Factory programming (QTP) available

x ESD protection > 4,000V

x 1,000,000 erase/write cycles

x Data retention > 200 years

x 8-lead PDIP, SOIC, TSSOP and MSOP packages

x 5-lead SOT-23 package

x Pb-free finish available

x Available for extended temperature ranges:

-Industrial (I): -40°C to +85°C

-Automotive (E): -40°C to +125°C

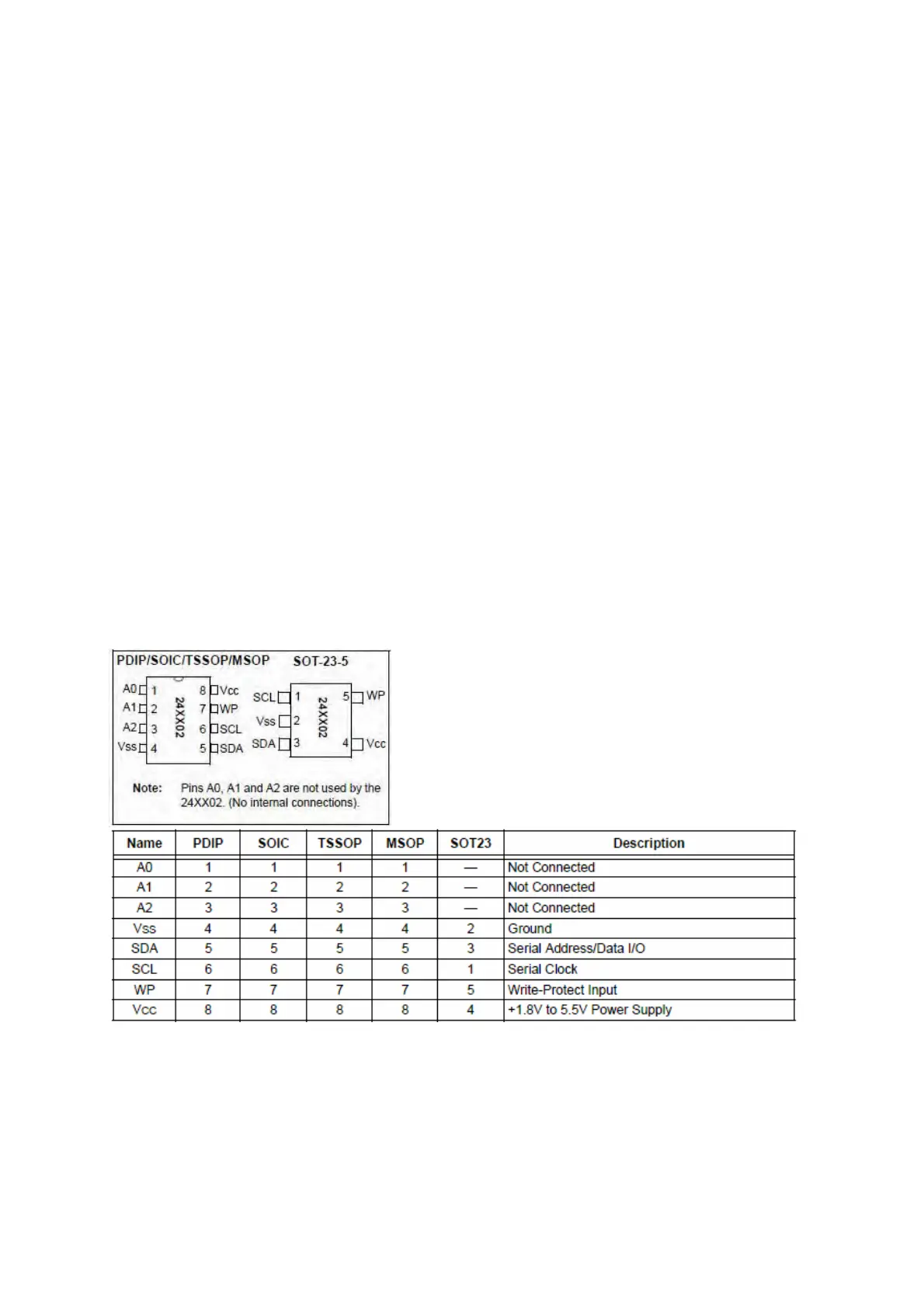

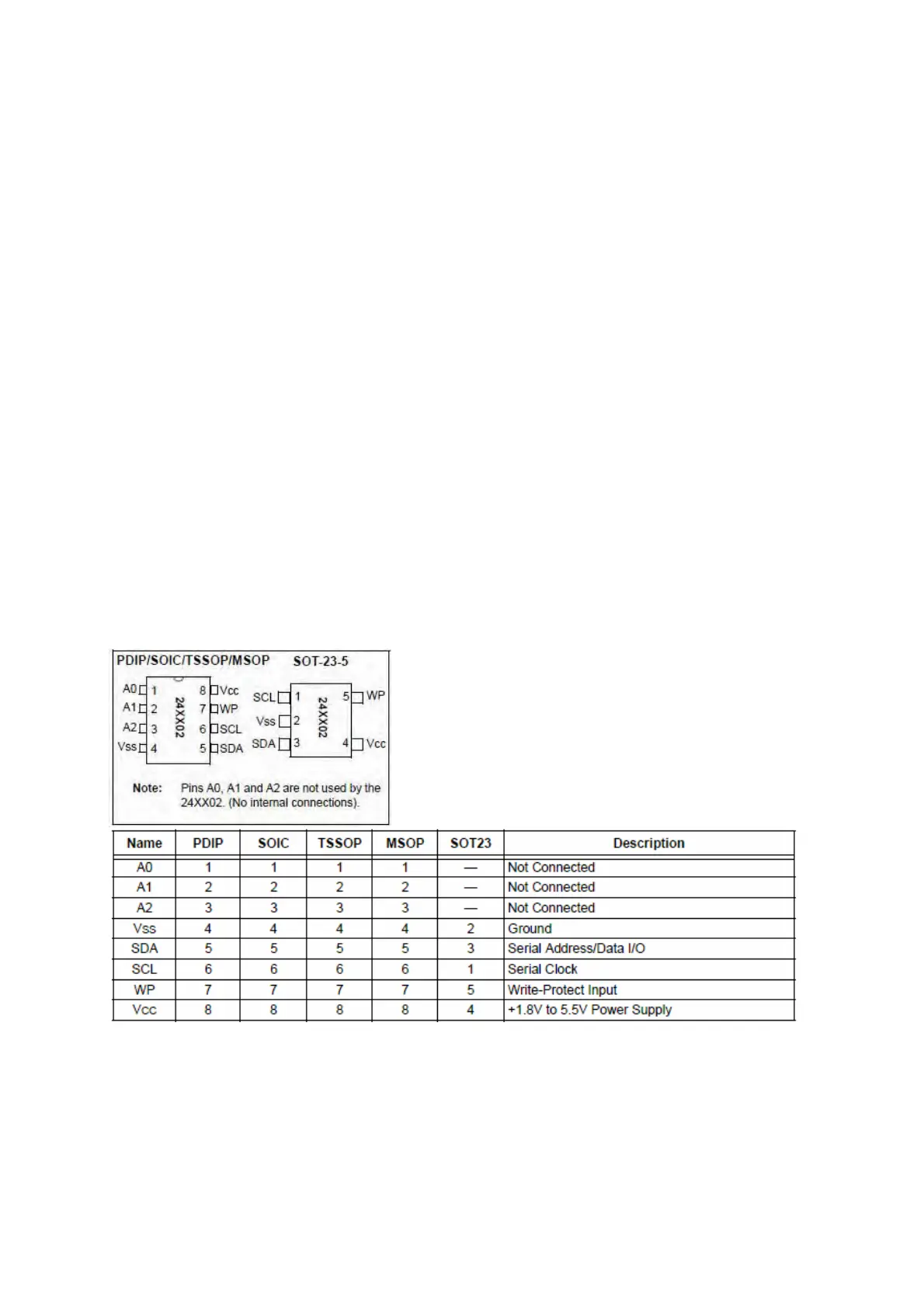

10.6.3 Pinning

10.7. μPA672T

10.7.1. General Description

N-channel Mos-Fet array for switching.The μPA672T is a super-mini-mold device

provided with two MOS FET elements. It achieves high-density mounting and saves

mounting costs.

Loading...

Loading...