Intel Desktop Board DN2800MT Technical Product Specification

62

2.2.3.6 Debug Header

During the POST, the BIOS generates diagnostic progress codes (POST codes) to I/O

port 80h. If the POST fails, execution stops and the last POST code generated is left at

port 80h. This code is useful for determining the point where an error occurred.

Displaying the POST codes requires a POST card that can interface with the Debug

header. The POST card can decode the port and display the contents on a medium

such as a seven-segment display.

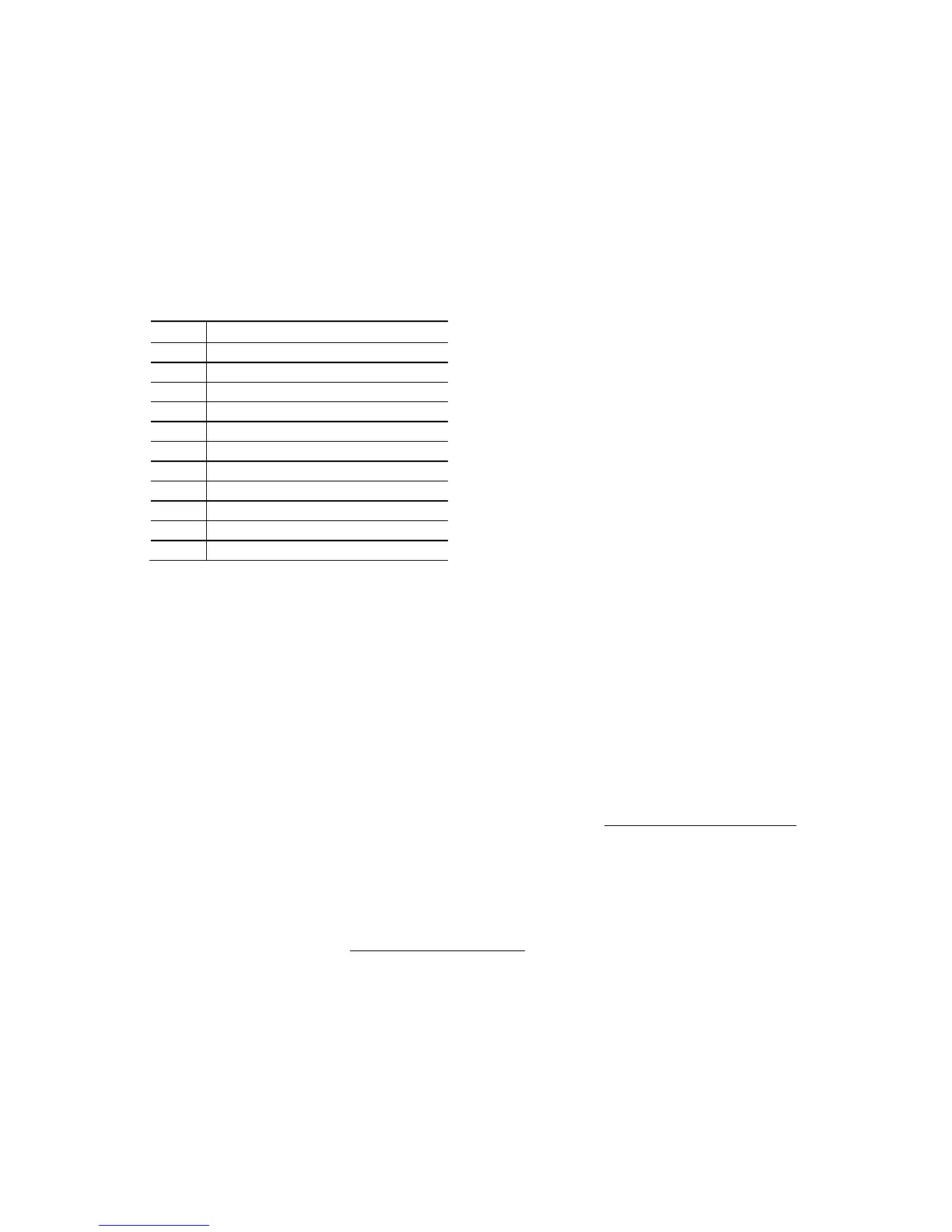

Table 37. Debug Header

3 PLTRST#

10 GND

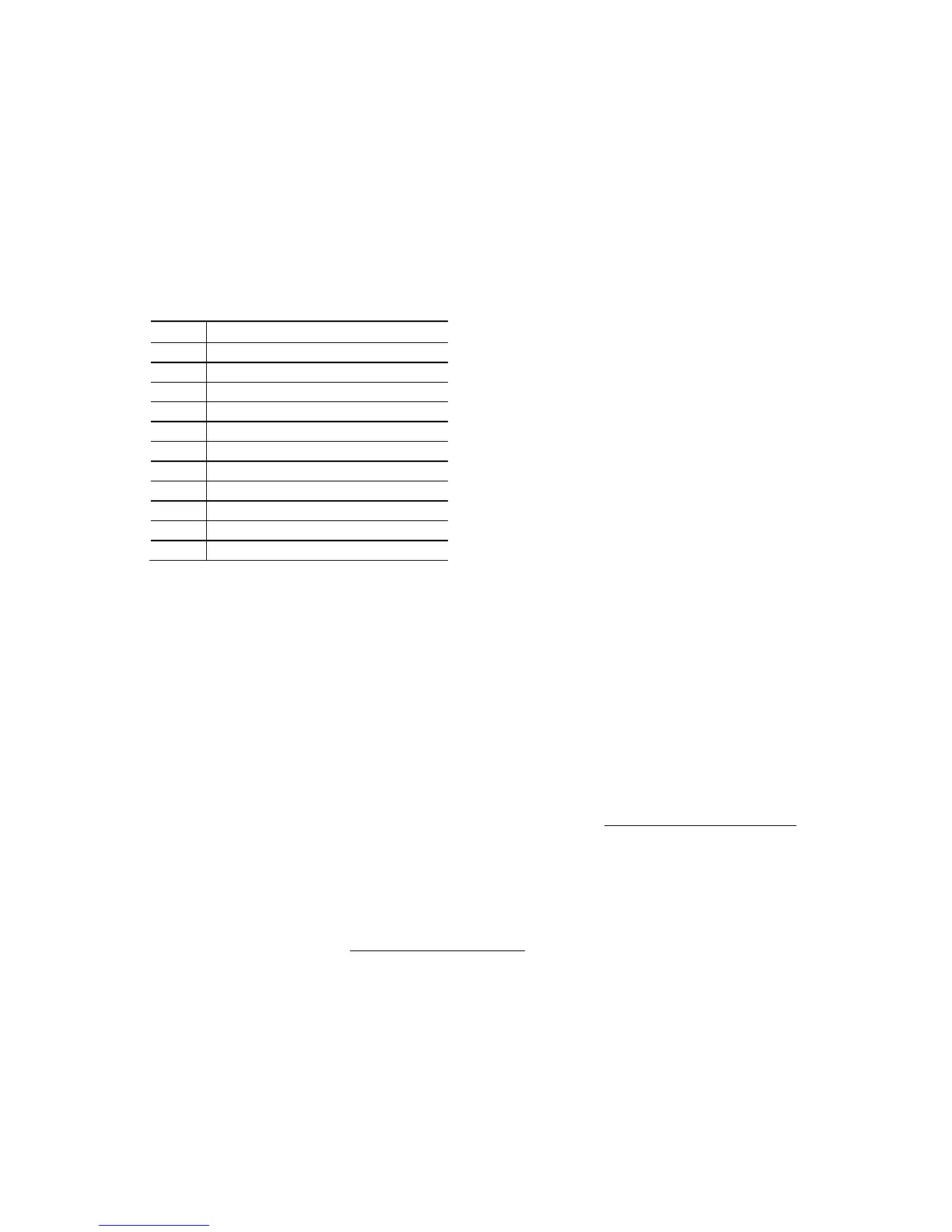

2.2.3.7 Custom Solutions Header

The Customs Solution header is provided to aid customers in developing unique

applications.

• WDTO#: indicates when the Watchdog Timer in the Super I/O device has expired.

This is a general purpose implementation that can be wired to external systems

(i.e., industrial control, etc.) or to the reset pin on the board (if the intended use is

to reset the board). Intel can provide sample code for customers who write their

own applications that require Watchdog Timer support.

• SMB_CLK and SMB_DATA: SMBus interface, reserved for Intel use. General SMBus

information can be found on the platform EDS and at http://smbus.org/specs/.

• 3.3 V Standby: can be used to monitor the presence of 3.3 V standby power

(functions in the same manner as the 3.3 V standby power LED).

• PWRBT#: power button signal (functions in the same manner as the power button

pin on the front panel header).

• HDMI Consumer Electronics Control (CEC): standard communication signal from

the HDMI connector (http://www.hdmi.org/) - the signal is exposed through the

Custom Solutions header for third party solutions to monitor/control CEC activity

between multiple HDMI devices.

Loading...

Loading...