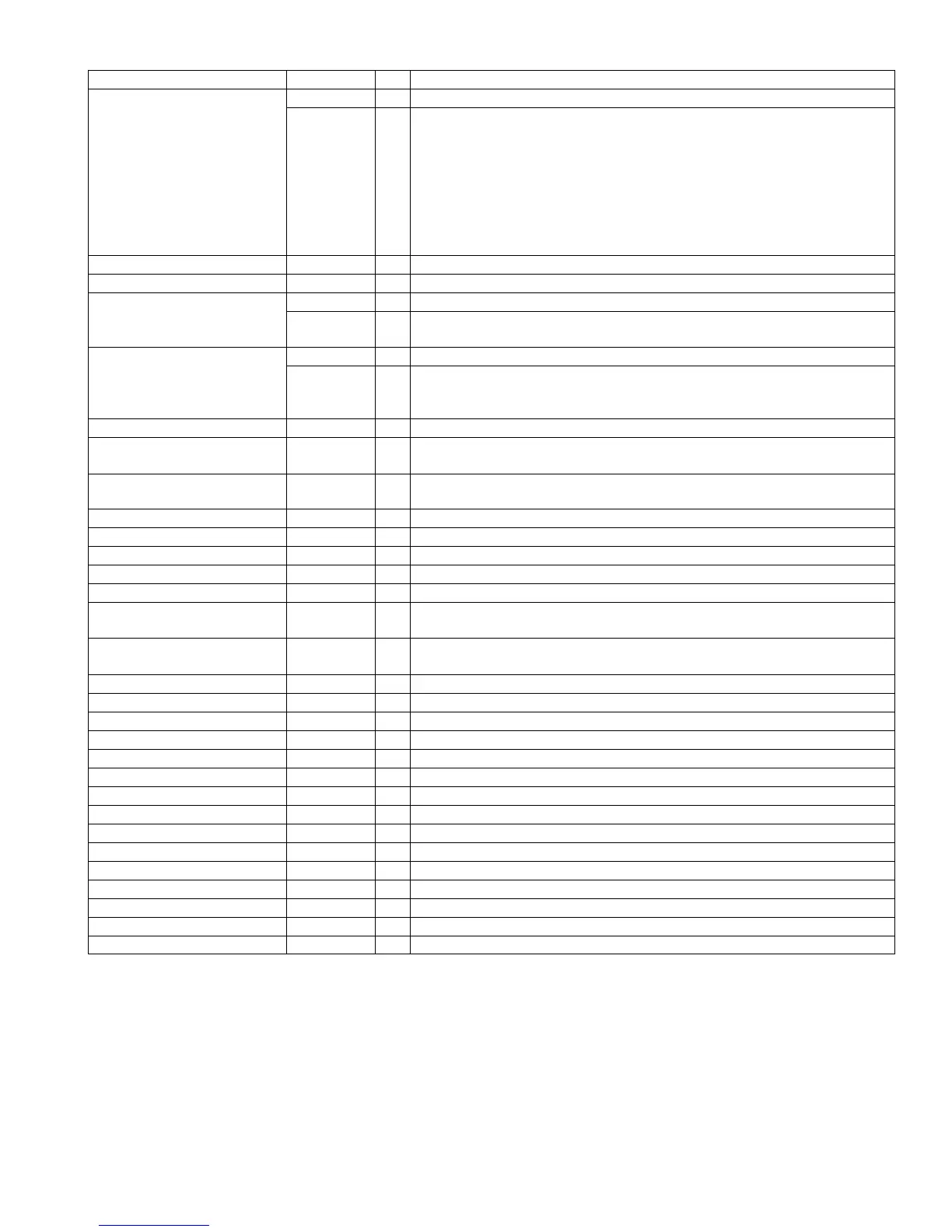

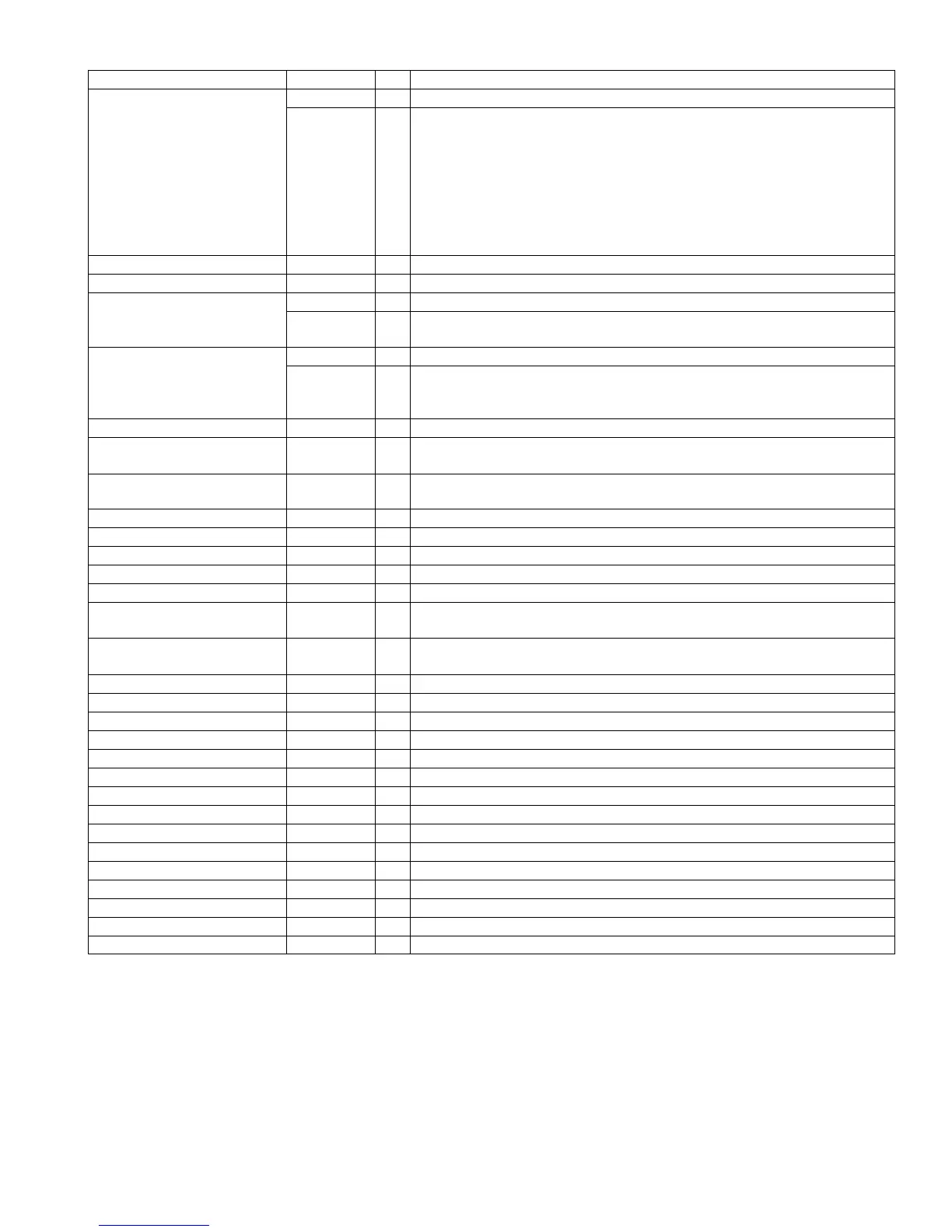

(No.49837)1-31

23 RWS O Dual-purpose pin RWS is the audio frame sync.

SEL_PLL1 I Pins SEL_PLL[1.0] select the PLL clock frequency for the DCLK output.

SEL_PLL1 SEL_PLL0 DCLK

0 0 Bypass PLL(input mode)

0 0 27 MHz(output mode)

1 0 32.4 MHz(output mode)

1 1 40.5 MHz(output mode)

24 RSTOUT_B O Reset output(active-low).

2:4,27:30,76 NC No connect.Do not connect to these pins.

33 RSD O Dual-purpose pin. RSD is the receive audio data input.

SEL_PLL0 I SEL_PLL0 along with SEL_PLL1 select the PLL clock frequency for the

DCLK output.See the table for pin number 23.

37 RBCK O Dual-purpose pin.RBCK is the receive audio bit clock.

SER_IN I SER_IN is the serial input DSC mode.

0-Parallel DSC mode.

1-Serial DSC mode.

41,51 VSSAA I Audio Analog Ground.

42 VCM I ADC Common Mode Reference(CMR) buffer output.CMR is approximately

2.25V.Bypass to analog ground with 47µF electrolytic in parallel with 0.1µF.

43 VREFP I DAC and ADC maximum reference.

Bypass to VCMR with 10µF in parallel with 0.1µF.

44 VCCAA I Analog VCC, 5V.

45:46 AOR+,AOR- O Right channel output.

47:48 AOL-,AOL+ O Left channel input.

49 MIC1 I Microphone input 1.

50 MIC2 I Microphone 2.

52 VREF I Internal resistor divider generates Common Mode Reference(CMR) voltage.

Bypass to analog ground with 0.1µF.

53 VREFM I DAC and ADC minimum reference.

Bypass to VCMR with 10µF in parallel with 0.1µF.

54 RSET I Full scale DAC current adjustment.

55 COMP I Compensation pin.

56:57,62:63 VSSAV I Video Analog Ground

58 CDAC O Modulates chrominance output.

59,60 VCCAV I Video VCC, 5V

61 YDAC O Y Iuminance data bus for screen video port.

64 VDAC O Composite video output.

65 ACAP I Audio CAP.

71 XOUT O Crystal output.

74 XIN I 27 MHz crystal input.

79 PCLK I/O 13.5 MHz pixel clock.

80 2XPCLK I/O 27 MHz(2 times pixel clock).

82 HSYN_B O Horizontal sync(active-low).

84 VSYN_B O Vertical sunc(active-low).

86:89,92,94,96,98 YUV[7:0] I YUV data bus for screen video port.

Pin No. Symbol I/O Function

Loading...

Loading...