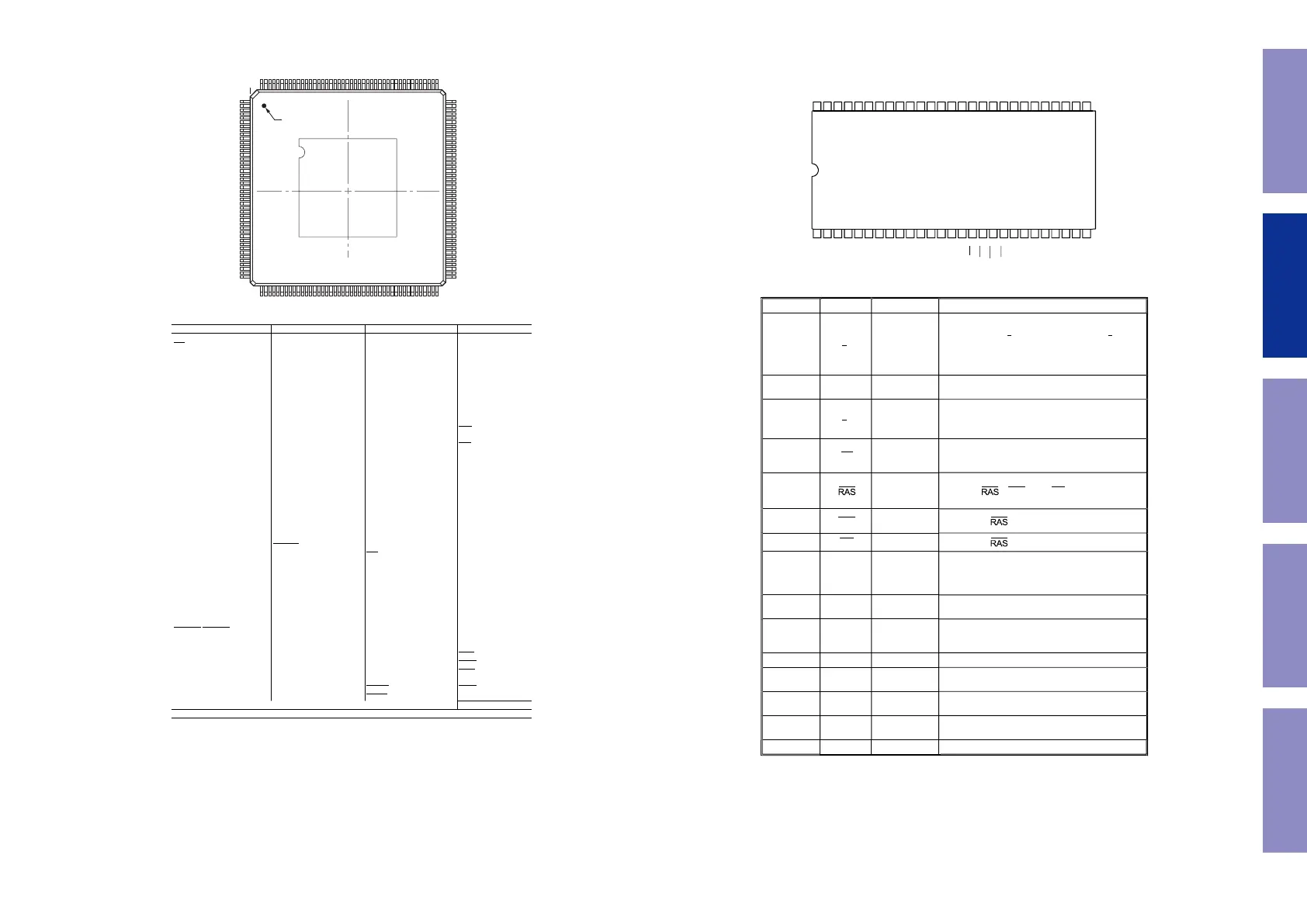

ADSP21487KSWZ-2B (DIGITAL : U1021)

TOP VIEW

(PINS DOWN)

1

44

45

89

88

132

176

133

PIN 1

GND PAD

(PIN 177)

at BOTTOM

Pin Name Pin No. Pin Name Pin No. Pin Name Pin No. Pin Name Pin No.

SDDQM 1 V

DD

_

EXT

45 DAI_P10 89 V

DD

_

INT

133

MS0

2 DPI_P08 46 V

DD

_

INT

90 FLAG0 134

SDCKE 3 DPI_P07 47 V

DD

_

EXT

91 FLAG1 135

V

DD

_

INT

4 V

DD

_

INT

48 DAI_P20 92 FLAG2 136

CLK_CFG1 5 DPI_P09 49 V

DD

_

INT

93 NC 137

ADDR0 6 DPI_P10 50 DAI_P08 94 FLAG3 138

BOOT_CFG0 7 DPI_P11 51 DAI_P14 95 NC 139

V

DD

_

EXT

8 DPI_P12 52 DAI_P04 96 NC 140

ADDR1 9 DPI_P13 53 DAI_P18 97 V

DD

_

EXT

141

ADDR2 10 DPI_P14 54 DAI_P17 98 NC 142

ADDR3 11 DAI_P03 55 DAI_P16 99 V

DD

_

INT

143

ADDR4 12 NC 56 DAI_P12 100 TRST

144

ADDR5 13 V

DD

_

EXT

57 DAI_P15 101 NC 145

BOOT_CFG1 14 NC 58 V

DD

_

INT

102 EMU 146

GND 15 NC 59 DAI_P11 103 DATA0 147

ADDR6 16 NC 60 V

DD

_

EXT

104 DATA1 148

ADDR7 17 NC 61 V

DD

_

INT

105 DATA2 149

NC 18 V

DD

_

INT

62 BOOT_CFG2 106 DATA3 150

NC 19 NC 63 V

DD

_

INT

107 TDO 151

ADDR8 20 NC 64 AMI_ACK 108 DATA4 152

ADDR9 21 V

DD

_

INT

65 GND 109 V

DD

_

EXT

153

CLK_CFG0 22 NC 66 THD_M 110 DATA5 154

V

DD

_

INT

23 NC 67 THD_P 111 DATA6 155

CLKIN 24 V

DD

_

INT

68 V

DD

_

THD

112 V

DD

_

INT

156

XTAL 25 NC 69 V

DD

_

INT

113 DATA7 157

ADDR10 26 WDTRSTO

70 V

DD

_

INT

114 TDI 158

SDA10 27 NC 71 MS1

115 SDCLK 159

V

DD

_

EXT

28 V

DD

_

EXT

72 V

DD

_

INT

116 V

DD

_

EXT

160

V

DD

_

INT

29 DAI_P07 73 WDT_CLKO 117 DATA8 161

ADDR11 30 DAI_P13 74 WDT_CLKIN 118 DATA9 162

ADDR12 31 DAI_P19 75 V

DD

_

EXT

119 DATA10 163

ADDR17 32 DAI_P01 76 ADDR23 120 TCK 164

ADDR13 33 DAI_P02 77 ADDR22 121 DATA11 165

V

DD

_

INT

34 V

DD

_

INT

78 ADDR21 122 DATA12 166

ADDR18 35 NC 79 V

DD

_

INT

123 DATA14 167

RESETOUT

/RUNRSTIN 36 NC 80 ADDR20 124 DATA13 168

V

DD

_

INT

37 NC 81 ADDR19 125 V

DD

_

INT

169

DPI_P01 38 NC 82 V

DD

_

EXT

126 DATA15 170

DPI_P02 39 NC 83 ADDR16 127 SDWE

171

DPI_P03 40 V

DD

_

EXT

84 ADDR15 128 SDRAS 172

V

DD

_

INT

41 V

DD

_

INT

85 V

DD

_

INT

129 RESET 173

DPI_P05 42 DAI_P06 86 ADDR14 130 TMS 174

DPI_P04 43 DAI_P05 87 AMI_WR

131 SDCAS 175

DPI_P06 44 DAI_P09 88 AMI_RD

132 V

DD

_

INT

176

GND 177*

* at BOTTOM

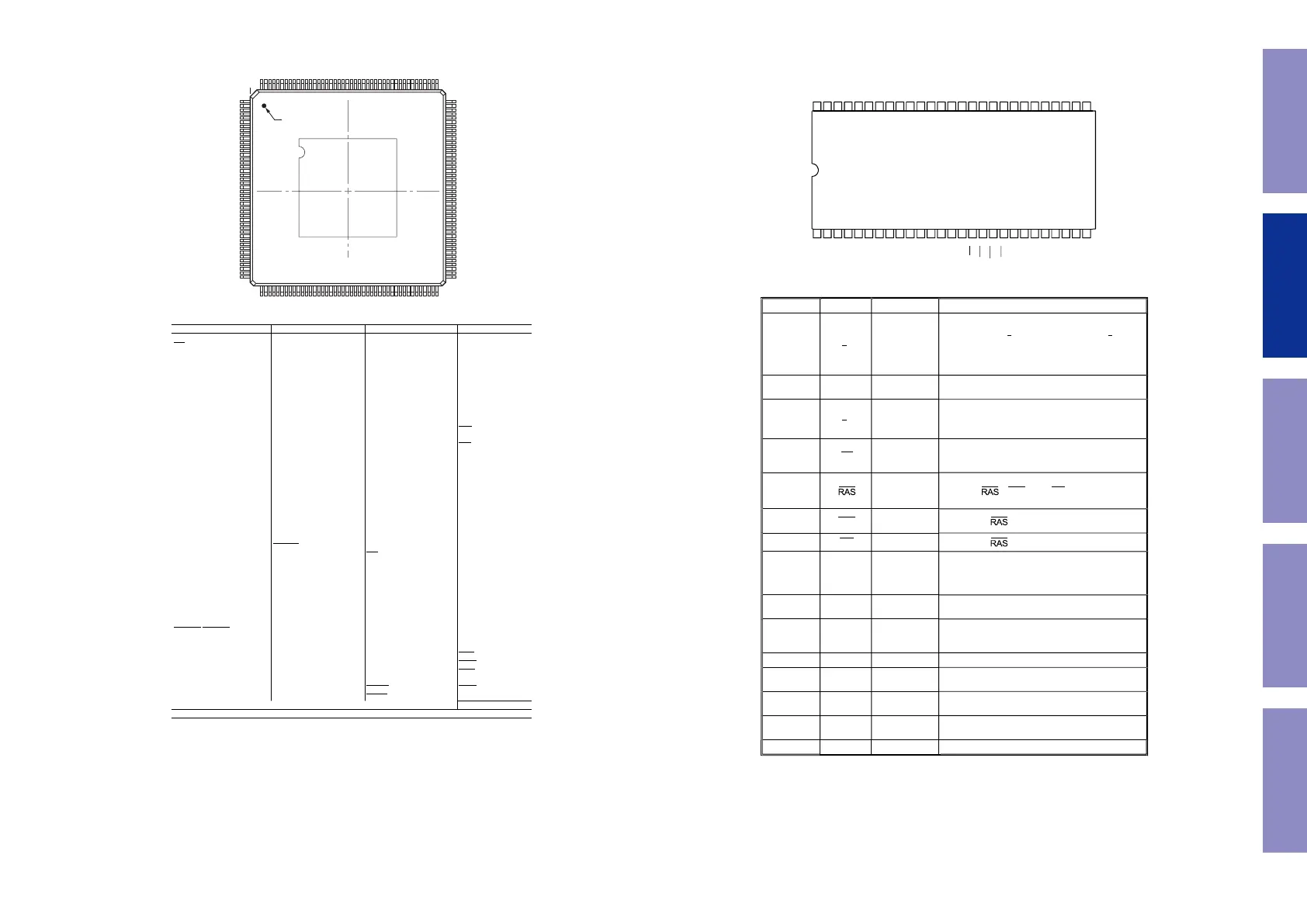

W9864G6KH-6(DIGITAL : U1020)

Pin description

W9864G6KH

Publication Release Date: Nov. 12, 2013

- 4 - Revision A02

4. PIN CONFIGURATION

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

DQ 0

DQ 1

DQ 2

DQ 3

DQ 4

DQ 5

DQ 6

DQ 7

LDQM

CAS

RAS

CS

BS 0

BS 1

A10/ AP

A0

A1

A2

A3

DQ 15

DQ 14

DQ 13

DQ 12

DQ 11

DQ 10

DQ 9

DQ 8

NC

UDQ M

CL K

CKE

NC

A11

A9

A8

A7

A6

A5

A4

VDDQ

VDDQ

VS SQ

VS SQ

VDD

VDD

VSS

VS SQ

VSSQ

VDDQ

VSS

VSS

WE

VDD

VDDQ

W9864G6KH

Publication Release Date: Nov. 12, 2013

- 5 - Revision A02

5. PIN DESCRIPTION

PIN NUMBER PIN NAME FUNCTION DESCRIPTION

23 ~ 26, 22,

29 ~35

A0 A11

Address

Multiplexed pins for row and column address.

Row address: A0

A11. Column address: A0 A7.

A10 is sampled during a precharge command to

determine if all banks are to be precharged or bank

selected by BS0, BS1.

20, 21

BS0, BS1 Bank Select

Select bank to activate during row address latch time,

or bank to read/write during address latch time.

2, 4, 5, 7, 8, 10,

11, 13, 42, 44,

45, 47, 48, 50,

51, 53

DQ0 DQ15

Data

Input/ Output

Multiplexed pins for data output and input.

19

CS

Chip Select

Disable or enable the command decoder. When

command decoder is disabled, new command is

ignored and previous operation continues.

18

Row Address

Strobe

Command input. When sampled at the rising edge of

the clock

,

CA

and

WE

define the

operation to be executed.

17

CAS

Column

Address Strobe

Referred to

16

WE

Write Enable

Referred to

39, 15

UDQM

LDQM

Input/output

mask

The output buffer is placed at Hi-Z (with latency of 2)

when DQM is sampled high in read cycle. In write

cycle, sampling DQM high will block the write

operation with zero latency.

38 CLK Clock Inputs

System clock used to sample inputs on the rising

edge of clock.

37 CKE Clock Enable

CKE controls the clock activation and deactivation.

When CKE is low, Power Down mode, Suspend

mode, or Self Refresh mode is entered.

1, 14, 27 VDD Power Power for input buffers and logic circuit inside DRAM.

28, 41, 54 VSS Ground

Ground for input buffers and logic circuit inside

DRAM.

3, 9, 43, 49 VDDQ

Power for I/O

buffer

Separated power from VDD, to improve DQ noise

immunity.

6, 12, 46, 52 VSSQ

Ground for I/O

buffer

Separated ground from VSS, to improve DQ noise

immunity.

36, 40 NC No Connection No connection.

52

Caution in

servicing

Electrical Mechanical Repair Information Updating

Loading...

Loading...