1-33 1-34

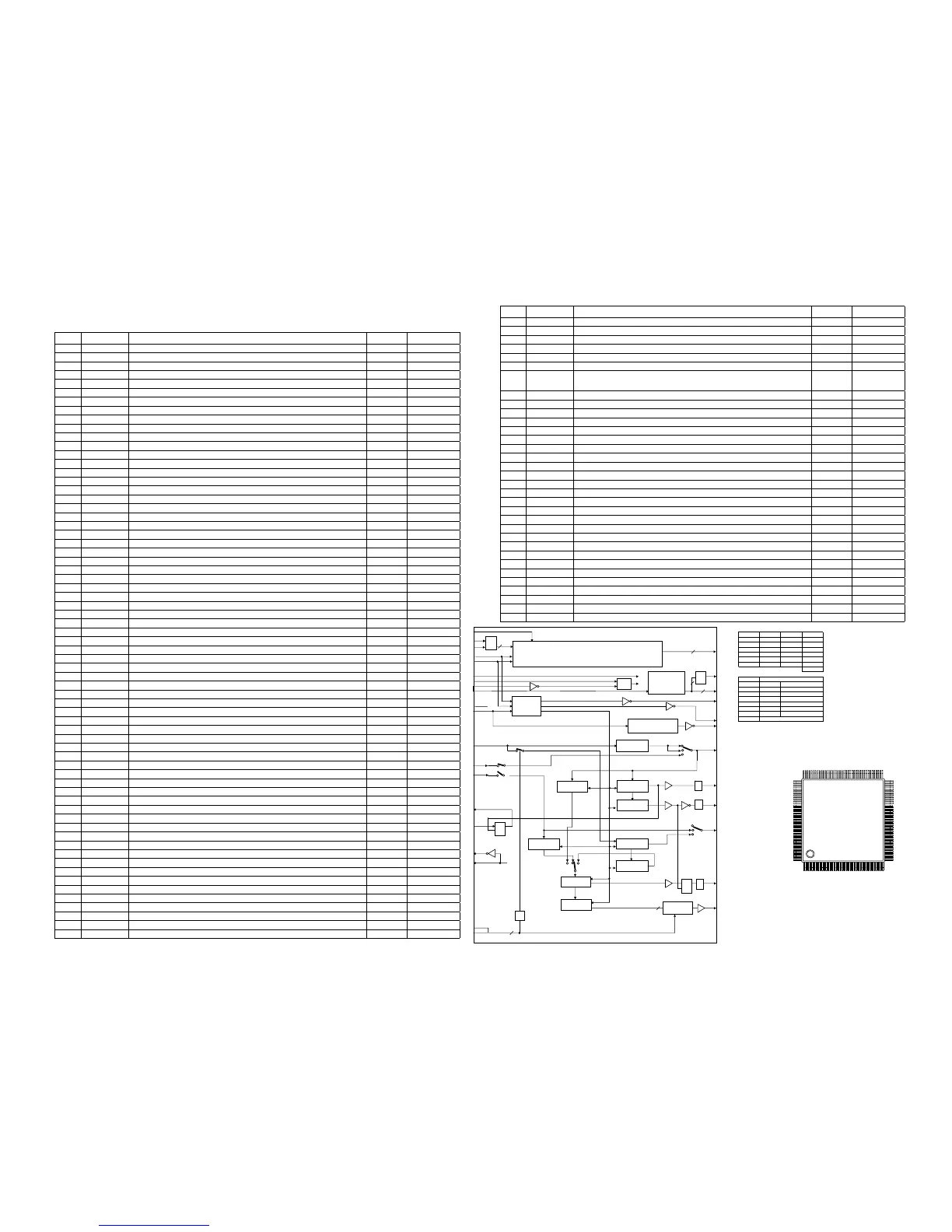

3

MODE

(H=SACD, L=CD) InputX/OutputX

(5=DAPC, 6=SAR)

pin no InputX pin no

OutputX

5, 6

618

SACLO

4

INV

5

DAPC

20

---- 22

SALO

7

LRCK

---- DACLO

88

BCLK

---- DALRO

---- 34

44 SYSO

DSDO

IMDA

9

DSCK

pin no Shift Resister(74HC595)

15

DSCS3

D0

IMD1

36

latchi

DATA

D2

DACRES

D3

NSH

Latch

latout

57

D4

DCF

D5 FILTC

10

Divider Reset

DSPR

59

D6

FILTB

60

D7

FILTA

TIM0

97

55

TIM1

47

81

EXCLK

out 0

EXT=on

768fs

82

40

Xin

CD

SACD

84

clkout

out 1

clkin

384fs

out 2

QA

192fs

DA

out 3

CL

512fs

REG_on

Xon

(H= x'tal on)

AB C

O

out 4

8fs

FSX

A

B

IMDA=EXOR="IMD0,IMD1"

Data Switch

and

7

2

7

Timing

>

DQ

>

DQ

Divider

(8fs)

Divider

(fs,2fs,4fs)

Delay puls

10 - 20msec

2

FSX switch2

3

8bit

Shift Resister

(74HC595)

EXO

R

D0

D1

EXOR

InputX

R

H=on

SW

SW

SW

2

B

A

C

A

C

DividerA

(

1/2)256fs

DividerB 0

DividerB

(1/2)

DividerA

(

1/3)512fs

A=CD, B=SACD,

C=EXT

A=CD, B=SACD,

C=EXT

DividerA

(

1/2)256fs

NOR

DividerB

(1/2)

A=CD, B=SACD,

C=EXT

DividerA

(1/3)256fs

B

O

RESET3

91

88

87

96

43

16

17

80

46

67

45

36

95

55

1

100

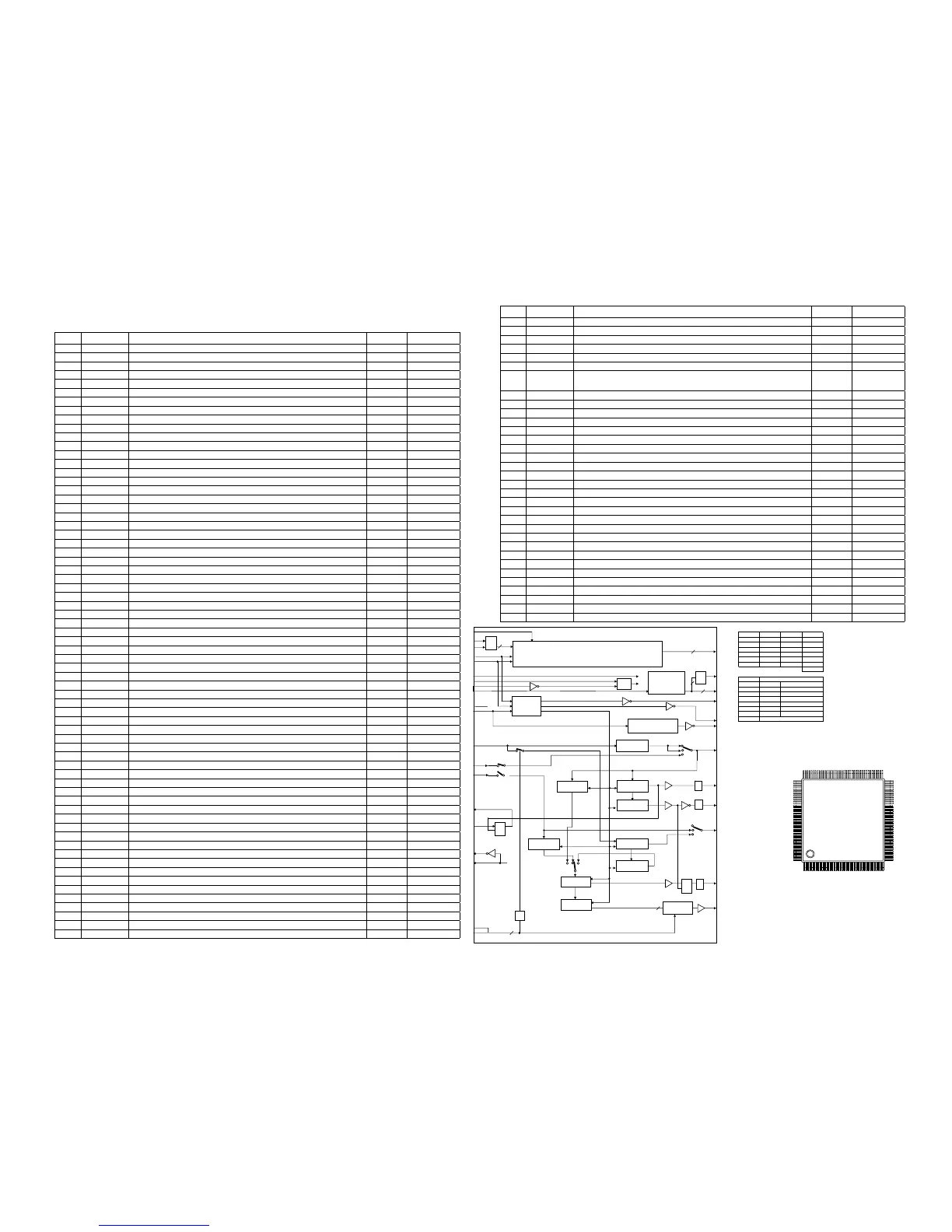

12. MICROPROCESSOR AND IC DATA

Q101 : FPGA XC2S15

Pin no Signal Name Function Pin Usage Pin Name

1 GND GND GND

2 TMS JTAG terminal TMS

3 MODE Mode SW for SACD or CD input(H=SACD, L=CD) IOB

4 D_INV DATA INVERS for SAR & DAPC(H=Correct, L=Invers) IOB IO_VREF_7

5 DAPC DAPC input(SACD : Lch data, CD : PCM data) IOB

6 DARD SACD Rch DATA input IOB

7 DALR Word CLK for CD input IOB

8 DSDO DSDO 8bit serial data signal IOB IO_VREF_7

9 DSCK DSDO data clock signal IOB

10 DSRST1 RESET3 for timing( DIVIDER and DSP,DAC) PCIIOB IO_IRDY

11 GND GND GND

12 VCCO 3.3v Power supply pins for output drivers (subject to banking rules) VCCO

13 CX Power control for TCXO(on/off) IOB IO_TRDY

14 VCCINT 2.5v Power supply pins for the internal core logic. VCCINT

15 DSCS3 DSDO data Chip serect signal IOB

16 CA0 Select signal A for FSX Switch selecter IOB IO_VREF_6

17 CB0 Select signal B fot FSX Switch selecter IOB

18 SACLO SACLO(SACD data CLock output) IOB

19 SYSR System Reset signal & MODE enable from front sub MPU IOB

20 SARO SARO(SACD Rch data output) IOB IO_VREF_6

21 SALO SALO(SACD Lch data output) IOB

22 384F

384fs output for DSP clock

IOB

23 M1 GND(Mode pins are used to specify the configuration mode.) M1

24 GND GND GND

25 M0 GND(Mode pins are used to specify the configuration mode.) M0

26 VCCO 3.3v Power supply pins for output drivers (subject to banking rules) VCCO

27 M2 GND(Mode pins are used to specify the configuration mode.) M2

28 NC NC

29 NC NC

30 DACLO DACLO(PCM data Clock output) IOB IO_VREF_5

31 UNUSED NC IOB

32 DALRO DALRO(PCM data word Clock output) IOB

33 VCCINT 2.5v Power supply pins for the internal core logic. VCCINT

34 DAPCO DAPCO(PCM data output) IOB IO_VREF_5

35 VCCINT 2.5v Power supply pins for the internal core logic. VCCINT

36 LATCH DSDO 8bit data Latch signal input GCLKIOB GCK1

37 VCCO 3.3v Power supply pins for output drivers (subject to banking rules) VCCO

38 GND GND GND

39 GCK0 NC GCLKIOB GCK0

40 x_in 1 SACD Master clk input(67MHz) IOB

41 x_in 2 CD Master clk input(33MHz) IOB IO_VREF_4

42 VCCINT 2.5v Power supply pins for the internal core logic. VCCINT

43 SAON SACD OSC Power supply on IOB

44 SYSO System clock for DAC IOB

45 192FS 192fs output for DSP56364 and SM5866AS IOB IO_VREF_4

46 8FS 8fs output for DSP56364 and SM5866AS IOB

47 DSRST reset3 delayed 20msec for DSP and DAC IOB

48 GND GND GND

49 DONE Connect to ROM(XCF01S)10pin 330 ohm pullup DONE

50 VCCO 3.3v Power supply pins for output drivers (subject to banking rules) VCCO

51 PROGRAM Connect to ROM(XCF01S)7pin 10K ohm pullup PROGRAM

52 IO_INIT Connect to ROM(XCF01S)8pin 3.3K ohm pullup IOB IO_INIT

53 DSP_RST Reset for DSP56364 IOB IO_D7

54 IMD1 output A IOB IO_VREF_3

55 IMDA EX_OR output from SHIFTresistr D0(A),D1(B) IOB

56 N_SH for DSP56364 of Noise shaper on/off IOB IO_D6

57 DC_F for DSP56364 of DC-Filter on/off IOB IO_D5

58 Filter3 for DSP56364 of filter3 control. IOB

59 Filter2 for DSP56364 of filter2 control. IOB IO_VREF_3

60 Filter1 for DSP56364 of filter1 control. IOB IO_D4

61 VCCINT 2.5v Power supply pins for the internal core logic. VCCINT

62 TEST_2 TEST_2 PCIIOB IO_TRDY

63 VCCO 3.3v Power supply pins for output drivers (subject to banking rules) VCCO

64 GND GND GND

65 NC NC PCIIOB IO_IRDY

66 IO_D3 NC IOB IO_D3

67 NC NC IOB IO_VREF_2

Pin no Signal Name Function Pin Usage Pin Name

68 GND To connect GND IOB

69 NC NC IOB IO_D2

70 TEST_3 TEST_3 IOB IO_D1

71 FSIO EXT_Sampling clock(3 fs output) IOB

72 FSI EXT_Sampling clock(3 fs input) IOB IO_VREF_2

73 DOXCF Connect to ROM(XCF01S)1pin IOB IO_DIN_D0

74 IO_DOUT_

BUSY

NC IOB IO_DOUT_

BUSY

75 CCLK Connect to ROM(XCF01S)2pin CCLK

76 VCCO 3.3v Power supply pins for output drivers (subject to banking rules) VCCO

77 TDO JTAG terminal TDO

78 GND GND GND

79 TDI JTAG terminal TDI

80 FSX x_fs output for PLL phase comparater IOB IO_CS

81 EXT_CLK EXT_CLK(1024fs input) IOB IO_WRITE

82 SYCL 768fs output for Engin IOB IO_VREF_1

83 NC NC IOB

84 ECKO SELECT out from Switch (osc_out orEXT_CLK) IOB

85 VCCINT 2.5v Power supply pins for the internal core logic. VCCINT

86 DF-DA DIG input IOB IO_VREF_1

87 DF-QA DIG Reclock out IOB

88 DACL SACD or CD bit clock input GCLKIOB GCK2

89 GND GND GND

90 VCCO 3.3v Power supply pins for output drivers (subject to banking rules) VCCO

91 CKI Clock Input Frequency for divider GCLKIOB GCK3

92 VCCINT 2.5v Power supply pins for the internal core logic. VCCINT

93 NC NC IOB IO_VREF_0

94 VCCINT 2.5v Power supply pins for the internal core logic. VCCINT

95 NC NC IOB

96 EXON for VCXO Power supply control (H=on) IOB

97 timo<0> reset3 delayed 1(1time of fs) IOB IO_VREF_0

98 NC NC IOB

99 TCK JTAG terminal TCK

100 VCCO 3.3v Power supply pins for output drivers (subject to banking rules) VCCO

Loading...

Loading...