38

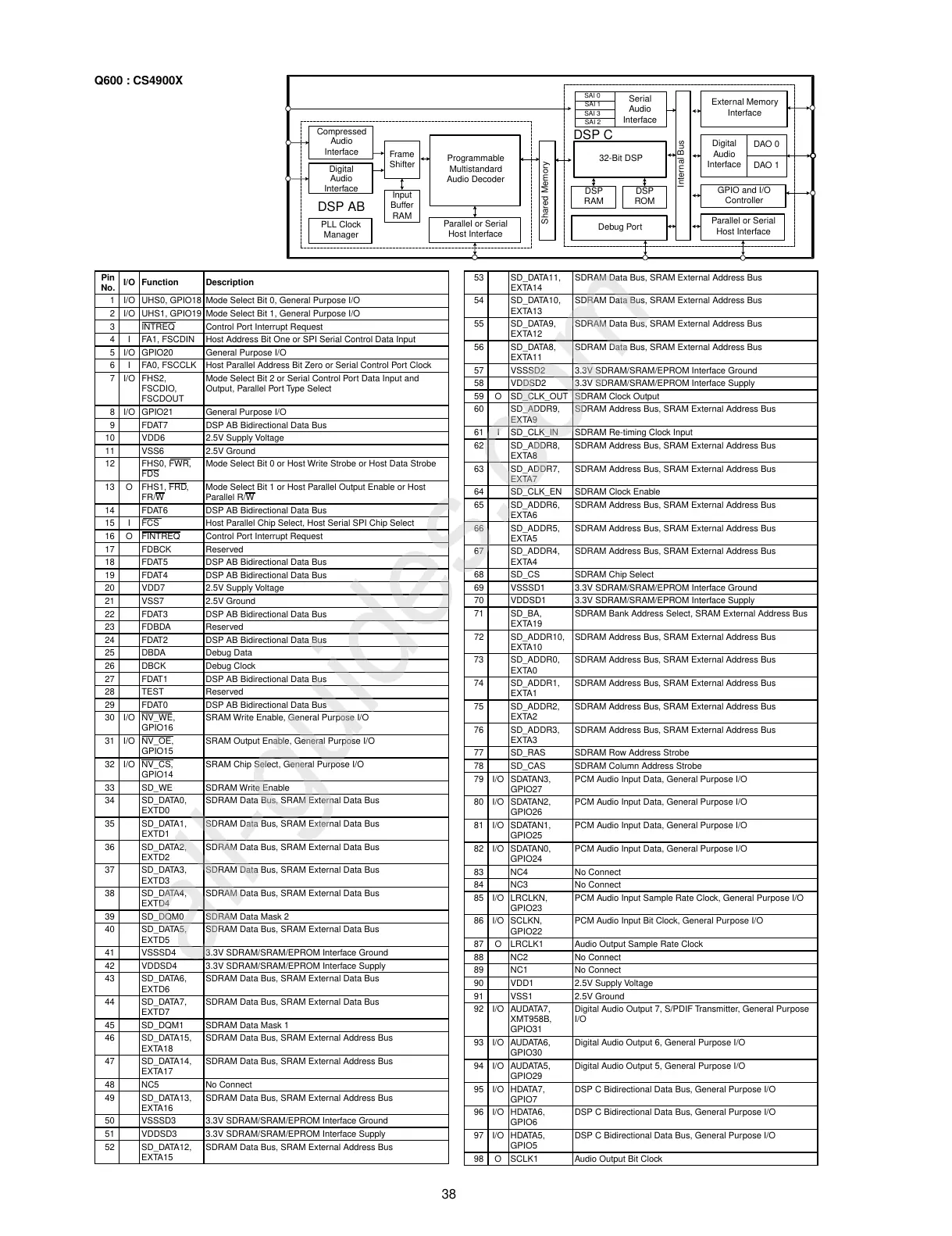

Parallel or Serial

Host Interface

External Memory

Interface

Internal Bus

32-Bit DSP

Programmable

Multistandard

Audio Decoder

Compressed

Audio

Interface

PLL Clock

Manager

Shared Memory

Debug Port

GPIO and I/O

Controller

Digital

Audio

Interface

Digital

Audio

Interface

DSP C

DSP AB

Serial

Audio

Interface

SAI 0

SAI 1

SAI 2

SAI 3

DAO 0

DAO 1

Frame

Shifter

Input

Buffer

RAM

DSP

RAM

DSP

ROM

Parallel or Serial

Host Interface

Q600 : CS4900X

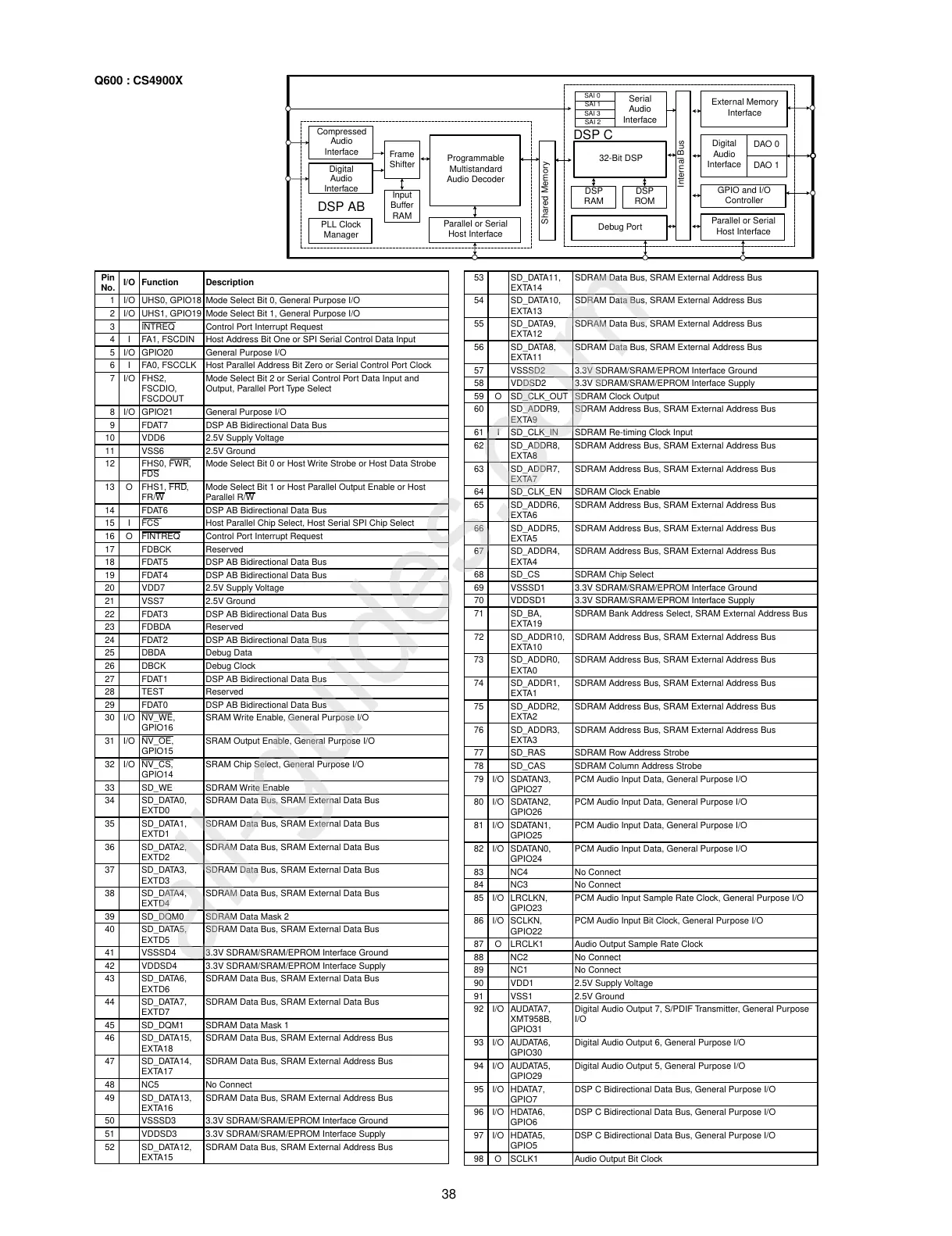

Pin

No.

I/O Function Description

1 I/O UHS0, GPIO18 Mode Select Bit 0, General Purpose I/O

2 I/O UHS1, GPIO19 Mode Select Bit 1, General Purpose I/O

3 INTREQ Control Port Interrupt Request

4 I FA1, FSCDIN Host Address Bit One or SPI Serial Control Data Input

5 I/O GPIO20 General Purpose I/O

6 I FA0, FSCCLK Host Parallel Address Bit Zero or Serial Control Port Clock

7 I/O FHS2,

FSCDIO,

FSCDOUT

Mode Select Bit 2 or Serial Control Port Data Input and

Output, Parallel Port Type Select

8 I/O GPIO21 General Purpose I/O

9 FDAT7 DSP AB Bidirectional Data Bus

10 VDD6 2.5V Supply Voltage

11 VSS6 2.5V Ground

12 FHS0, FWR,

FDS

Mode Select Bit 0 or Host Write Strobe or Host Data Strobe

13 O FHS1, FRD,

FR/W

Mode Select Bit 1 or Host Parallel Output Enable or Host

Parallel R/W

14 FDAT6 DSP AB Bidirectional Data Bus

15 I FCS Host Parallel Chip Select, Host Serial SPI Chip Select

16 O FINTREQ Control Port Interrupt Request

17 FDBCK Reserved

18 FDAT5 DSP AB Bidirectional Data Bus

19 FDAT4 DSP AB Bidirectional Data Bus

20 VDD7 2.5V Supply Voltage

21 VSS7 2.5V Ground

22 FDAT3 DSP AB Bidirectional Data Bus

23 FDBDA Reserved

24 FDAT2 DSP AB Bidirectional Data Bus

25 DBDA Debug Data

26 DBCK Debug Clock

27 FDAT1 DSP AB Bidirectional Data Bus

28 TEST Reserved

29 FDAT0 DSP AB Bidirectional Data Bus

30 I/O NV_WE,

GPIO16

SRAM Write Enable, General Purpose I/O

31 I/O NV_OE,

GPIO15

SRAM Output Enable, General Purpose I/O

32 I/O NV_CS,

GPIO14

SRAM Chip Select, General Purpose I/O

33 SD_WE SDRAM Write Enable

34 SD_DATA0,

EXTD0

SDRAM Data Bus, SRAM External Data Bus

35 SD_DATA1,

EXTD1

SDRAM Data Bus, SRAM External Data Bus

36 SD_DATA2,

EXTD2

SDRAM Data Bus, SRAM External Data Bus

37 SD_DATA3,

EXTD3

SDRAM Data Bus, SRAM External Data Bus

38 SD_DATA4,

EXTD4

SDRAM Data Bus, SRAM External Data Bus

39 SD_DQM0 SDRAM Data Mask 2

40 SD_DATA5,

EXTD5

SDRAM Data Bus, SRAM External Data Bus

41 VSSSD4 3.3V SDRAM/SRAM/EPROM Interface Ground

42 VDDSD4 3.3V SDRAM/SRAM/EPROM Interface Supply

43 SD_DATA6,

EXTD6

SDRAM Data Bus, SRAM External Data Bus

44 SD_DATA7,

EXTD7

SDRAM Data Bus, SRAM External Data Bus

45 SD_DQM1 SDRAM Data Mask 1

46 SD_DATA15,

EXTA18

SDRAM Data Bus, SRAM External Address Bus

47 SD_DATA14,

EXTA17

SDRAM Data Bus, SRAM External Address Bus

48 NC5 No Connect

49 SD_DATA13,

EXTA16

SDRAM Data Bus, SRAM External Address Bus

50 VSSSD3 3.3V SDRAM/SRAM/EPROM Interface Ground

51 VDDSD3 3.3V SDRAM/SRAM/EPROM Interface Supply

52 SD_DATA12,

EXTA15

SDRAM Data Bus, SRAM External Address Bus

53 SD_DATA11,

EXTA14

SDRAM Data Bus, SRAM External Address Bus

54 SD_DATA10,

EXTA13

SDRAM Data Bus, SRAM External Address Bus

55 SD_DATA9,

EXTA12

SDRAM Data Bus, SRAM External Address Bus

56 SD_DATA8,

EXTA11

SDRAM Data Bus, SRAM External Address Bus

57 VSSSD2 3.3V SDRAM/SRAM/EPROM Interface Ground

58 VDDSD2 3.3V SDRAM/SRAM/EPROM Interface Supply

59 O SD_CLK_OUT SDRAM Clock Output

60 SD_ADDR9,

EXTA9

SDRAM Address Bus, SRAM External Address Bus

61 I SD_CLK_IN SDRAM Re-timing Clock Input

62 SD_ADDR8,

EXTA8

SDRAM Address Bus, SRAM External Address Bus

63 SD_ADDR7,

EXTA7

SDRAM Address Bus, SRAM External Address Bus

64 SD_CLK_EN SDRAM Clock Enable

65 SD_ADDR6,

EXTA6

SDRAM Address Bus, SRAM External Address Bus

66 SD_ADDR5,

EXTA5

SDRAM Address Bus, SRAM External Address Bus

67 SD_ADDR4,

EXTA4

SDRAM Address Bus, SRAM External Address Bus

68 SD_CS SDRAM Chip Select

69 VSSSD1 3.3V SDRAM/SRAM/EPROM Interface Ground

70 VDDSD1 3.3V SDRAM/SRAM/EPROM Interface Supply

71 SD_BA,

EXTA19

SDRAM Bank Address Select, SRAM External Address Bus

72 SD_ADDR10,

EXTA10

SDRAM Address Bus, SRAM External Address Bus

73 SD_ADDR0,

EXTA0

SDRAM Address Bus, SRAM External Address Bus

74 SD_ADDR1,

EXTA1

SDRAM Address Bus, SRAM External Address Bus

75 SD_ADDR2,

EXTA2

SDRAM Address Bus, SRAM External Address Bus

76 SD_ADDR3,

EXTA3

SDRAM Address Bus, SRAM External Address Bus

77 SD_RAS SDRAM Row Address Strobe

78 SD_CAS SDRAM Column Address Strobe

79 I/O SDATAN3,

GPIO27

PCM Audio Input Data, General Purpose I/O

80 I/O SDATAN2,

GPIO26

PCM Audio Input Data, General Purpose I/O

81 I/O SDATAN1,

GPIO25

PCM Audio Input Data, General Purpose I/O

82 I/O SDATAN0,

GPIO24

PCM Audio Input Data, General Purpose I/O

83 NC4 No Connect

84 NC3 No Connect

85 I/O LRCLKN,

GPIO23

PCM Audio Input Sample Rate Clock, General Purpose I/O

86 I/O SCLKN,

GPIO22

PCM Audio Input Bit Clock, General Purpose I/O

87 O LRCLK1 Audio Output Sample Rate Clock

88 NC2 No Connect

89 NC1 No Connect

90 VDD1 2.5V Supply Voltage

91 VSS1 2.5V Ground

92 I/O AUDATA7,

XMT958B,

GPIO31

Digital Audio Output 7, S/PDIF Transmitter, General Purpose

I/O

93 I/O AUDATA6,

GPIO30

Digital Audio Output 6, General Purpose I/O

94 I/O AUDATA5,

GPIO29

Digital Audio Output 5, General Purpose I/O

95 I/O HDATA7,

GPIO7

DSP C Bidirectional Data Bus, General Purpose I/O

96 I/O HDATA6,

GPIO6

DSP C Bidirectional Data Bus, General Purpose I/O

97 I/O HDATA5,

GPIO5

DSP C Bidirectional Data Bus, General Purpose I/O

98 O SCLK1 Audio Output Bit Clock

Loading...

Loading...