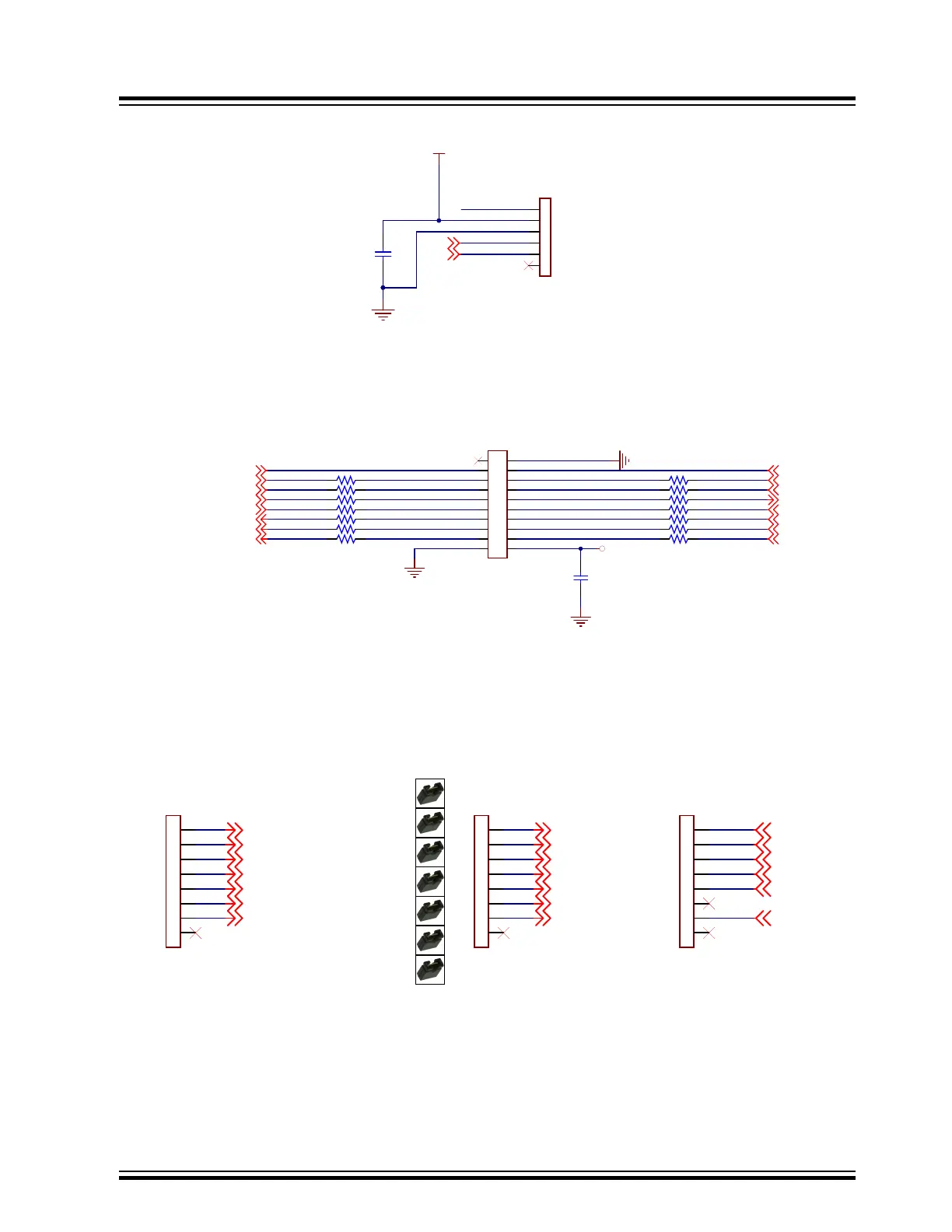

Figure 7-18. CPU JTAG Header

CPU_JTAG

RST_N

GND

3V3_IO

P1_2

P1_3

EMUD_CPU

EMUC_CPU

0.1uF

16V

0603

C311

1

2

3

4

5

6

HDR-2.54 Male 1x6

J301

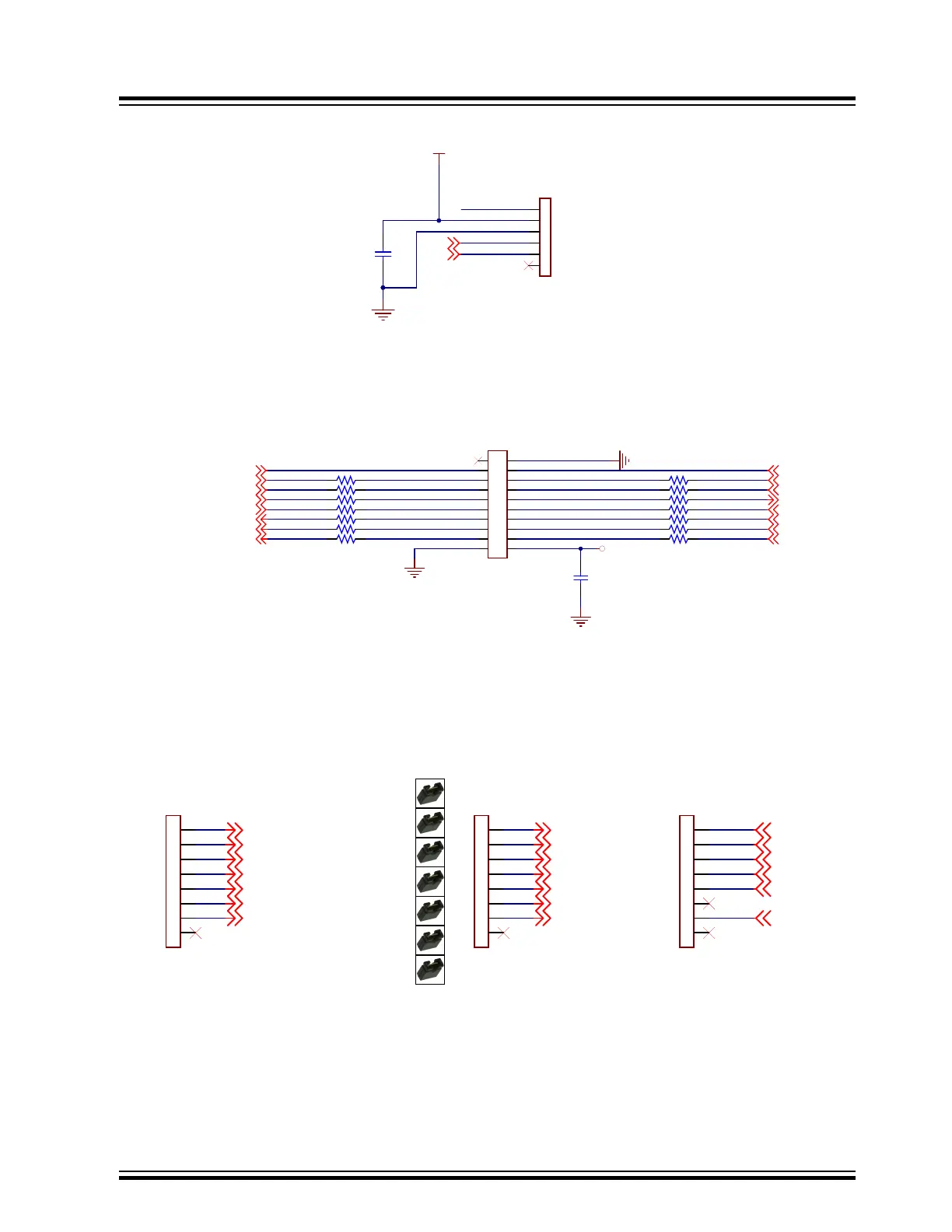

Figure 7-19. XPRO Header

XPRO_INTERFACE

3V3_IO

Xplained Pro standar d extension header

I2C_SDA I2C_SCL

UART_RX UART_TX

SPI_SS_A SPI_MOSI

SPI_MISO SPI_SCK

IRQ/GPIO SPI_SS_B/GPIO

0R 0603R309

0R 0603R314

0R 0603R312

0R 0603R315

0R 0603R310

0R 0603R317

0R 0603R319

0R 0603R316

0R 0603R318

0R 0603R313

4.7uF

6.3V

0603

C302

SK2_KEY_AD

HOST_WAKEUP

UART_RTS

CHIP_EN

IRQN

SPI_SSN

BT_UART1_TXD

SPI_MISO

HCI_TXDHCI_RXD

P0_6

0R 0603R324

SK1_AMB_DET

GPIO_1 GPIO_2

I2C_SDA I2C_SCL

GPIO_1 GPIO_2

ADC+ ADC-

SK1_AMB_DETSK2_KEY_AD

PWM

PWM+

P1_6

P3_5

P0_7

P2_3

P2_6

P0_0

0R 0603R326 0R 0603R327

0R 0603R328

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

HDR-2.54 Male 2x10 RA Rotated 180

J304

Figure 7-20. Button Control Jumper

MCU_VOL_UP

MCU_FWD

MCU_REV

MCU_VOL_DN

PAIRING_MCU

MCU_PLAY/PAUSE

12345678

HDR-2.54 Male 1x8

J700

12345678

HDR-2.54 Male 1x8

J702

VOL_UP

FWD

REV

VOL_DN

PAIRING

PLAY/PAUSE

12345678

HDR-2.54 Male 1x8

J701

BUTTON CO-USE JUMPER

MCU BUTTON BM8X_CARRIER_BOARD

CAD Note:

Place these 3 headers close to each other

J 701<-->J 702 Default Configur ation

J 701<-->J 700 For MCU Button Contr ol

P0_2

P0_3

P0_5

P2_7

P0_1

MCU_REC P0_6SELECT

JP702

JP704

JP705

JP706

JP703

JP701

JP700

BM83 EVB

Appendix A: BM83 EVB Reference Schematics

© 2019 Microchip Technology Inc.

User Guide

DS50002902A-page 52

Loading...

Loading...