dsPIC33/PIC24 Family Reference Manual

DS70005340A-page 18 2018 Microchip Technology Inc.

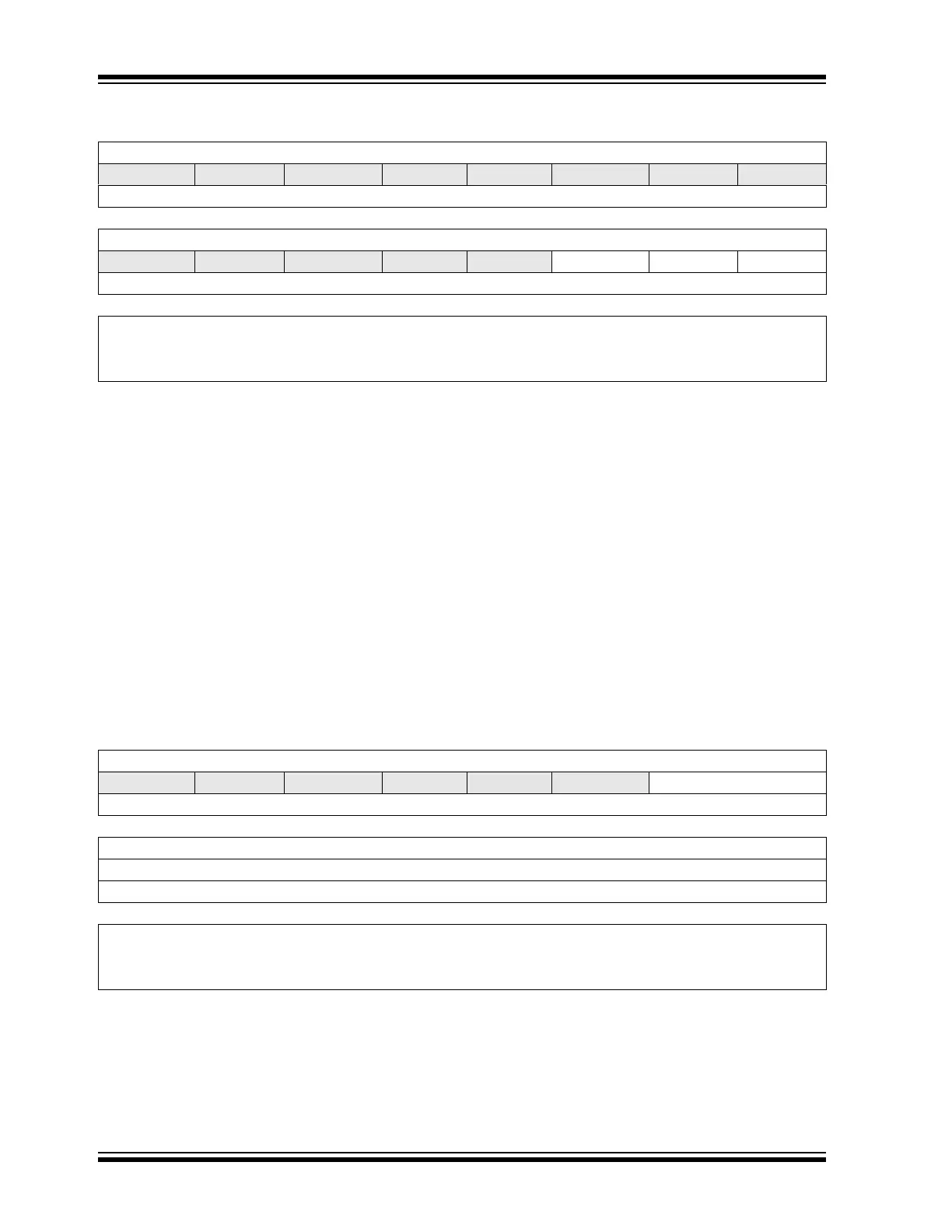

Register 3-11: C1TSCONH: CAN Timestamp Control Register High

U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

bit 15 bit 8

U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0

— — — — — TSRES TSEOF TBCEN

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-3 Unimplemented: Read as ‘0’

bit 2 TSRES: Timestamp Reset bit (CAN FD frames only)

1 = At sample point of the bit following the FDF bit

0 = At sample point of Start-of-Frame (SOF)

bit 1 TSEOF: Timesstamp End-of-Frame (EOF) bit

1 = Timestamp when frame is taken valid (11898-1 10.7):

- RX no error until last, but one bit of EOF

- TX no error until the end of EOF

0 = Timestamp at “beginning” of frame:

- Classical Frame: At sample point of SOF

- FD Frame: see TSRES bit

bit 0 TBCEN: Time Base Counter (TBC) Enable bit

1 = Enables TBC

0 = Stops and resets TBC

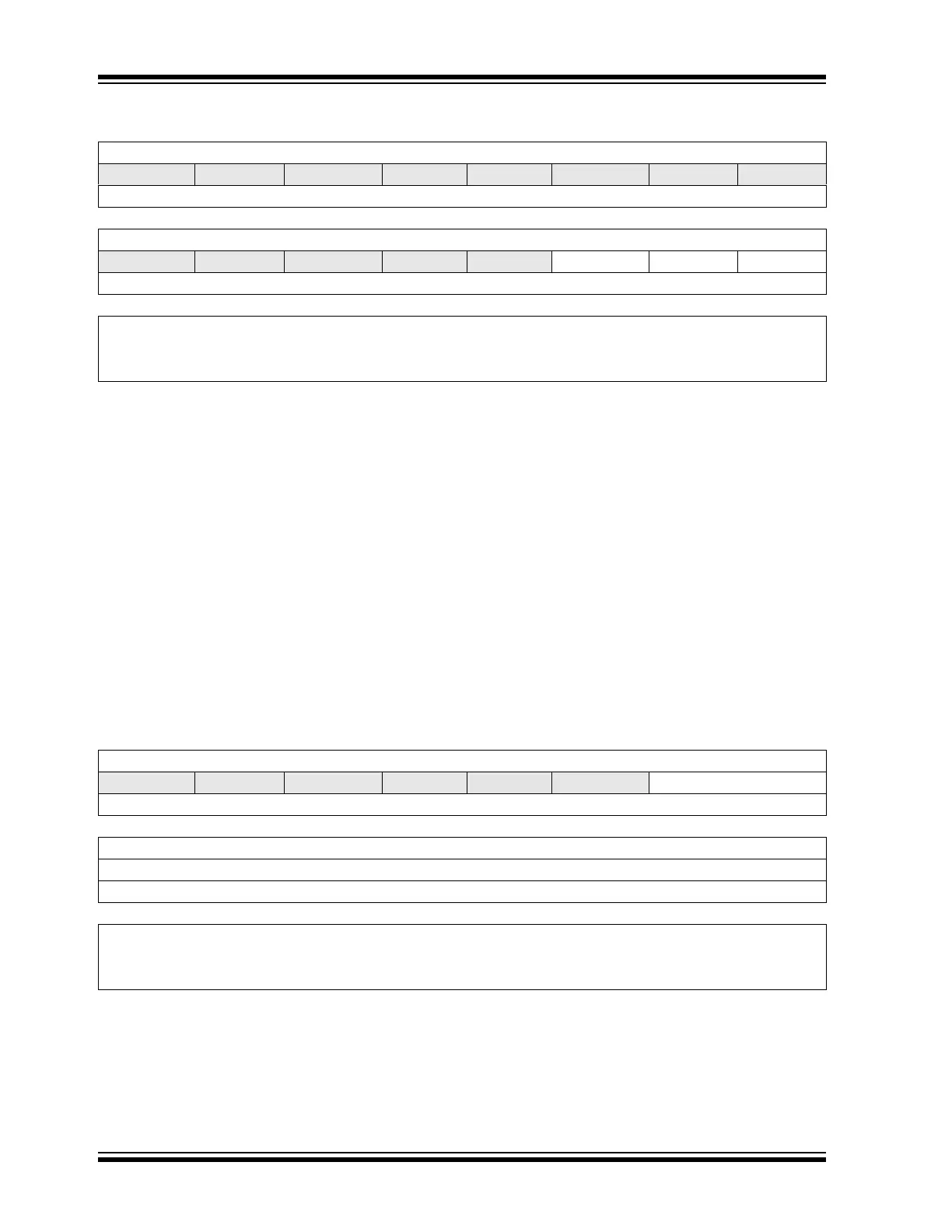

Register 3-12: C1TSCONL: CAN Timestamp Control Register Low

U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-0

— — — — — — TBCPRE<9:8>

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

TBCPRE<7:0>

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-10 Unimplemented: Read as ‘0’

bit 9-0 TBCPRE<9:0>: CAN Time Base Counter Prescaler bits

1023 = TBC increments every 1024 clocks

...

0 = TBC increments every 1 clock

Loading...

Loading...