2018 Microchip Technology Inc. DS70005340A-page 17

CAN FD Protocol Module

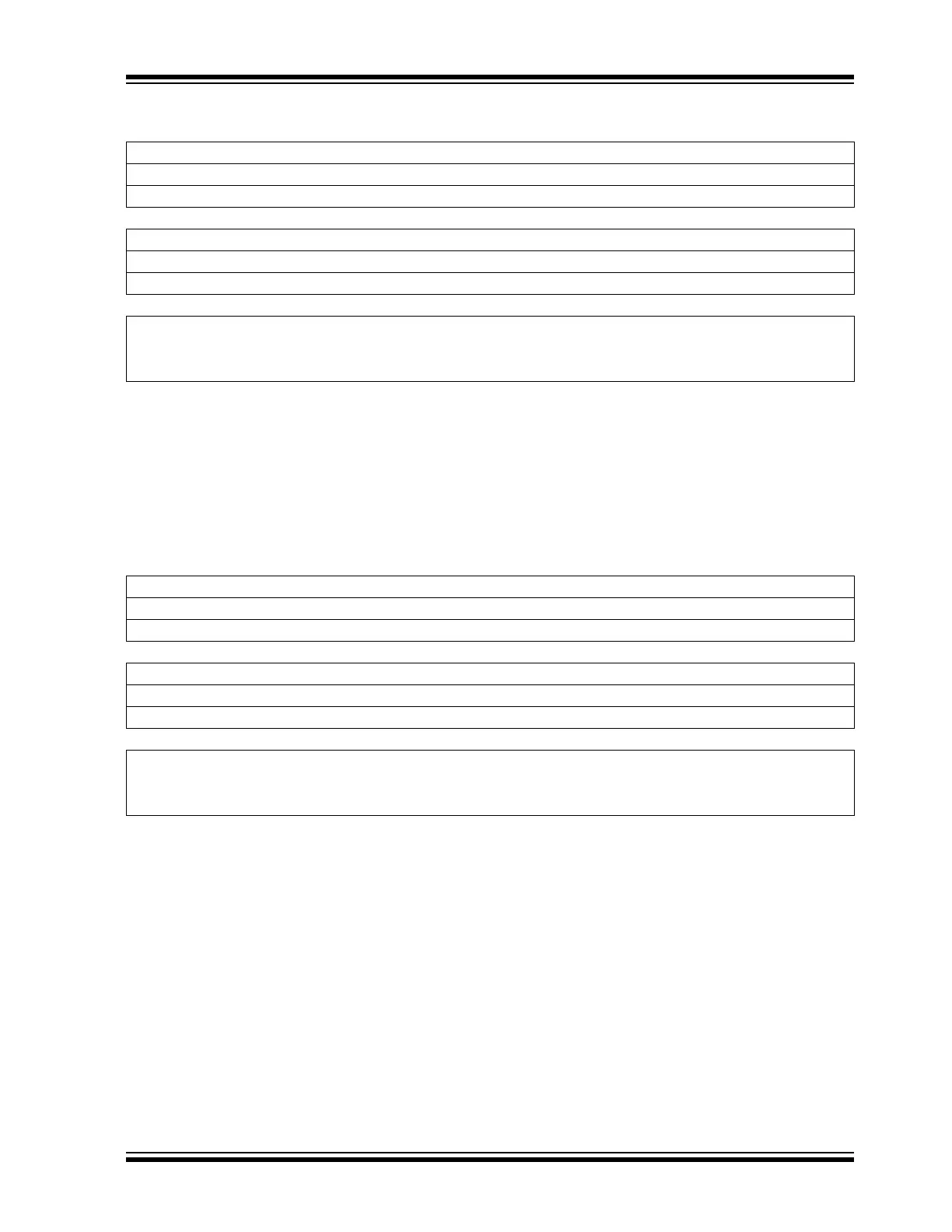

Register 3-9: C1TBCH: CAN Time Base Counter Register High

(1,2)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

TBC<31:24>

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

TBC<23:16>

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-0 TBC<31:16> CAN Time Base Counter bits

This is a free-running timer that increments every TBCPRE<9:0> clock when TBCEN is set.

Note 1: The Time Base Counter (TBC) will be stopped and reset when TBCEN = 0 to save power.

2: The TBC prescaler count will be reset on any write to C1TBCH/L (TBCPREx will be unaffected).

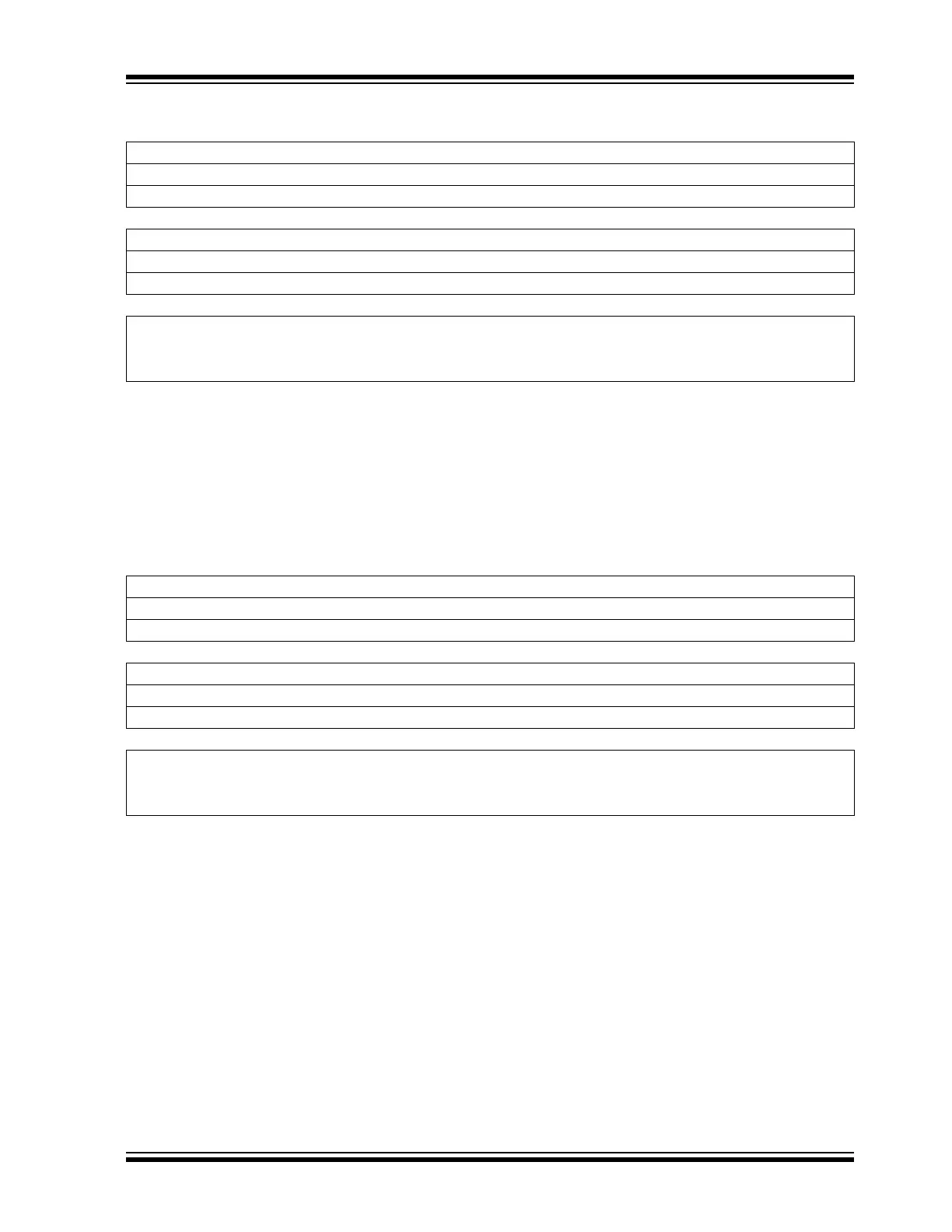

Register 3-10: C1TBCL: CAN Time Base Counter Register Low

(1,2)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

TBC<15:8>

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

TBC<7:0>

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-0 TBC<15:0> CAN Time Base Counter bits

This is a free-running timer that increments every TBCPRE<9:0> clock when TBCEN is set.

Note 1: The TBC will be stopped and reset when TBCEN = 0 to save power.

2: The TBC prescaler count will be reset on any write to C1TBCH/L (TBCPREx will be unaffected).

Loading...

Loading...