dsPIC33/PIC24 Family Reference Manual

DS70005340A-page 16 2018 Microchip Technology Inc.

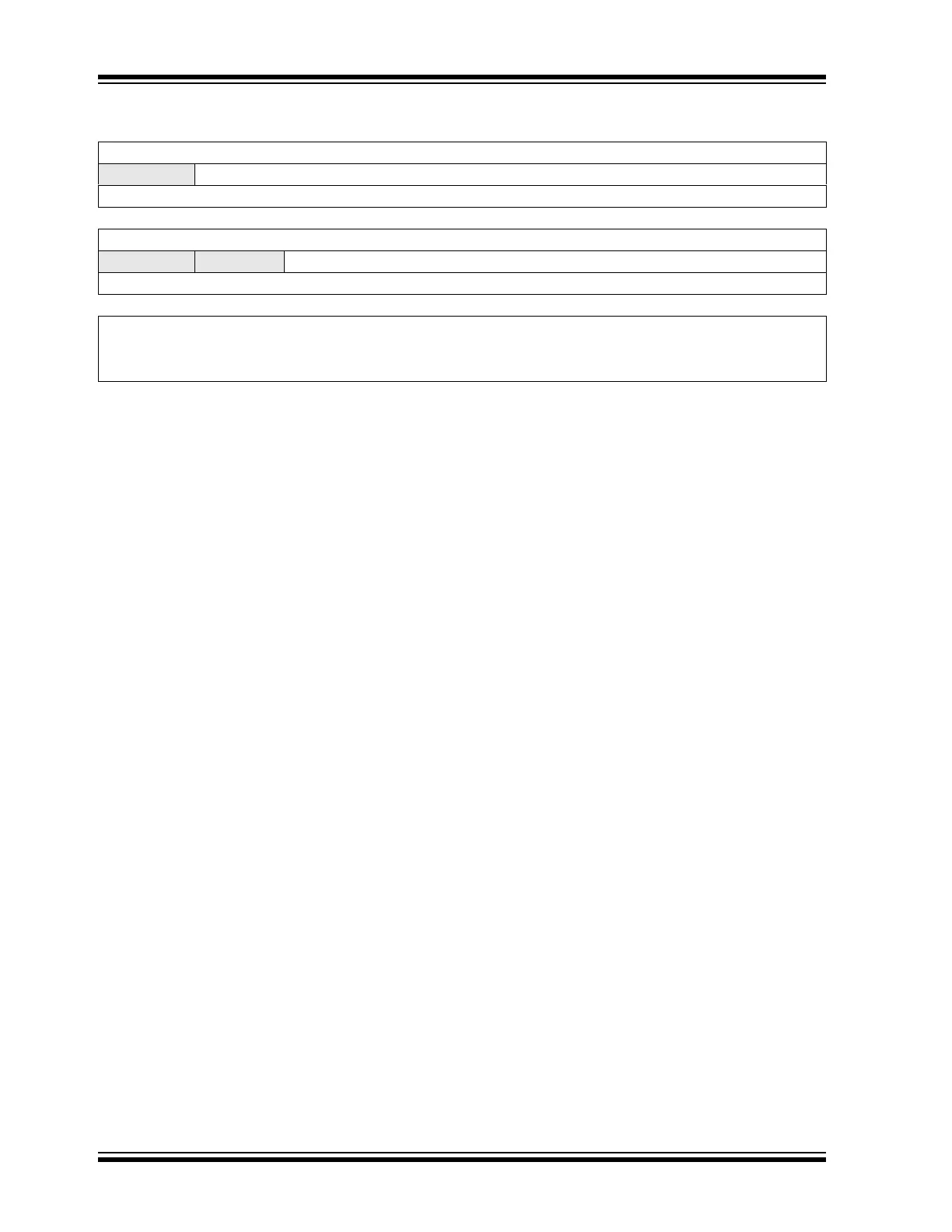

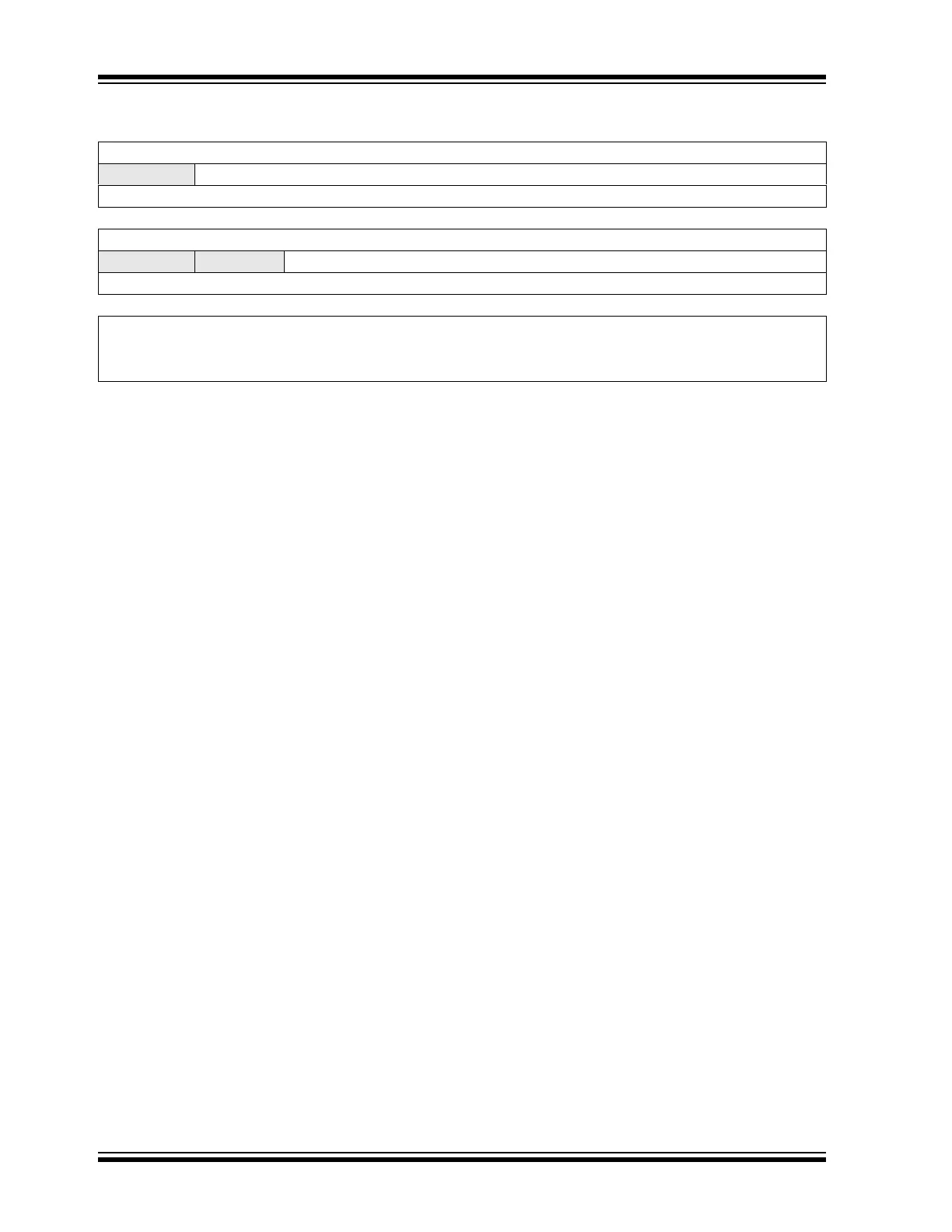

Register 3-8: C1TDCL: CAN Transmitter Delay Compensation Register Low

(1)

U-0 R/W-0 R/W-0 R/W-1 R/W-0 R/W-0 R/W-0 R/W-0

— TDCO<6:0>

bit 15 bit 8

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— — TDCV<5:0>

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as ‘0’

bit 14-8 TDCO<6:0>: Transmitter Delay Compensation Offset bits (Secondary Sample Point (SSP))

111 1111 = -64 x T

CY

...

011 1111 = 63 x T

CY

...

000 0000 = 0 x T

CY

bit 7-6 Unimplemented: Read as ‘0’

bit 5-0 TDCV<5:0>: Transmitter Delay Compensation Value bits (Secondary Sample Point (SSP))

11 1111 = 63 x T

CY

...

00 0000 = 0 x T

CY

Note 1: This register can only be modified in Configuration mode (OPMOD<2:0> = 100).

Loading...

Loading...