2018 Microchip Technology Inc. DS70005340A-page 23

CAN FD Protocol Module

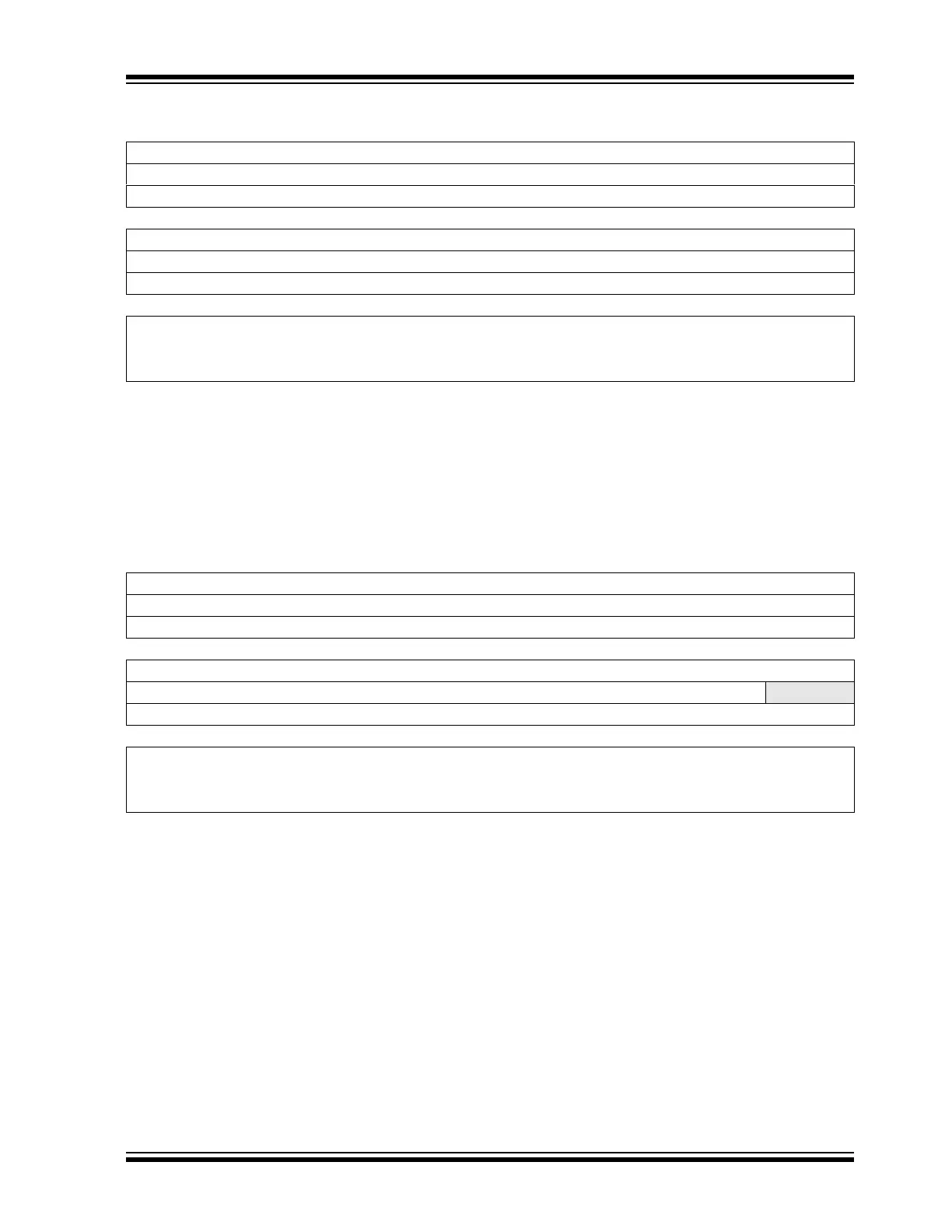

Register 3-17: C1RXIFH: CAN Receive Interrupt Status Register High

(1)

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

RFIF<31:24>

bit 15 bit 8

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

RFIF<23:16>

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-0 RFIF<31:16>: Receive FIFO Interrupt Pending bits

1 = One or more enabled receive FIFO interrupts are pending

0 = No enabled receive FIFO interrupts are pending

Note 1: C1RXIFH: FIFO: RFIFx = ‘or’ of enabled RX FIFO flags (flags need to be cleared in the FIFO register).

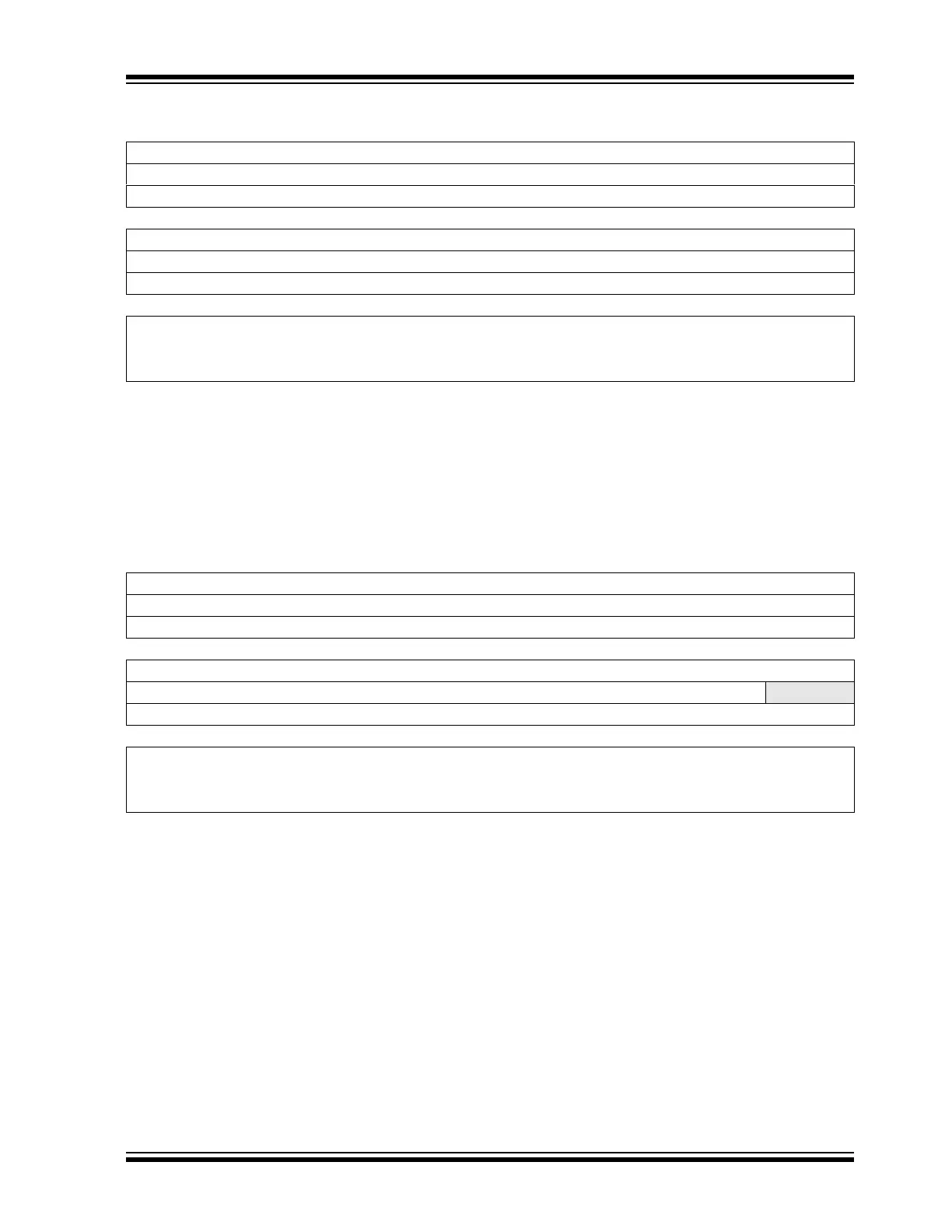

Register 3-18: C1RXIFL: CAN Receive Interrupt Status Register Low

(1)

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

RFIF<15:8>

bit 15 bit 8

R-0 R-0 R-0 R-0 R-0 R-0 R-0 U-0

RFIF<7:1>

—

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-1 RFIF<15:1>: Receive FIFO Interrupt Pending bits

1 = One or more enabled receive FIFO interrupts are pending

0 = No enabled receive FIFO interrupts are pending

bit 0 Unimplemented: Read as ‘0’

Note 1: C1RXIFL: FIFO: RFIFx = ‘or’ of enabled RX FIFO flags (flags need to be cleared in the FIFO register).

Loading...

Loading...