2018 Microchip Technology Inc. DS70005340A-page 39

CAN FD Protocol Module

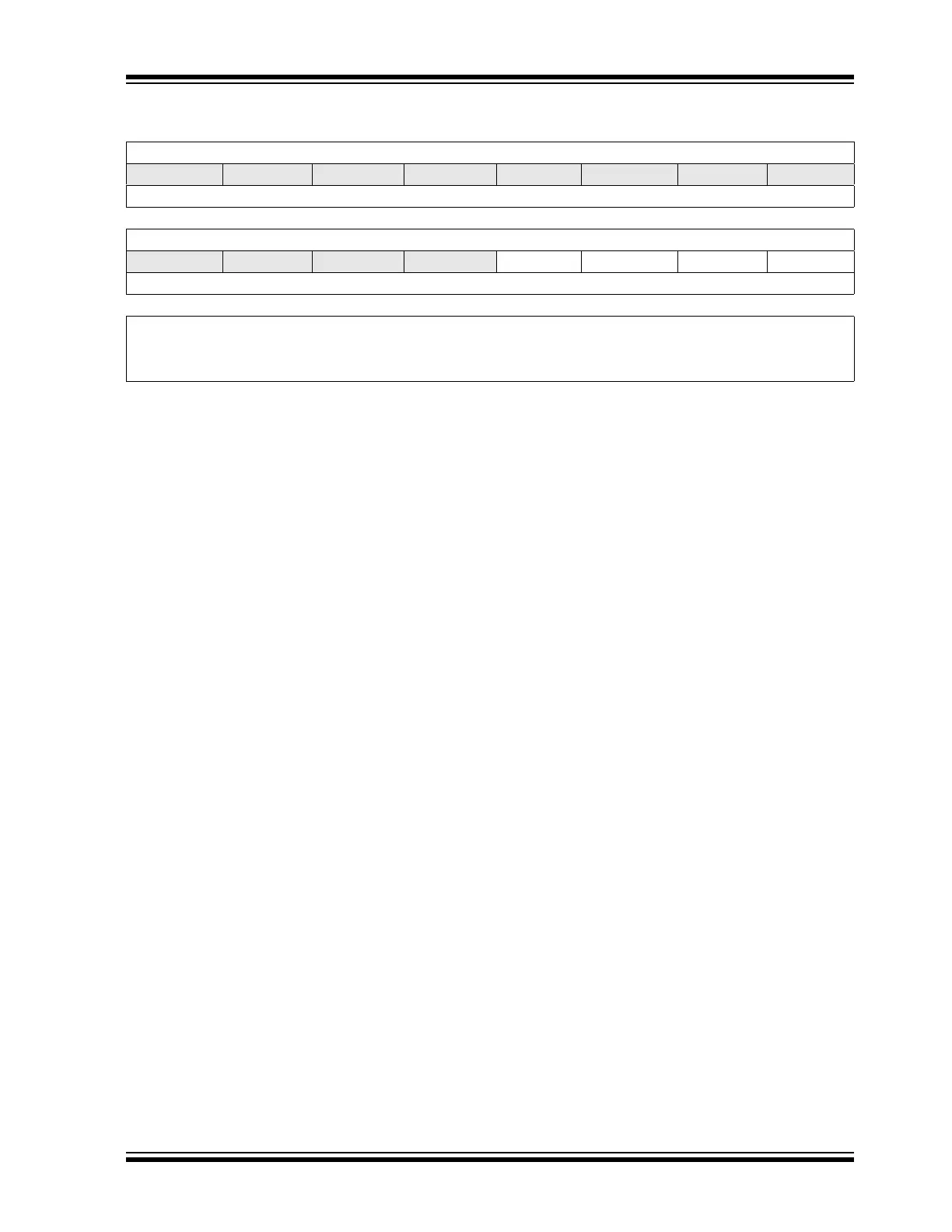

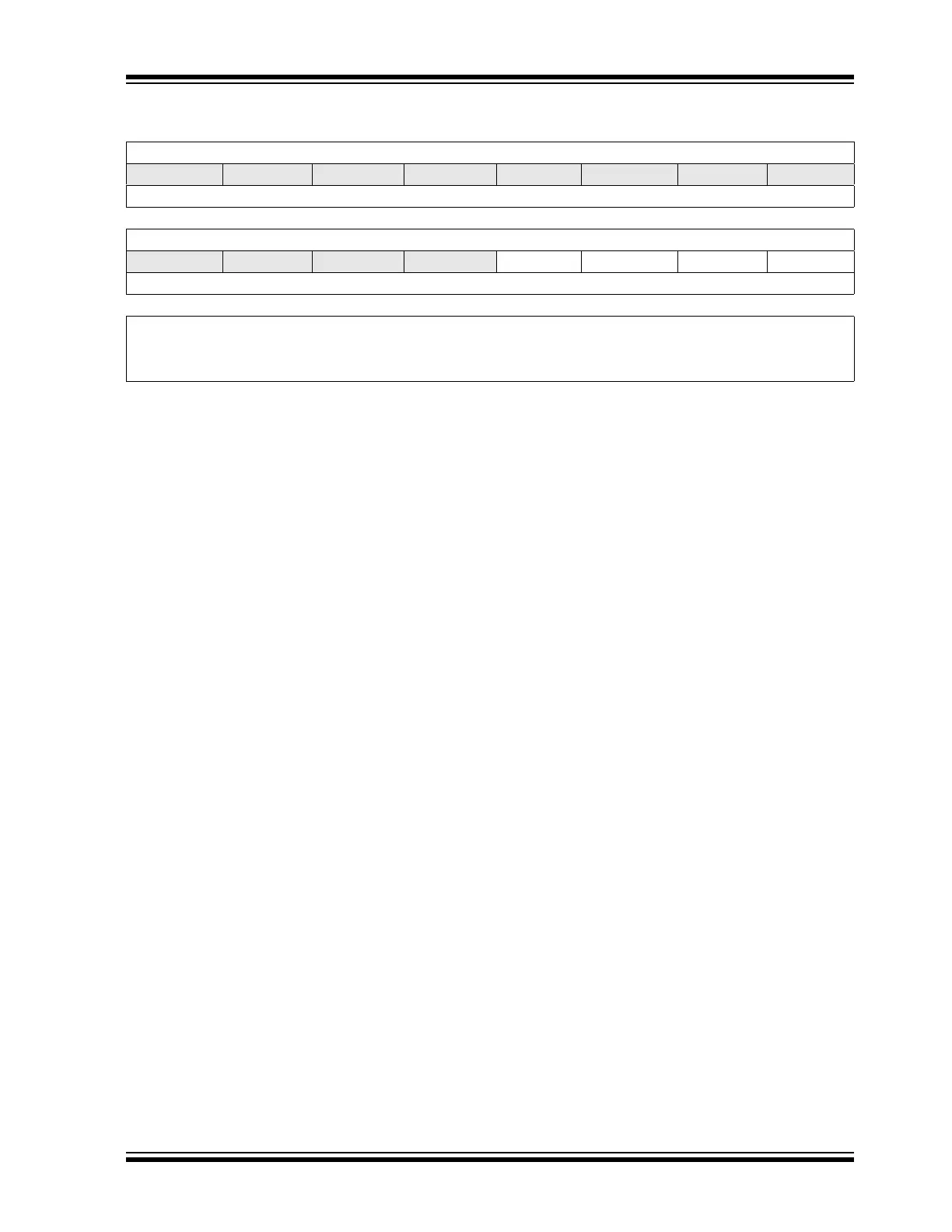

Register 3-37: C1TEFSTA: CAN Transmit Event FIFO Status Register

U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

bit 15 bit 8

U-0 U-0 U-0 U-0 HS/C R-0 R-0 R-0

— — — — TEFOVIF TEFFIF

(1)

TEFHIF

(1)

TEFNEIF

(1)

bit 7 bit 0

Legend: HS = Hardware Settable bit C = Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as ‘0’

bit 3 TEFOVIF: Transmit Event FIFO Overflow Interrupt Flag bit

1 = Overflow event has occurred

0 = No overflow event has occurred

bit 2 TEFFIF: Transmit Event FIFO Full Interrupt Flag bit

(1)

1 = FIFO is full

0 = FIFO is not full

bit 1 TEFHIF: Transmit Event FIFO Half Full Interrupt Flag bit

(1)

1 = FIFO is half full

0 = FIFO is < half full

bit 0 TEFNEIF: Transmit Event FIFO Not Empty Interrupt Flag bit

(1)

1 = FIFO is not empty

0 = FIFO is empty

Note 1: These bits are read-only and reflect the status of the FIFO.

Loading...

Loading...