2018 Microchip Technology Inc. DS70005340A-page 65

CAN FD Protocol Module

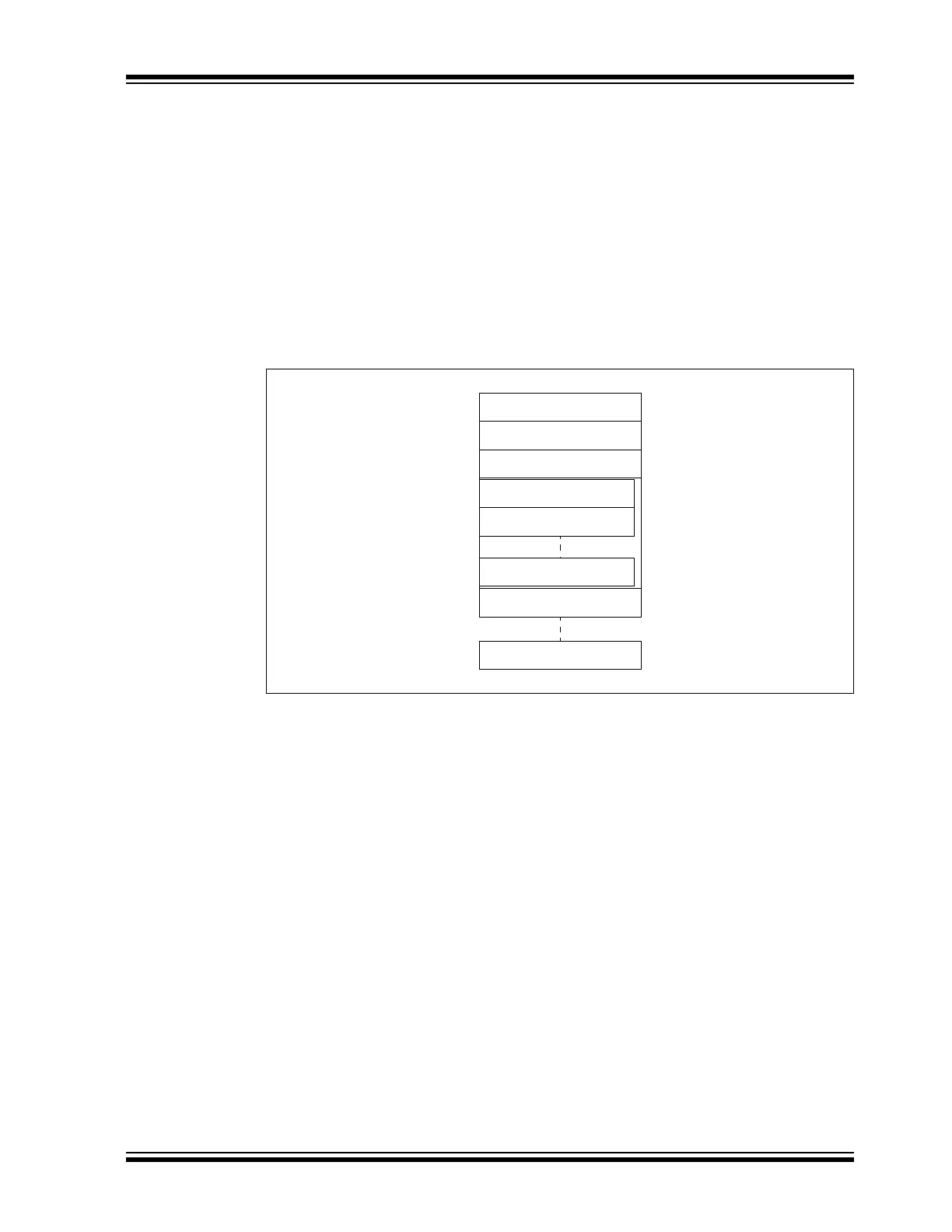

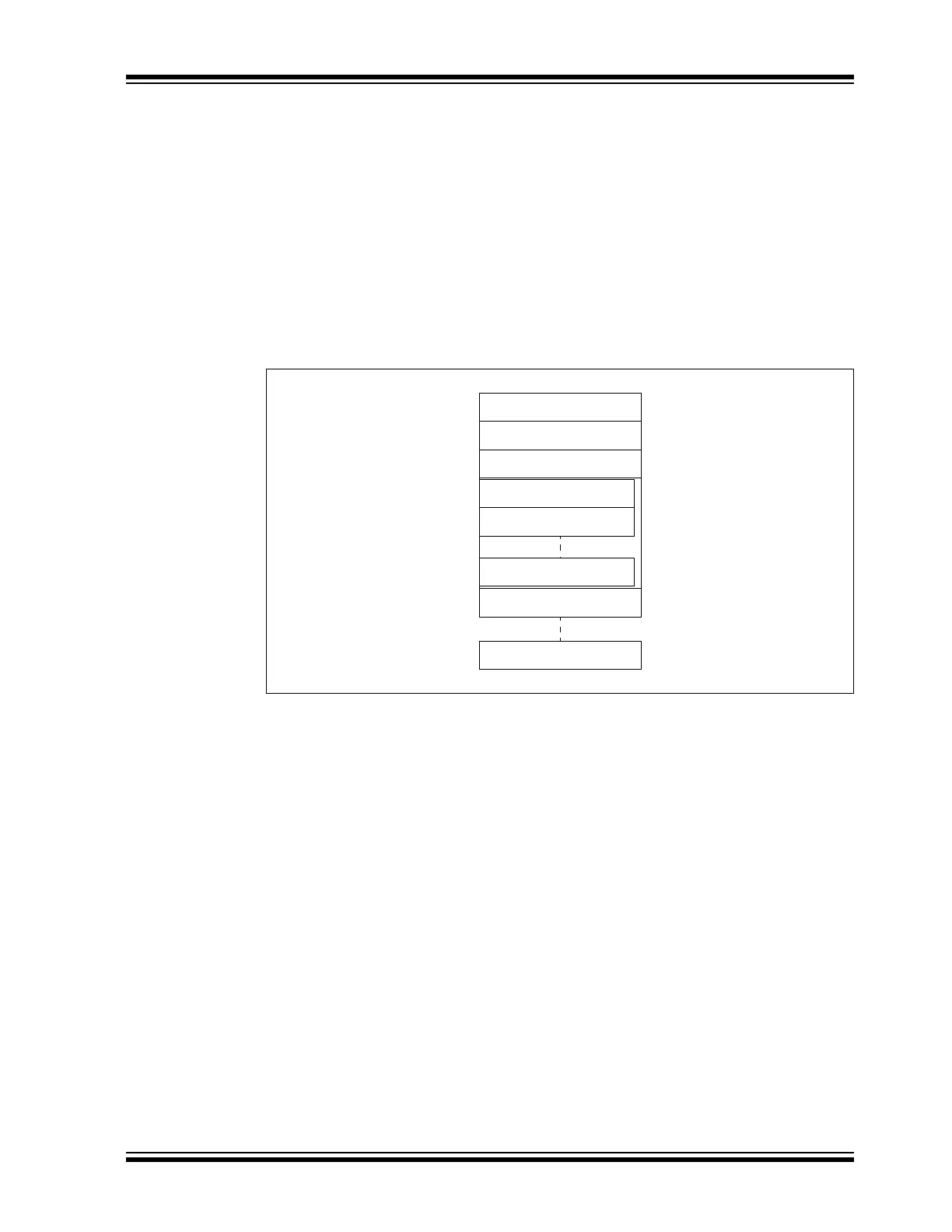

5.4 Message Memory Configuration

The message objects of the TEF, TXQ and transmit/receive FIFOs are located in RAM (see

Figure 5-4). The application must configure the number of message objects in a FIFO between

Message Object 0 and Message Object 31. Additionally, the application must configure the

payload size of the message objects in each FIFO. This configuration determines where

message objects are located in RAM. The RAM allocation can only be configured in

Configuration mode.

In order to optimize RAM usage, the application should start configuring the RAM with the TEF,

followed by the TXQ, and continue with FIFO 1, FIFO 2, FIFO 3 and so on. In case a user

application requires TEF, TXQ and 16 additional FIFOs, it should configure TEF and TXQ,

followed by FIFO 1 through FIFO 16. It is not necessary to configure the unused FIFOs 17

through 31.

Figure 5-4: Message Memory Organization

5.4.1 TRANSMIT EVENT FIFO CONFIGURATION

In order to reserve space in RAM for the TEF, the STEF bit (C1CONH<3>) has to be set. The number

of message objects in the TEF is configured using the FSIZE<4:0> bits (C1TEFCONH<12:8>).

Transmitted messages can be timestamped by setting the TEFTSEN bit (C1TEFCONL<5>).

5.4.2 TRANSMIT QUEUE CONFIGURATION

In order to reserve space in RAM for the TXQ, the TXQEN bit (C1CONH<4>) has to be set. The

number of message objects in the TXQ is configured using the FSIZE<4:0> bits

(C1TXQCONH<12:8>. All objects in the TXQ use the same payload size (number of data bytes),

which is configured using PLSIZE<2:0> bits (C1TXQCONH<15:13>).

5.4.3 TRANSMIT FIFO CONFIGURATION

FIFO 1 through FIFO 31 can be configured as transmit FIFOs by setting TXEN in the C1FIFOCONxL

register. The number of message objects in each transmit FIFO is configured using the FSIZE<4:0>

bits (C1FIFOCONxH<12:8>). All objects in one transmit FIFO use the same payload size (number of

data bytes), which is determined by the PLSIZE<2:0> bits (C1FIFOCONxH<15:13>).

TEF

TXQ

FIFO 1

FIFO 2: Message Object 0

FIFO 2: Message Object 1

FIFO 2: Message Object n

FIFO 31

FIFO 3

Loading...

Loading...