dsPIC33/PIC24 Family Reference Manual

DS70005340A-page 64 2018 Microchip Technology Inc.

5.3.7 BIT TIME CONFIGURATION EXAMPLE

The following tables illustrate the configuration of the CAN FD Bit Time registers, assuming there

is a CAN FD network in an automobile with the following parameters:

• 500 kbps NBR – Sample Point at 80%

• 2 Mbps DBR – Sample Point at 80%

•40 Meters – Minimum Bus Length

Table 5-3 and Ta bl e 5 -4 illustrate how the bit time parameters are calculated. Since the

parameters depend on multiple constraints and equations, and are calculated using an iterative

process, it is recommended to enter the equations in a spreadsheet.

Table 5-5 translates the calculated values into register values. It is recommended to let the CAN

FD Protocol Module measure the Transmitter Delay Compensation Value (TDCV). This is

accomplished by setting TDCMOD<1:0> (C1TDCH<1:0>) = 10 (Automatic mode). In order to set

the SSP to 80%, TDCO<6:0> are set to 1 + DTSEG1.

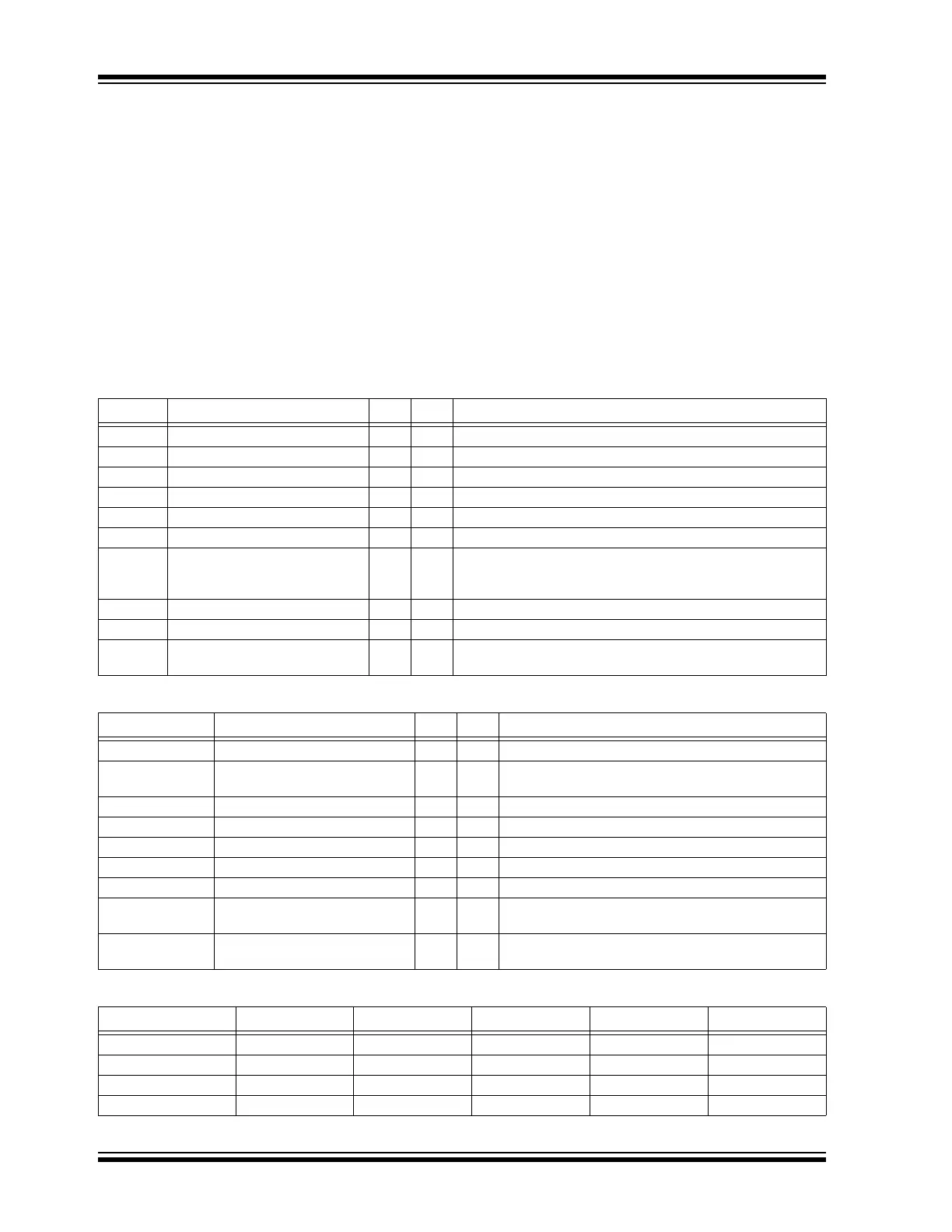

Table 5-3: Step-by-Step Nominal Bit Rate Configuration

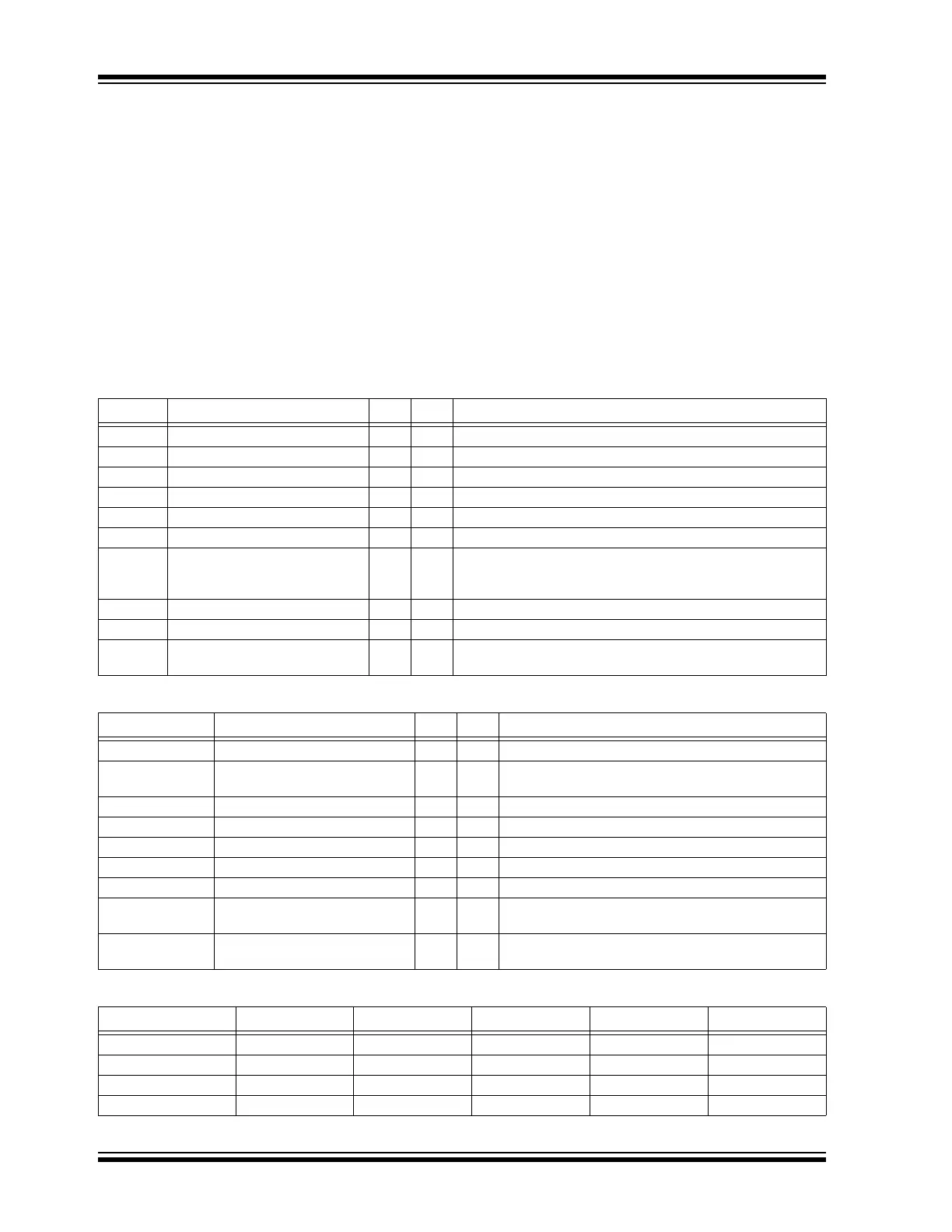

Table 5-4: Step-by-Step Data Bit Rate Configuration

Table 5-5: Bit Time Register Initialization (500k/2M)

Parameter Constraint Value Unit Equations and Comments

NBT NBT ≥ 1 s2s Equation 5-1.

F

OSC

F

OSC

≤ 80 MHz 80 MHz F

SYSCLK

= F

OSC

/2 = 40 MHz.

NBRP 1 to 256 1 — Select smallest possible BRP value to maximize resolution.

NTQ NBT, F

SYSCLK

12.5 ns Equation 5-3.

NBT/NTQ 4 to 385 160 — Equation 5-5.

NSYNC Fixed 1 NTQ Defined in ISO11898-1:2015.

NPRSEG NPRSEG > T

PROP

95 NTQ Equation 5-9: T

PROP

= 910 ns,

minimum NPRSEG = T

PROP

/NTQ = 72.8 NTQ.

Selecting 95 will allow up to 60m bus length.

NTSEG1 2 to 256 NTQ 127 NTQ Equation 5-7. Select NTSEG1 to achieve 80% NSP.

NTSEG2 1 to 128 NTQ 32 NTQ There are 32 NTQ left to reach NBT/NTQ = 160.

NSJW 1 to 128 NTQ;

SJW ≤ min (NPHSEG1, NPHSEG2)

32 NTQ Maximizing NSJW lessens the requirement for the oscillator tolerance.

Parameter Constraint Value Unit Equations and Comments

DBT DBT ≥ 125 ns 500 ns Equation 5-2.

DBRP 1 to 256 1 — Selecting the same prescaler as for NBT ensures that the T

Q

resolution does not change during the Bit Rate Switching.

DTQ DBT, F

SYSCLK

12.5 ns Equation 5-4.

DBT/DTQ 3 to 49 40 — Equation 5-6.

DSYNC Fixed 1 DTQ Defined in ISO11898-1:2015.

DTSEG1 1 to 32 DTQ 31 DTQ Equation 5-7. Select DTSEG1 to achieve 80% DSP.

DTSEG2 1 to 16 DTQ 8 DTQ There are 8 DTQ left to reach DBT/DTQ = 40.

DSJW 1 to 16 DTQ;

SJW ≤ min (DPHSEG1, DPHSEG2)

8 DTQ Maximizing DSJW lessens the requirement for the

oscillator tolerance.

Oscillator Tolerance

Conditions 1-5

Minimum of Conditions 1-5 0.78 % Equation 5-11 through Equation 5-16.

C1NBTCFGH/L Value C1DBTCFGH/L Value C1TDCH/L Value

BRP<7:0> 0 BRP<7:0> 0 TDCMOD<1:0> 2

TSEG1<7:0> 126 TSEG1<4:0> 30 TDCO<6:0> 31

TSEG2<6:0> 31 TSEG2<3:0> 7 TDCV<5:0> 0

SJW<6:0> 31 SJW<3:0> 7 — —

Loading...

Loading...