dsPIC33/PIC24 Family Reference Manual

DS70005340A-page 94 2018 Microchip Technology Inc.

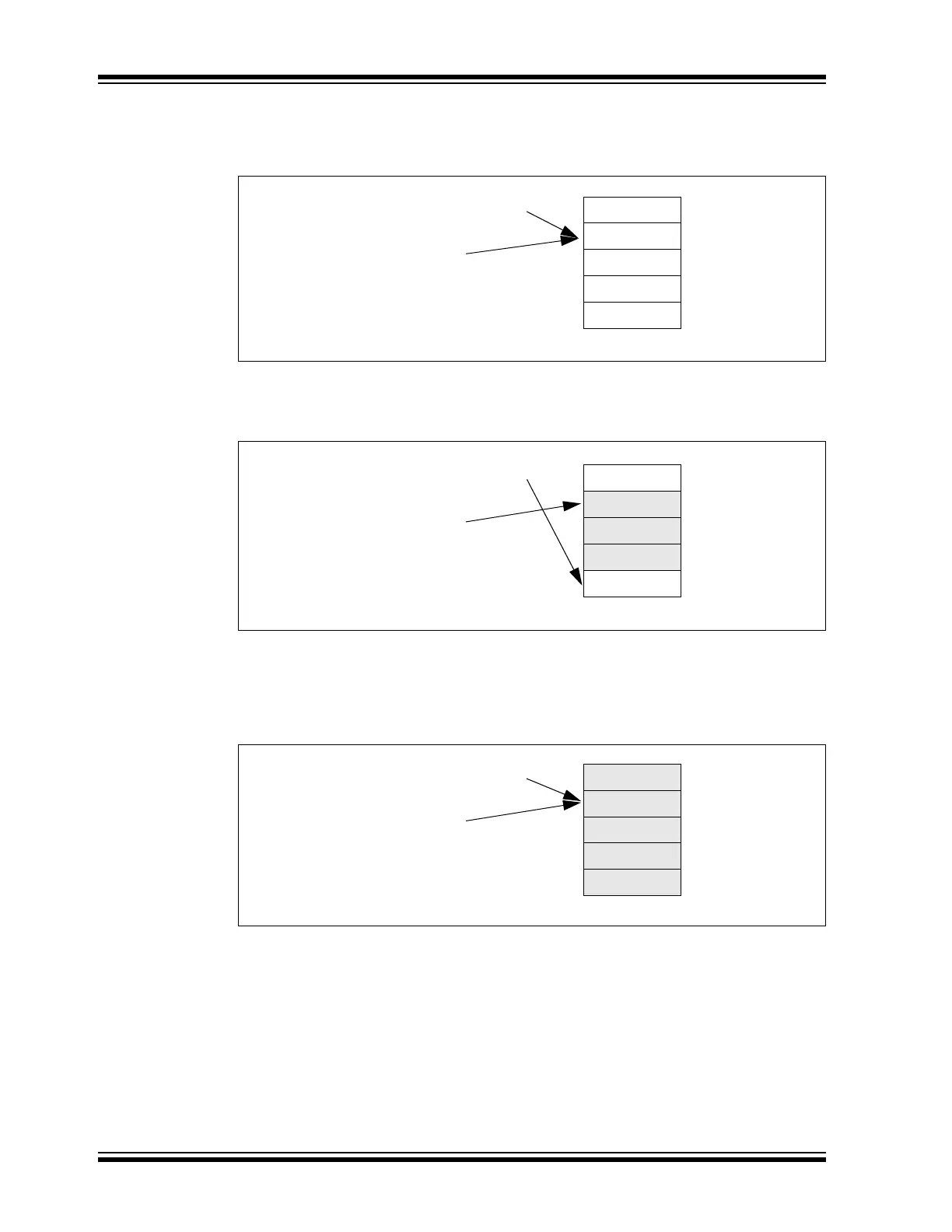

Figure 10-3 illustrates the status of FIFO 1 after MSG0 is transmitted. The FIFO is empty again.

TFEIF is set and TXREQ is cleared. FIFOCIx bits now point to MO1 with user address 0x218.

Figure 10-3: FIFO 1 – First Message Transmitted

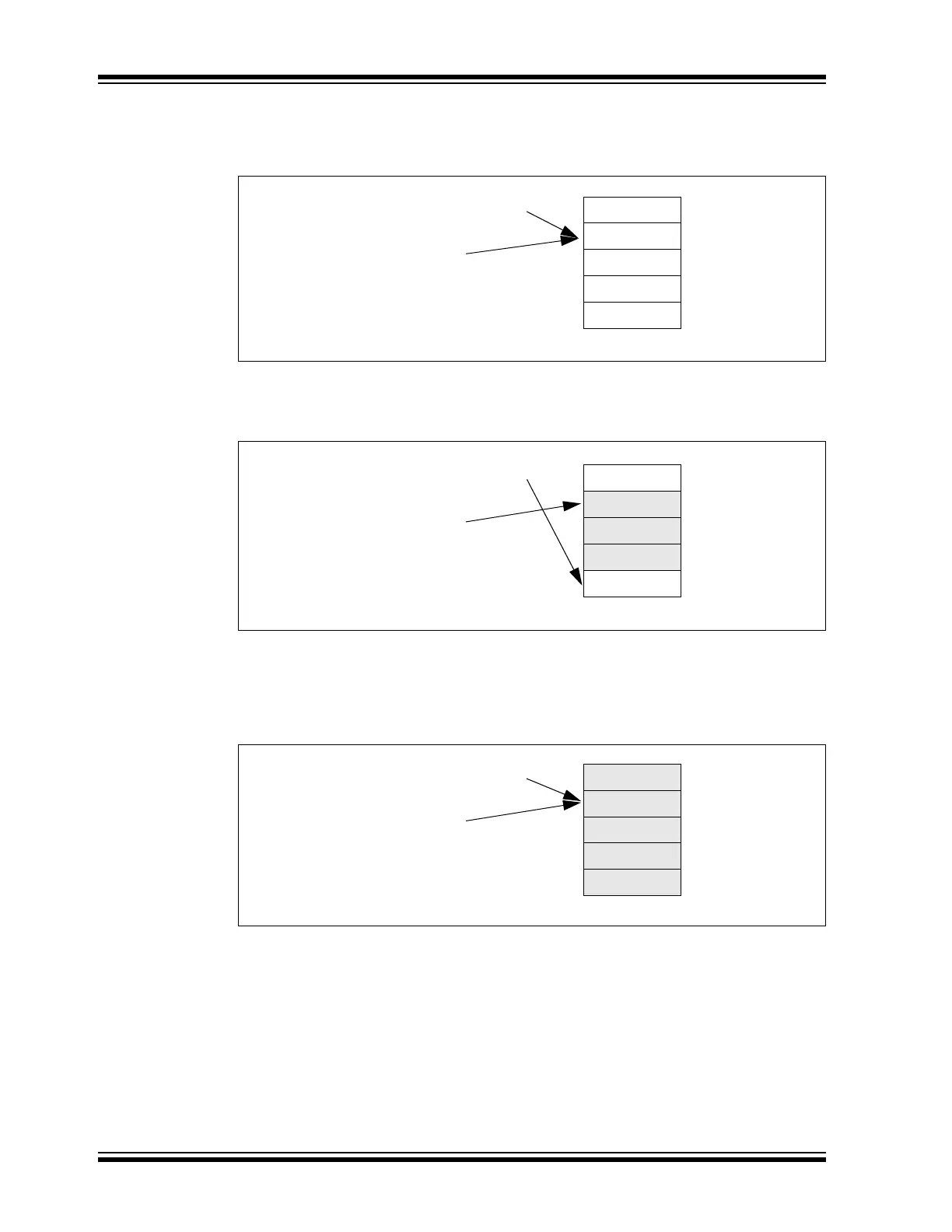

Figure 10-4 illustrates the status of FIFO 1 after three more messages are loaded: MSG1-MSG3. The

user address now points to MO4. TFHIF is cleared because the FIFO is now less than half empty.

Figure 10-4: FIFO 1 – Three More Messages Loaded

Figure 10-5 illustrates the status of FIFO 1 after two more messages are loaded: MSG4 and

MSG5. C1FIFOUA1L now points to MO1. All status flags are now cleared because the FIFO is

full. The user address and the FIFO index now point to MO1. The user application now sets

TXREQ to request the transmission of MSG1-MSG5.

Figure 10-5: FIFO 1 – FIFO Fully Loaded

MO0

MO1

MO2

MO3

MO4

C1FIFOUA1L = 0x218

C1FIFOSTA1:

FIFOCIx = 1

TFEIF = 1

TFHIF = 1

TFNIF = 1

C1FIFOCON1L:

TXREQ = 0

MO0

MO1/MSG1

MO2/MSG2

MO3/MSG3

MO4

C1FIFOUA1L = 0x2F0

C1FIFOSTA1:

FIFOCIx = 1

TFEIF = 0

TFHIF = 0

TFNIF = 1

C1FIFOCON1L:

TXREQ = 0

MO0/MSG5

MO1/MSG1

MO2/MSG2

MO3/MSG3

MO4/MSG4

C1FIFOUA1L = 0x218

C1FIFOSTA1:

FIFOCIx = 1

TFEIF = 0

TFHIF = 0

TFNIF = 0

C1FIFOCON1L:

TXREQ = 1

Loading...

Loading...