Motorola Confidential Proprietary

Theory of OperationService Manual(Level 3)

3-15

Draft 1.0

Baseband Electrical (Digital)

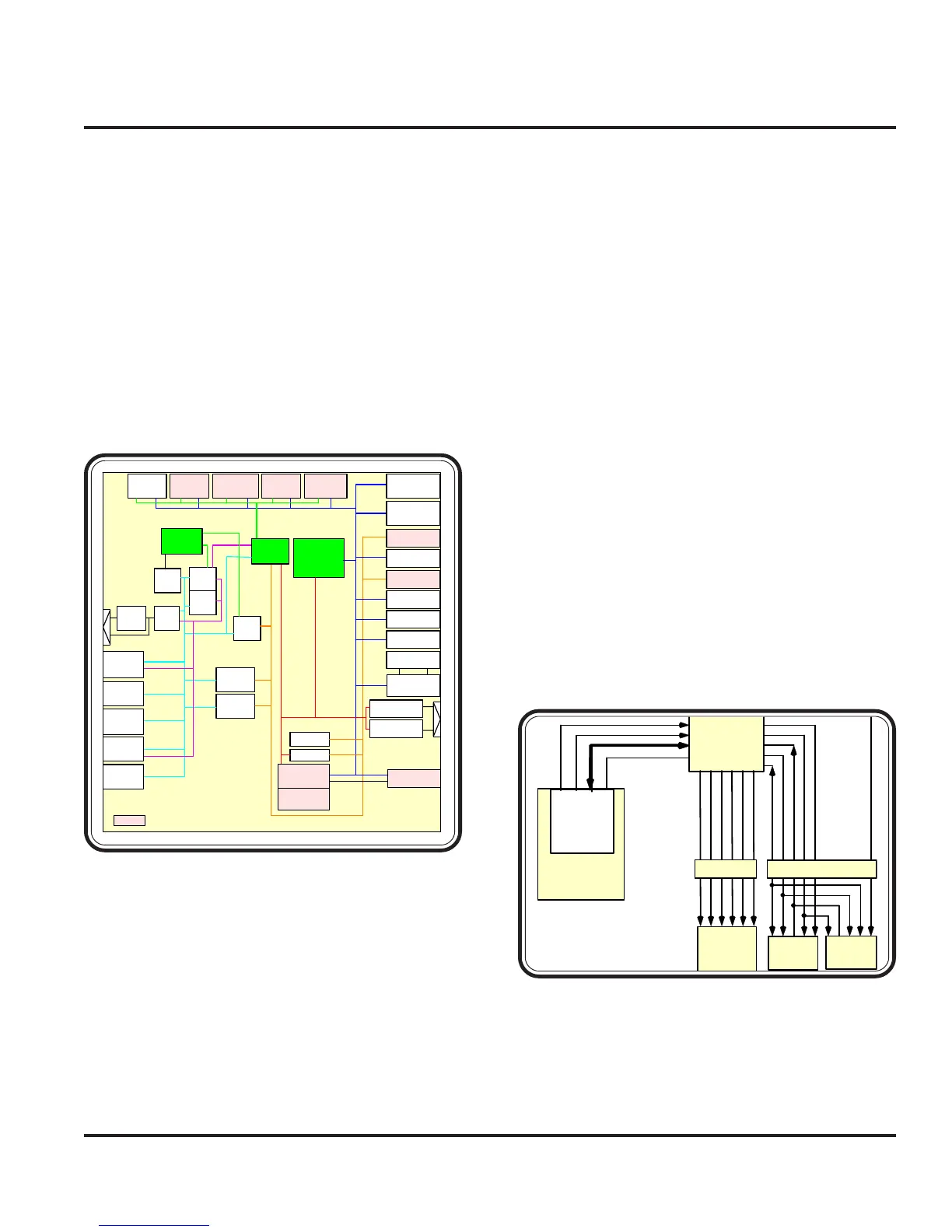

POG (U1000)

POG is the baseband processor IC of the 3G chipset

solution. POG is crafted to provide a high performance

embedded solution at low power for 3G mobile de-

vices. POG is a TriCore processor IC integrating a pow-

erful DSP core, a 32bit MCU RISC core with unified

cache and a custom 32bit RISC engine for data move-

ment across the processing domains.

The DSP core is a high performance StarCore with four

parallel ALUs, the SC140, with a novel Variable Length

Execution Set (VLES) architecture which maximizes the

execution of multiple instructions in a single clock cycle.

The SC140 is assisted by 3G specific hardware accel-

erators and timers to optimize performance and power.

As part of the 3G support, the Wideband CDMA Sig-

nal Processor (WCSP) module implements modem

functions required by the CDMA subscriber unit in ac-

cordance with the 3GPP specifications.

The 32bit MCU RISC core is the M*Core M341 de-

signed for high performance and low power embedded

systems. The M341 embodies an 16K unified cache,

integer multiplier and MMU in support of virtual memory

management OSes.

Data communication across the cores is handled by a

flexible 32bit RISC machine, the Inter Processor Com-

munication Module (IPCM). The IPCM supports flex-

ible data flow between the MCU, DSP and the multi-

media peripherals.

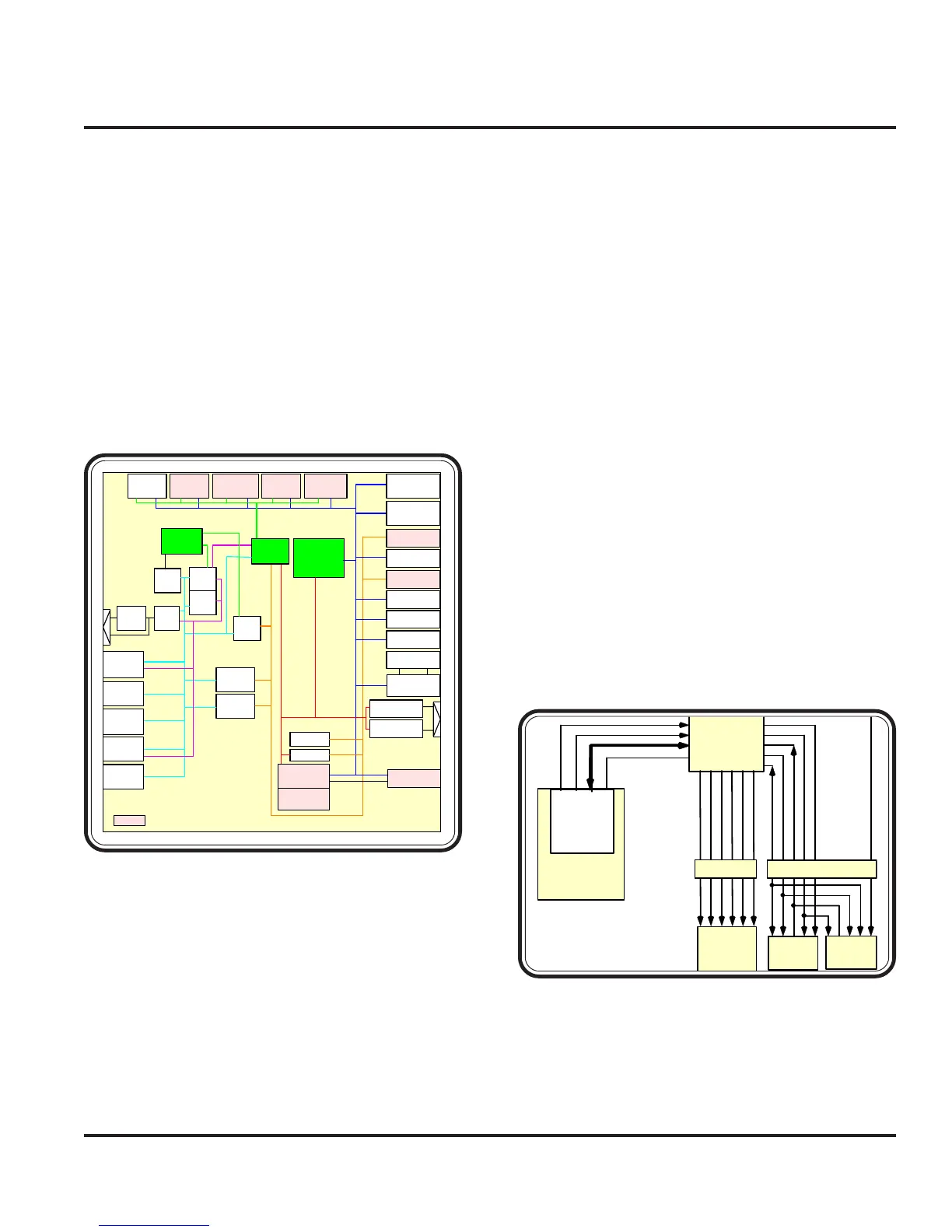

Graphics Accelerator

U5201 is a high performance, low power, Graphics/

Media Processor IC (GPU) that supports advanced

multimedia applications for W-CDMA, UMTS, and

GSM. This IC enables the user to capture, view, and

share high quality images and video. A hardware-based

MPEG-4 encoder captures video at up to CIF resolu-

tion at 30fps. A hardware-based video decoder allows

playback of the video recorded, or any other MPEG-4

clip or streaming video. A full hardware codec is uti-

POG

(U1 000)

M*Co re

Platform

USB UART 3

VIDEO SAP

(VSAP)

MMC

UART1

RS232/IrDa

Q2IP

MDI

Debug

Timer

Watchdog

DMA 2

SRAM

QMDA

(8)

GEM

HACC

EIM

SDRAM Ctl.

IPCM

Platform

EBIFWCSP

Serial

BBP

L1T_1/2

MQSPI

Audio

SAP

GPIO

1&2

Not used in this design

UART2

RS232/IrDa

GPIO

3&4

Keypad

Watchdog

One Wire

SIM _1/2

SGPT

GQSPI

Clk Control

2 PLLs

2ClkMon

LCD

StarCore

Platform

LCD SRAM

Controller

Video

Buffe r

Figure 3-18. POG Block Diagram

Figure 3-19. GPU Interface

E

x

t

e

r

n

a

l

I

n

t

e

r

f

a

c

e

M

o

d

u

l

e

(

E

I

M

)

POG

(U1000)

Gr aphics

Ac celer ator

(U5201)

Main

Display

DATA(15:0)

GPU_IND_ADDR

GPU_INTb

PCAP_RESETb

VG A

Cam

CIF

Ca m

D

I

S

P

_

H

S

Y

N

C

D

I

S

P

_

V

S

Y

N

C

L

C

D

_

G

R

N

(

5

:

0

)

L

C

D

_

R

E

D

(

5

:

0

)

L

C

D

_

B

L

U

(

5

:

0

)

D

I

S

P

_

M

C

L

K

J7500

I

M

G

_

R

E

S

E

T

b

V

I

P

_

S

D

A

V

I

P

_

S

L

D

V

I

P

_

D

A

T

A

(

9

:

2

)

J790 0

V

G

A

_

O

F

F

C

I

F

_

O

F

F

Baseband Electrical (Digital)

Loading...

Loading...