AWARD

®

BIOS Setup

3-13

!Note: Change these settings only if you are familiar with the chipset.

SDRAM Cycle Length

The option controls the CAS latency, which determines the timing delay

before SDRAM starts a read command after receiving it. Settings are 2 and

3 (clock cycles). 2 increases system performance while 3 provides more

stable system performance.

DRAM Clock

The chipset supports synchronous and asynchronous mode between host

clock and DRAM clock frequency. Settings are:

Host CLK The DRAM clock will be equal to the Host clock.

HCLK-33M The DRAM clock will be equal to the Host clock minus

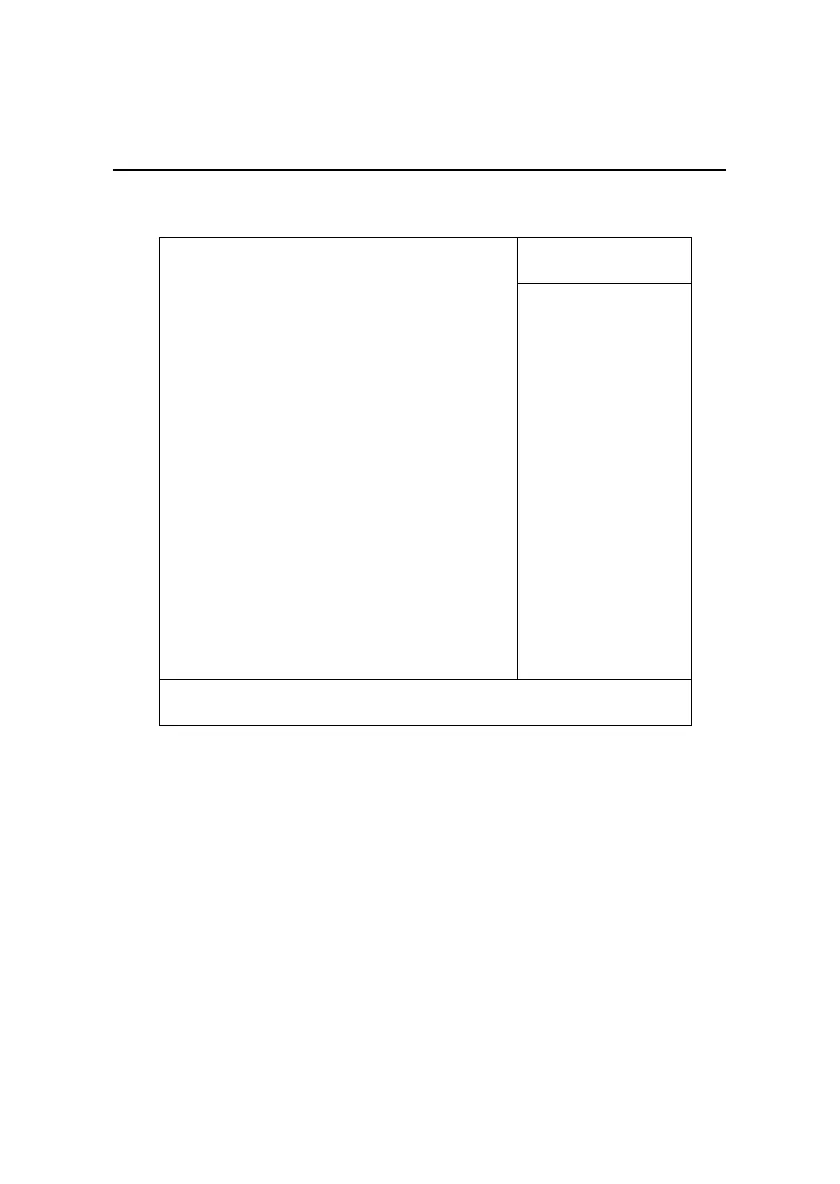

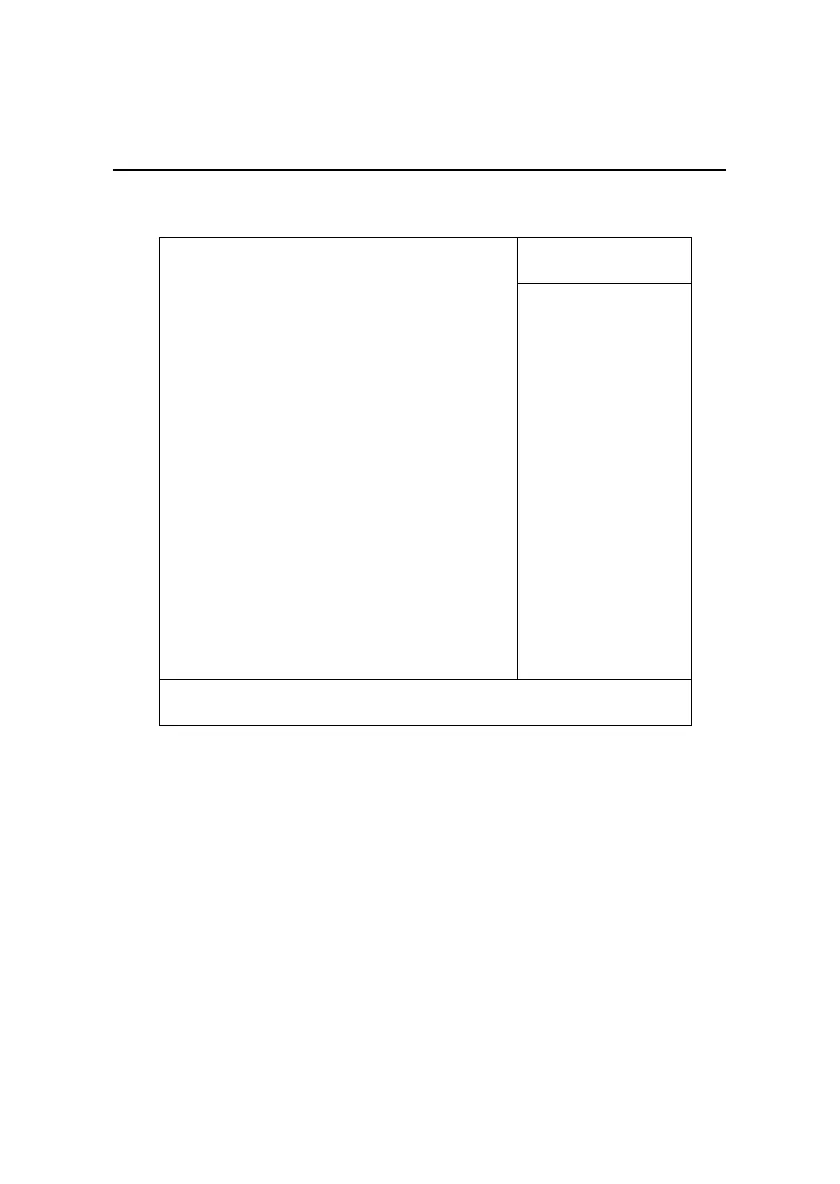

Advanced Chipset Features

↑ ↓ → ←:Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Fail-Safe Defaults F7:Optimized Defaults

SDRAM Cycle Length 3

DRAM Clock Host CLK

Memory Hole Disabled

P2C/C2P Concurrency Enabled

Fast R-W Turn Around Disabled

System BIOS Cacheable Disabled

Video RAM Cacheable Disabled

AGP Aperture Size 64M

AGP-4X Mode Enabled

AGP Driving Control Auto

AGP Driving Value DA

AGP Fast Write Disabled

OnChip USB Enabled

USB Keyboard Support Disabled

USB Mouse Support Disabled

On Chip Sound Auto

OnChip Modem Auto

CPU to PCI Write Buffer Enabled

PCI Dynamic Bursting Enabled

PCI Master 0 WS Write Enabled

PCI Delay Transaction Enabled

PCI#2 Access #1 Retry Enabled

AGP Master 1 WS Write Disabled

AGP Master 1 WS Read Disabled

Memory Parity/ECC Check Disabled

CMOS Setup Utility - Copyright(C) 1984-2000 Award Software

Advanced Chipset Features

Item Help

Menu Level !

x

Loading...

Loading...