USB and PCIe

PRELIMINARY INFORMATION

Jetson Orin NX Series and Jetson Orin Nano Series DG-10931-001_v1.1 | 42

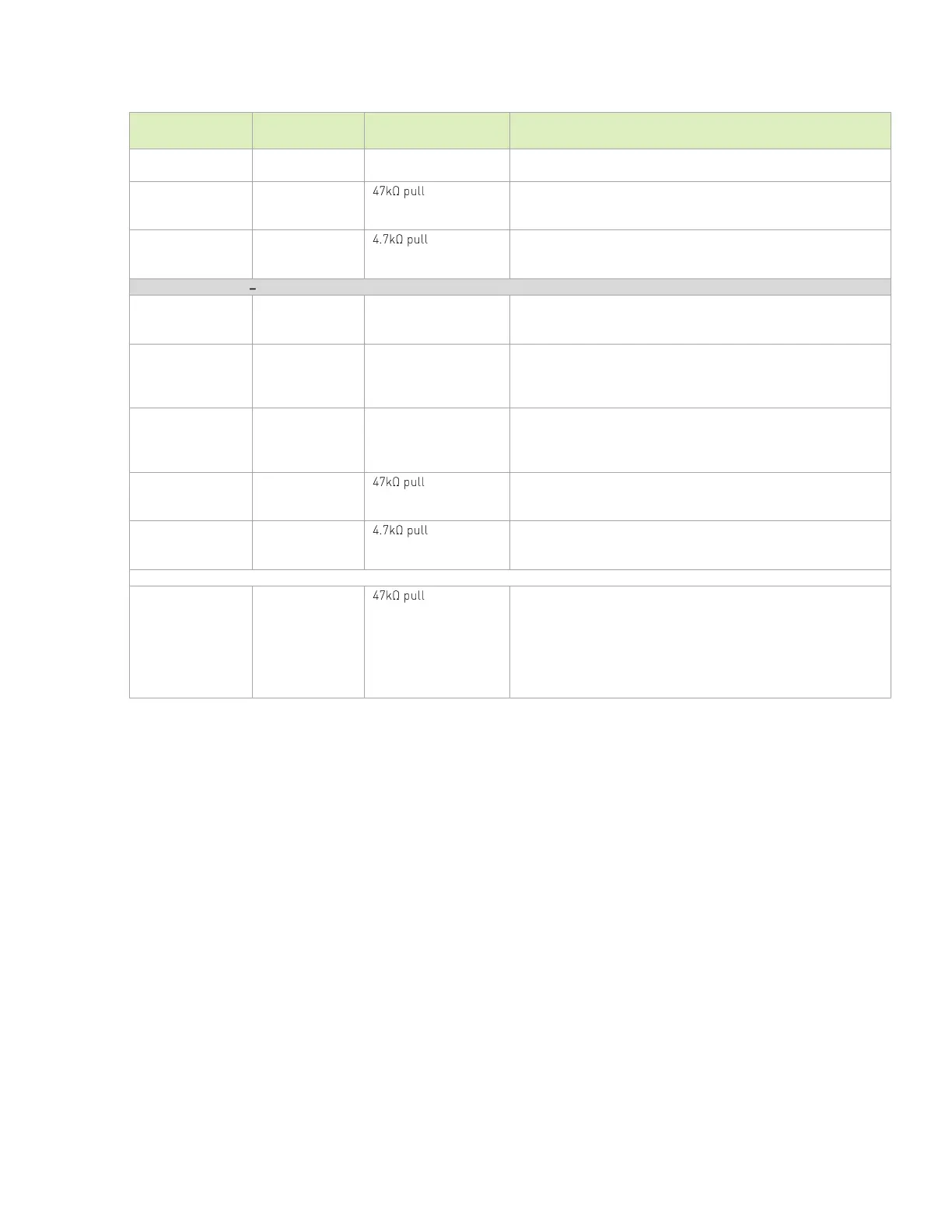

Module Pin

Name (Function)

CSI4_CLK_N/P

(PCIE2_CLK_N/P)

Differential Reference Clock Output: Connect to REFCLK_N/P

pins of PCIe device/connector

SDMMC_DAT1

(PCIE2_CLKREQ*)

-up to

VDD_3V3_SYS on

module

PCIe Clock Request for PCIE1_CLK: Connect to CLKREQ pins on

device/connector(s)

-up to

VDD_3V3_SYS on

module

PCIe Reset: Connect to PERST pins on device/connector(s)

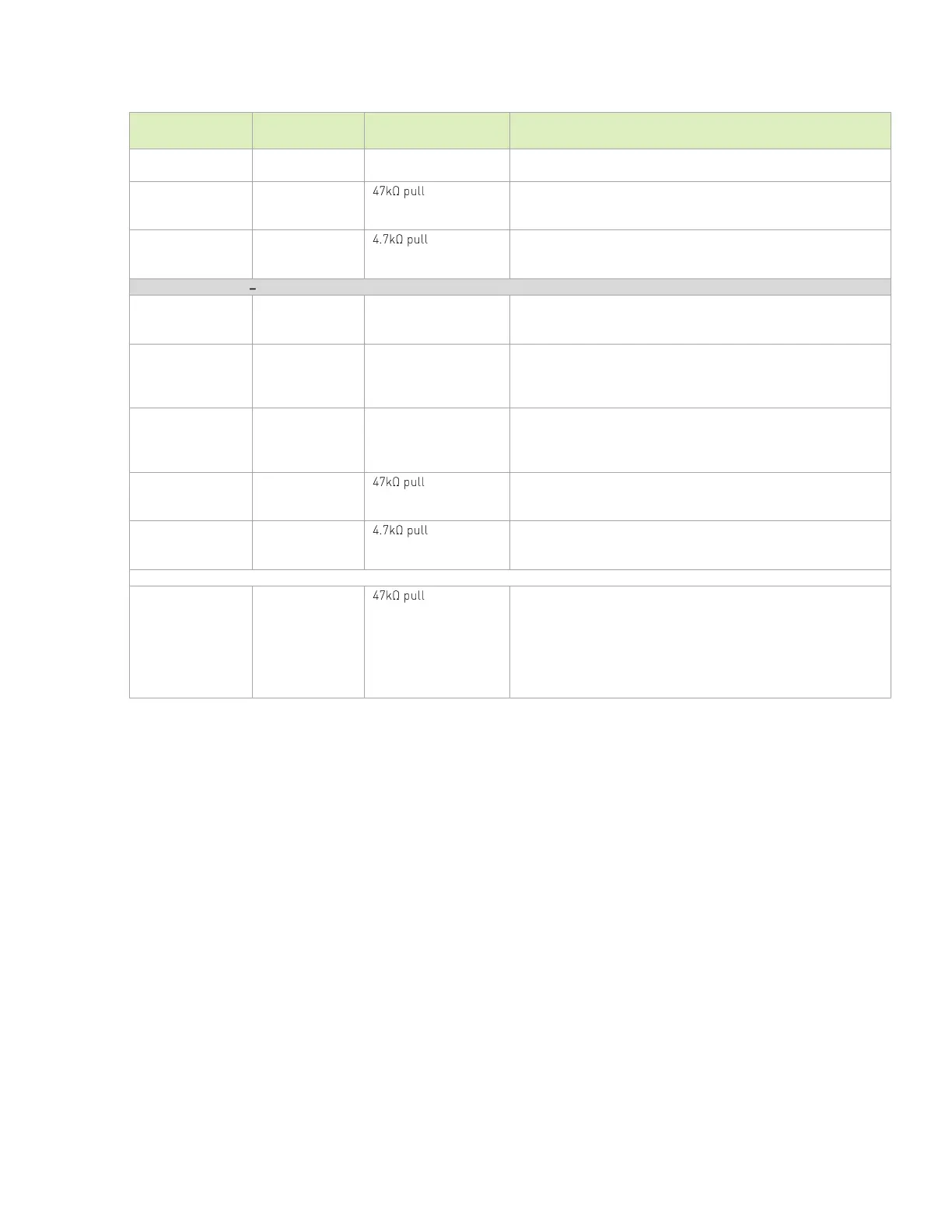

PCIe Interface 3 (x1 Controller #9. Available if PCIe IF #2 is used as x1 only. Supports Root Port only)

CSI4_D3_N/P

(PCIE3_TX0_N/P)

Differential Transmit Data Pair: Connect to TX_N/P pins of PCIe

connector or RX_N/P pin of PCIe device through AC cap according

to supported configuration.

CSI4_D1_N/P

(PCIE3_RX0_N/P)

Series 0.22uF

capacitors near

module pins or device

if device on main PCB.

Differential Receive Data Pair: Connect to RX_N/P pins of PCIe

connector or TX_N/P pin of PCIe device through AC cap according

to supported configuration.

SDMMC_CMD

(PCIE3_CLK_N)

SDMMC_CLK

(PCIE3_CLK_P)

Differential Reference Clock Output: Connect to REFCLK_N/P

pins of PCIe device/connector

SDMMC_DAT3

(PCIE3_CLKREQ*)

-up to

VDD_3V3_SYS on

module

PCIe Clock Request for PCIE1_CLK: Connect to CLKREQ pins on

device/connector(s)

-up to

VDD_3V3_SYS on

module

PCIe Reset: Connect to PERST pins on device/connector(s)

-up to

VDD_3V3_SYS on

module

PCIe Wake: Connect to WAKE pins on device or connector. If the

module is configured as an Endpoint, include a isolator between

the wake pin on the module and the device/connector powered by

the 3.3V rail at the connector or device. The isolator should have

the output toward the connector or device. This isolates the on-

module pull-up resistors as well as ensures this signal will not be

pulled or driven high before the Root Port is powered on.

Loading...

Loading...