IC BLOCK DIAGRAMS AND TERMINAL DESCRIPTIONS

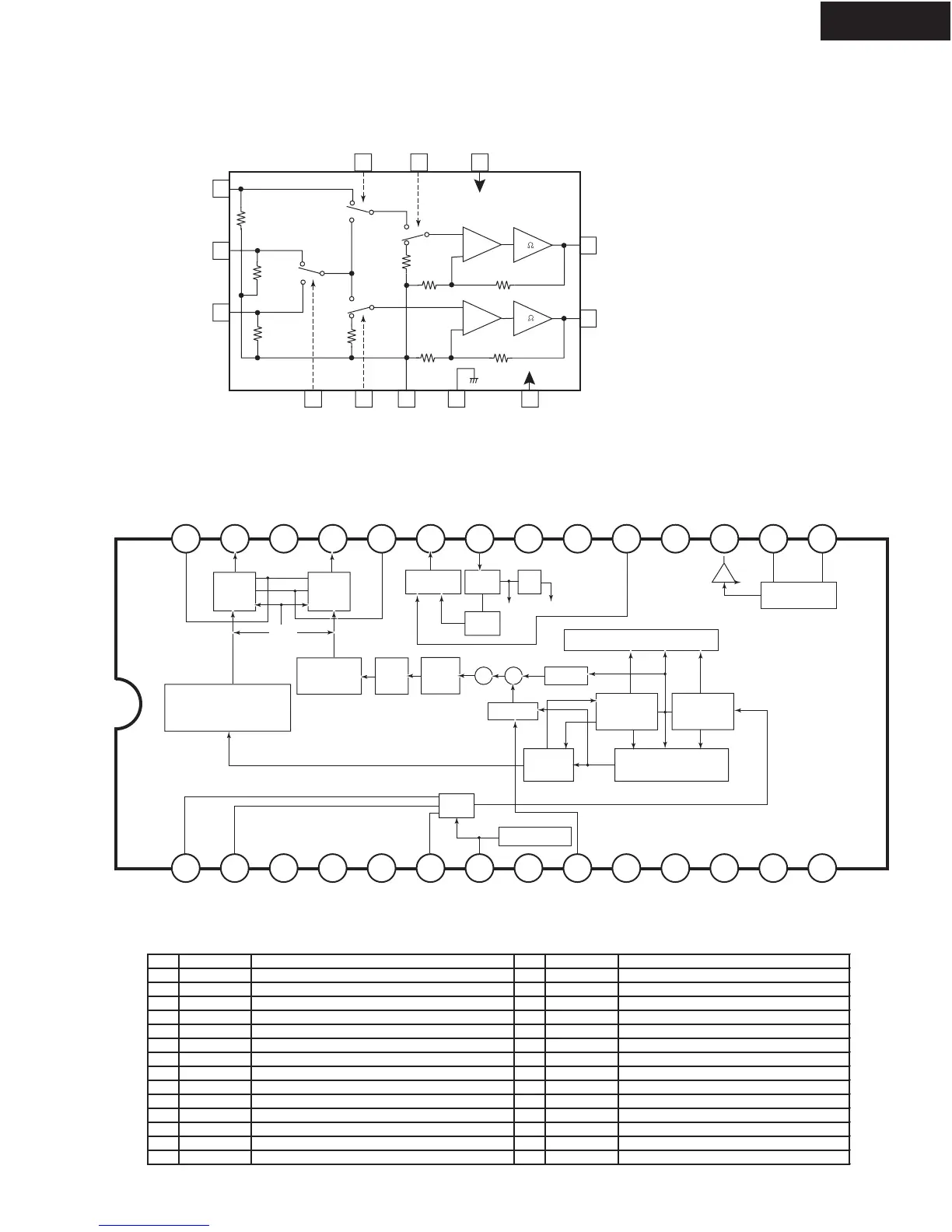

NJM2279 (3 Input/2 Output Video Switch)

BLOCK DIAGRAM

TX-L55/LR552

NJM2279 (3 Input/2 Output Video Switch)

SW1 MUTE2 GND1 GND2 V-

Vout1

Vout2

SW2 MUTE1 V+

Vin1

Vin2

Vin3

20k

20k

20k

20k

20k

4.14k

4.14k

AMP

DRIVER

AMP

DRIVER

4.45k

4.45k

6dB

6dB

75

75

1. Vin3

2. SW1

3 Vin2

4. MUTE2

5. Vout2

6. GND2

7. GND1

8. V+

9. N.C

10. Vout1

11. MUTE1

12. Vin1

13. SW2

14. V-

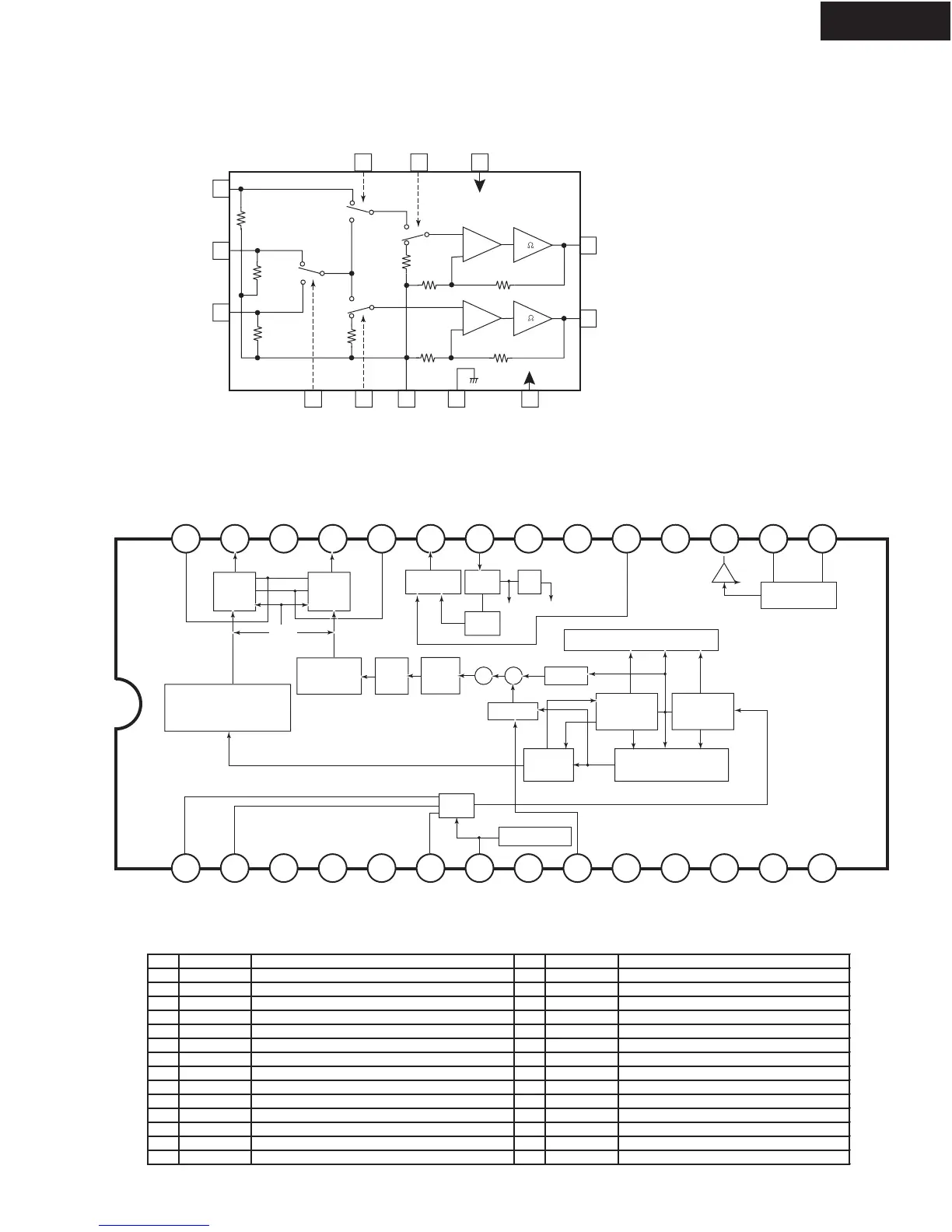

1234567891011121314

28 27 26 25 24 23 22 21 20 19 18 17 16 15

DAC DAC

PLL DET VCO 1/2

1/8

8fsc

4fsc

I CBUS

2

8fsc

INTERPOLATION

CORING

PEAKING

LPF

Ped.

CLIP

++

CORING V-ENHANCER

KILLER

LINE

MEMORY

LINE

MEMORY

CNR

C-N.C

DYNAMIC COMB

FILTER

ADC

Sync Clamp

DELAY

VB1

COUT

Vss1

YOUT

VB2

PD

FIL

Vss4

VDD4

FSC

TESTOUT

MODE1

SDA

SCL

BIAS

VRT

VDD1

TEST11

Vss2

VRB

YCIN

TEST

KILLER

TEST12

VDD3

Vss3

VDD2

TEST13

Pin Symbol Function Pin Symbol Function

1 BIAS Bias for ADC 15 SCL Clock input of I2C Bus

2 VRT Maximum bias of D range for ADC 16 SDA Data input/output of I2C Bus

3 VDD1 Analog supply for ADC/DAC 17 MODE1 Mode 1 output

4 TEST1 Test input 18 TESTOUT Test output

5 VSS2 Analog ground supply for ADC 19 FSC Clock input of I2C Bus

6 VRB Minimum bias of D range for ADC 20 VDD4 Analog supply for PLL

7 YCIN Video signal input 21 VSS4 Analog ground supply for PLL

8 TEST1 Reset control and test control of initializing 22 FIL VCO control

9 KILLER Y/C separation and vertical enhancer off control 23 PD PLL detection output

10 TEST2 Test input 24 VB2 Bias 2 for DAC

11 VDD3 Digital soppy for logic 25 YOUT Brightness signal output

12 VSS3 Digital ground supply for Logic/DRAM 26 VSS1 Analog ground for DAC

13 VDD2 Digital supply for DRAM 27 COUT Color signal output

14 TEST3 Test input 28 VB1 Bias 1 for DAC

TC90A69F (COM Filter)

Loading...

Loading...