TDA8950_2 © NXP B.V. 2009. All rights reserved.

Product data sheet Rev. 02 — 11 June 2009 14 of 39

NXP Semiconductors

TDA8950

2 × 150 W class-D power amplifier

12. Dynamic characteristics

12.1 Switching characteristics

[1] V

P

is the supply voltage on pins VDDP1, VDDP2 and VDDA.

[2] When using an external oscillator, the frequency f

track

(500 kHz minimum, 900 kHz maximum) will result in a PWM frequency f

osc

(250 kHz minimum, 450 kHz maximum) due to the internal clock divider; see Section 8.2.

[3] When t

r(i)

> 100 ns, the output noise floor will increase.

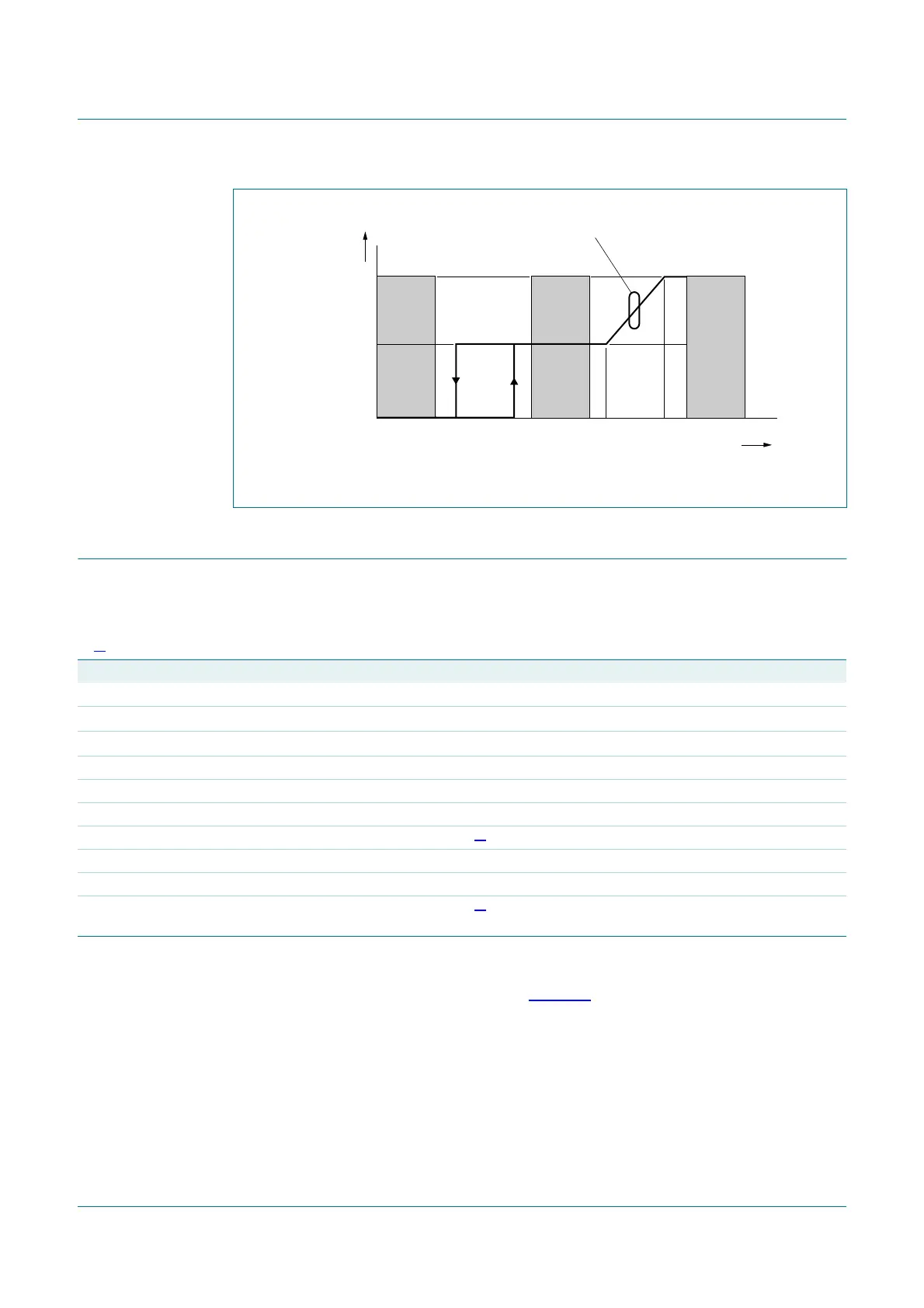

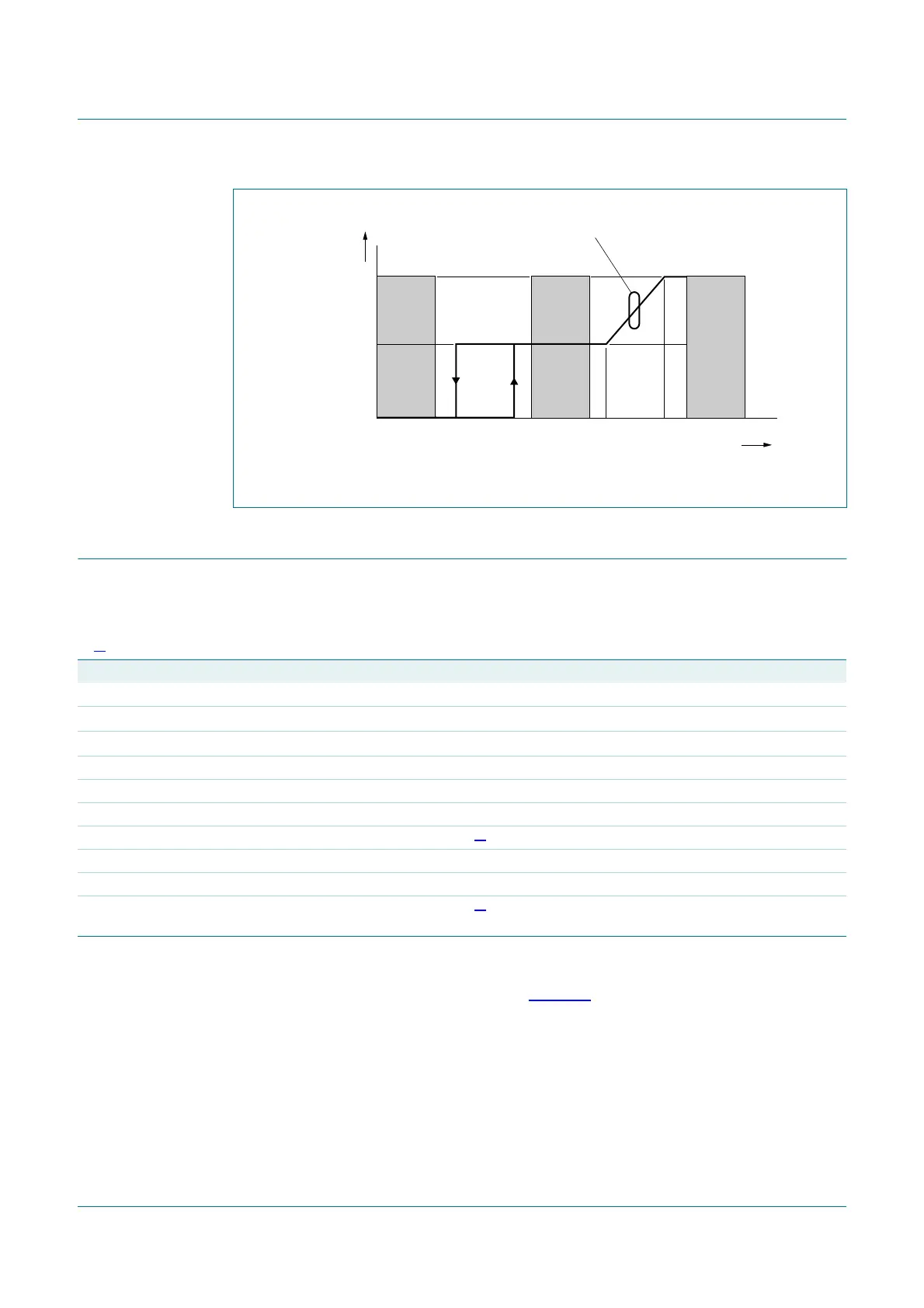

Fig 8. Behavior of mode selection pin MODE

Standby Mute On

5.5

coa021

V

MODE

(V)

4.23.02.20.80

V

O

(V)

V

O(offset)(mute)

V

O(offset)(on)

slope is directly related to the time-constant

of the RC network on the MODE pin

Table 9. Dynamic characteristics

V

P

[1]

=

±

35 V; T

amb

= 25

°

C; unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Unit

Internal oscillator

f

osc(typ)

typical oscillator frequency R

OSC

= 30.0 kΩ 290 345 365 kHz

f

osc

oscillator frequency 250 - 450 kHz

External oscillator input or frequency tracking; pin OSC

V

OSC

voltage on pin OSC HIGH-level SGND + 4.5 SGND + 5 SGND + 6 V

V

trip

trip voltage - SGND + 2.5 - V

f

track

tracking frequency

[2]

500 - 900 kHz

Z

i

input impedance 1 - - MΩ

C

i

input capacitance - - 15 pF

t

r(i)

input rise time from SGND + 0 V

SGND + 5 V

[3]

- - 100 ns

Loading...

Loading...