TDA8950_2 © NXP B.V. 2009. All rights reserved.

Product data sheet Rev. 02 — 11 June 2009 15 of 39

NXP Semiconductors

TDA8950

2 × 150 W class-D power amplifier

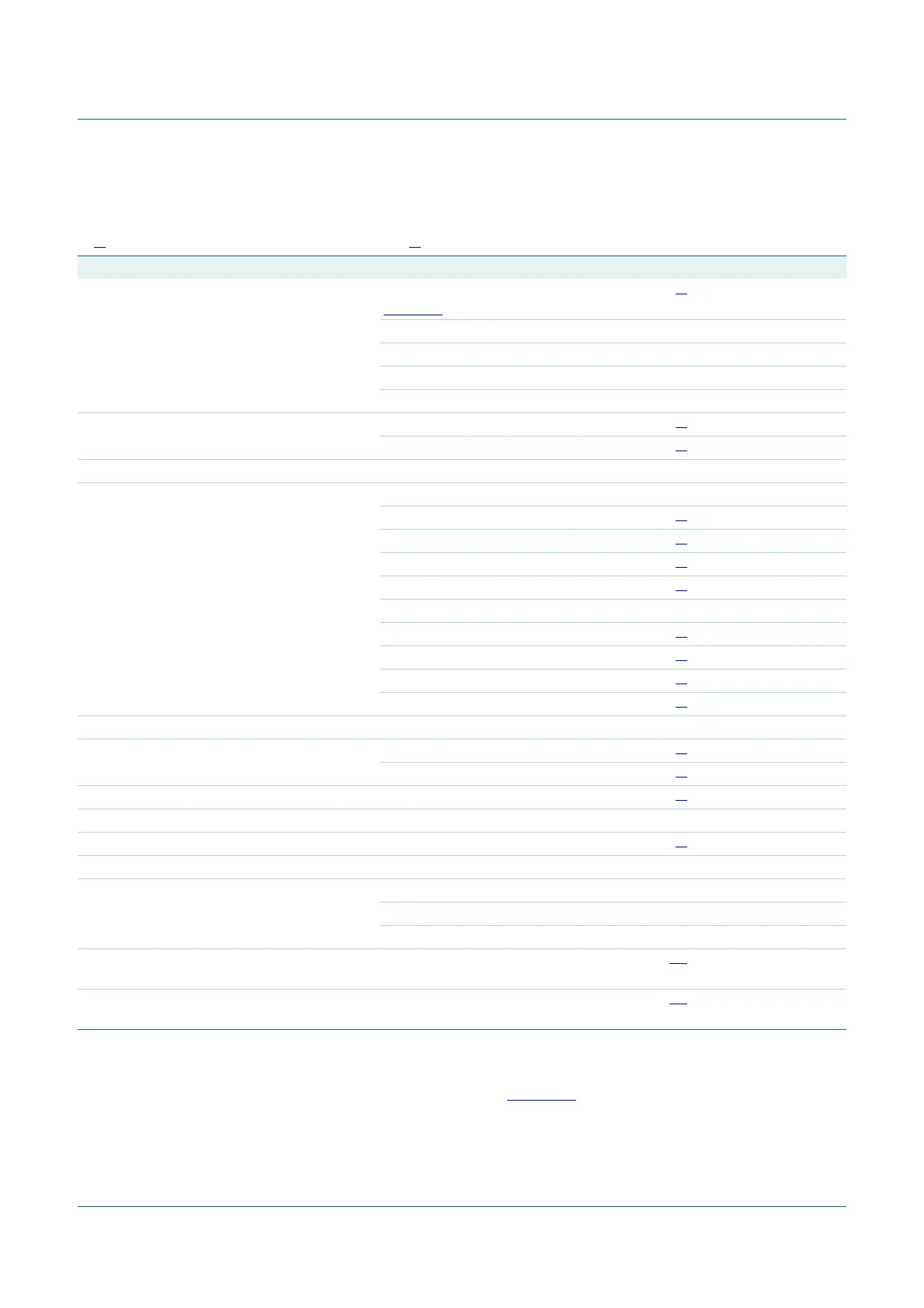

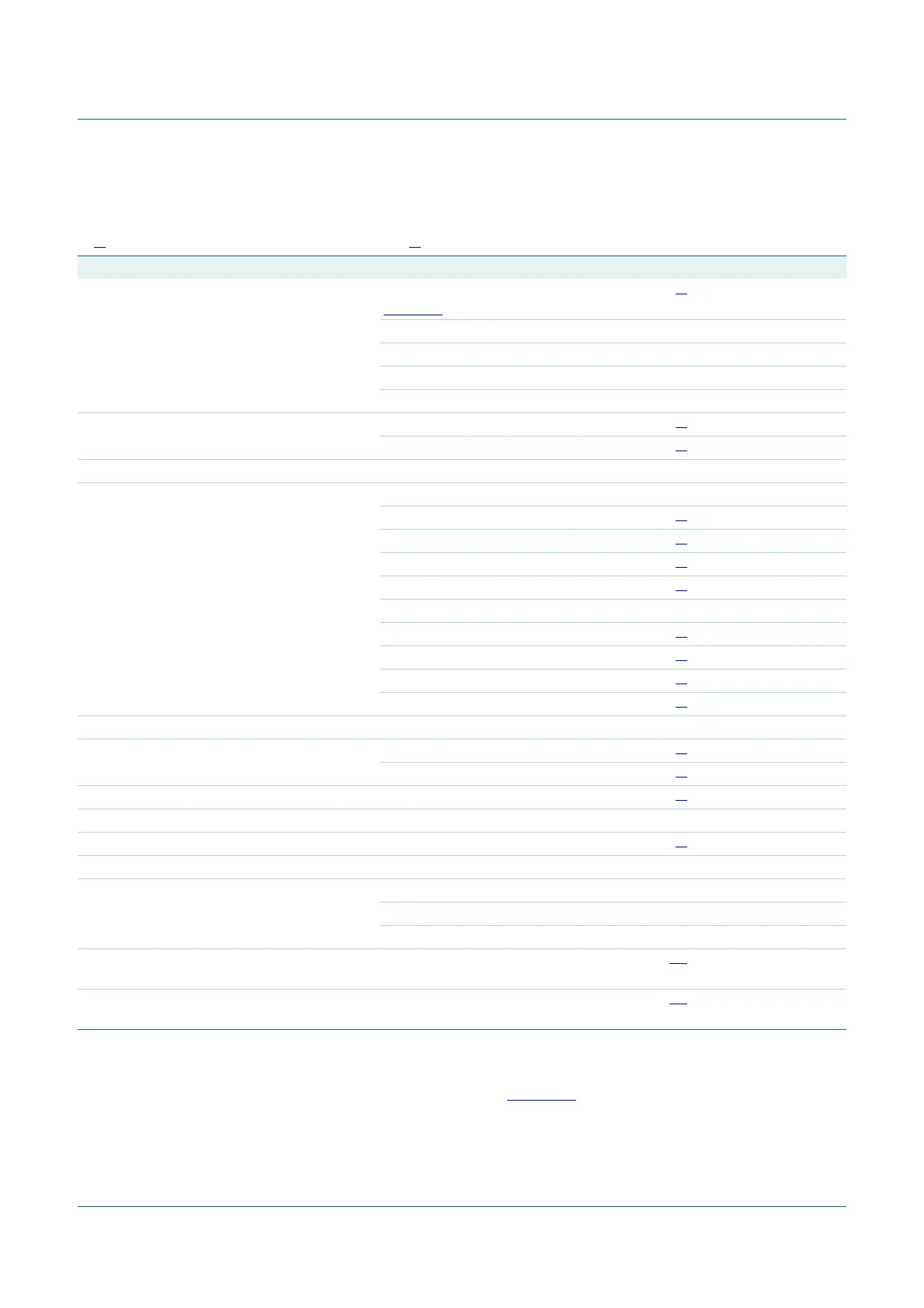

12.2 Stereo SE configuration characteristics

[1] V

P

is the supply voltage on pins VDDP1, VDDP2 and VDDA.

[2] R

sL

is the series resistance of the low-pass LC filter inductor used in the application.

[3] Output power is measured indirectly; based on R

DSon

measurement; see Section 13.3.

[4] THD measured between 22 Hz and 20 kHz, using AES17 20 kHz brick wall filter; max. limit is guaranteed but may not be 100 % tested.

[5] V

ripple

= V

ripple(max)

= 2 V (p-p); measured independently between VDDPn and SGND and between VSSPn and SGND.

[6] 22 Hz to 20 kHz, using AES17 20 kHz brick wall filter.

[7] 22 Hz to 20 kHz, using AES17 20 kHz brick wall filter.

Table 10. Dynamic characteristics

V

P

[1]

=

±

35 V; R

L

= 4

Ω

; f

i

= 1 kHz; f

osc

= 345 kHz; R

sL

[2]

< 0.1

Ω

; T

amb

= 25

°

C; unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Unit

P

o

output power T

j

=85°C; L

LC

=22µH; C

LC

= 680 nF (see

Figure 10)

[3]

THD + N = 10 %; R

L

=4Ω; V

P

= ±39 V 170 W

THD + N = 0.5 %; R

L

= 4 Ω; V

P

= ±37 V - 100 - W

THD + N = 10 %; R

L

= 4 Ω; V

P

= ±37 V - 150 - W

THD + N = 10 %; R

L

= 6 Ω; V

P

= ±37 V - 100 - W

THD total harmonic distortion P

o

= 1 W; f

i

= 1 kHz

[4]

- 0.05 - %

P

o

= 1 W; f

i

= 6 kHz

[4]

- 0.05 - %

G

v(cl)

closed-loop voltage gain 29 30 31 dB

SVRR supply voltage ripple rejection between pins VDDPn and SGND

Operating mode; f

i

= 100 Hz

[5]

-90-dB

Operating mode; f

i

= 1 kHz

[5]

-70-dB

Mute mode; f

i

= 100 Hz

[5]

-75-dB

Standby mode; f

i

= 100 Hz

[5]

- 120 - dB

between pins VSSPn and SGND

Operating mode; f

i

= 100 Hz

[5]

-80-dB

Operating mode; f

i

= 1 kHz

[5]

-60-dB

Mute mode; f

i

= 100 Hz

[5]

-80-dB

Standby mode; f

i

= 100 Hz

[5]

- 115 - dB

Z

i

input impedance between one of the input pins and SGND 45 63 - kΩ

V

n(o)

output noise voltage Operating mode; R

s

=0Ω

[6]

- 160 - µV

Mute mode

[7]

-85-µV

α

cs

channel separation

[8]

-70-dB

|∆G

v

| voltage gain difference - - 1 dB

α

mute

mute attenuation f

i

= 1 kHz; V

i

= 2 V (RMS)

[9]

-75-dB

CMRR common mode rejection ratio V

i(CM)

= 1 V (RMS) - 75 - dB

η

po

output power efficiency SE, R

L

= 4 Ω -88-%

SE, R

L

= 6 Ω -90-%

BTL, R

L

= 8 Ω -88-%

R

DSon(hs)

high-side drain-source on-state

resistance

[10]

- 200 - mΩ

R

DSon(ls)

low-side drain-source on-state

resistance

[10]

- 190 - mΩ

Loading...

Loading...