Circuit Descriptions

EN 25TPM5.1E LA 7.

2011-Sep-02

7. Circuit Descriptions

Index of this chapter:

7.1

Introduction

7.2 Power Architecture

7.3 T-CON Architecture

Notes:

•Only new circuits (circuits that are not published recently)

are described.

• Figures can deviate slightly from the actual situation, due

to different set executions.

• For a good understanding of the following circuit

descriptions, please use the wiring, block (see chapter

9.

Block Diagrams) and circuit diagrams (see chapter

10.

Circuit Diagrams and PWB Layouts).Where necessary,

you will find a separate drawing for clarification.

7.1 Introduction

The TPM5.1E LA chassis is used the MT5363LICG main

processing.

7.1.1 Implementation

Key components of this chassis are:

• TPA3110D2 Audio Amplifier

• NAND128W3A2BN6E NAND Flash

• TDTW-S810D Tuner

• NT5TU32M16CG-BD DDR Memory

• TPA6132A2RTER Head phone Amplifier

• TL2428MC T-CON IC

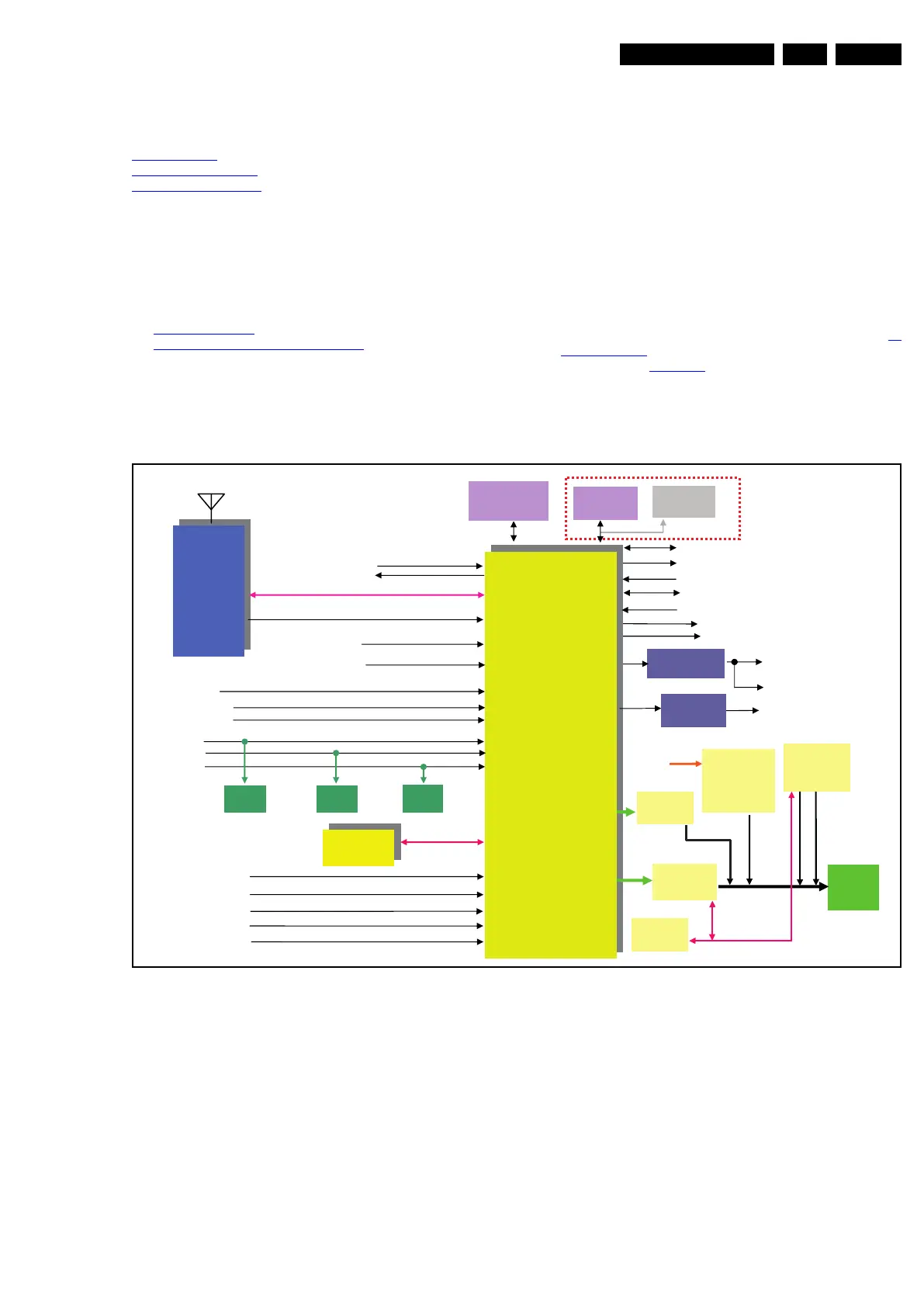

7.1.2 TPM5.1E Architecture Overview

For details about the chassis block diagrams refer to chapter 9.

Block Diagrams. An overview of the TPM5.1E LA architecture

can be found in Figure 7-1

.

Figure 7-1 Architecture of Dali

18850_211_100222.eps

100222

MT5363H

MCU

DTV receiver/demodulator

MPEG/video/audio decoder

Scaling

Video enhancement

3D comb

LVDS Transmitter

HDMI 1.3

ADC

H.264

Audio R/L of CVI

Audio AMP

TPA3110

IFAT +/- (VIF/SIF)

System NVM

24C64

System NVM

24C64

speakers

UART (ISP & Factory alignment)

SPDIF Out

RC

I2C

Audio R/L of SCART1

Audio R/L of Side CVBS

I

2

C

Key pad

CVI × 1

CVBS × 1 (side)

RF

Tuner

Side HDMI

EDID

24C02

EDID

24C02

HDMI

Audio R/L of PC/ DVI

SCART1 CVBS/YC

Audio R/L of SCART2

SCART2 CVBS out

SCART2 CVBS/YC

Audio Pre-amplifier

DRV603

SCART2 L/R out

SCART1 L/R out

SCART1 CVBS out

USB 2.0

SCART1 RGB

NAND Flash

16 MByte

NOR Flash

512 kByte

DDR2 1GHz

64 MByte × 2

VGA

EDID

24C02

MPEG2 TS

CI card

slot

T-con IC

TL2428MC

LCD

Panel

Mini LVDS × 2

LVDS

DC/DC suites

1. Max PF57

2. G5657

3. AP1117E18

Gamma

/ V-com

Max9668

Level shifter

TPS65192

12V

NVM

24C32

T-con I2C

Loading...

Loading...