116 Rabbit 2000 Microprocessor

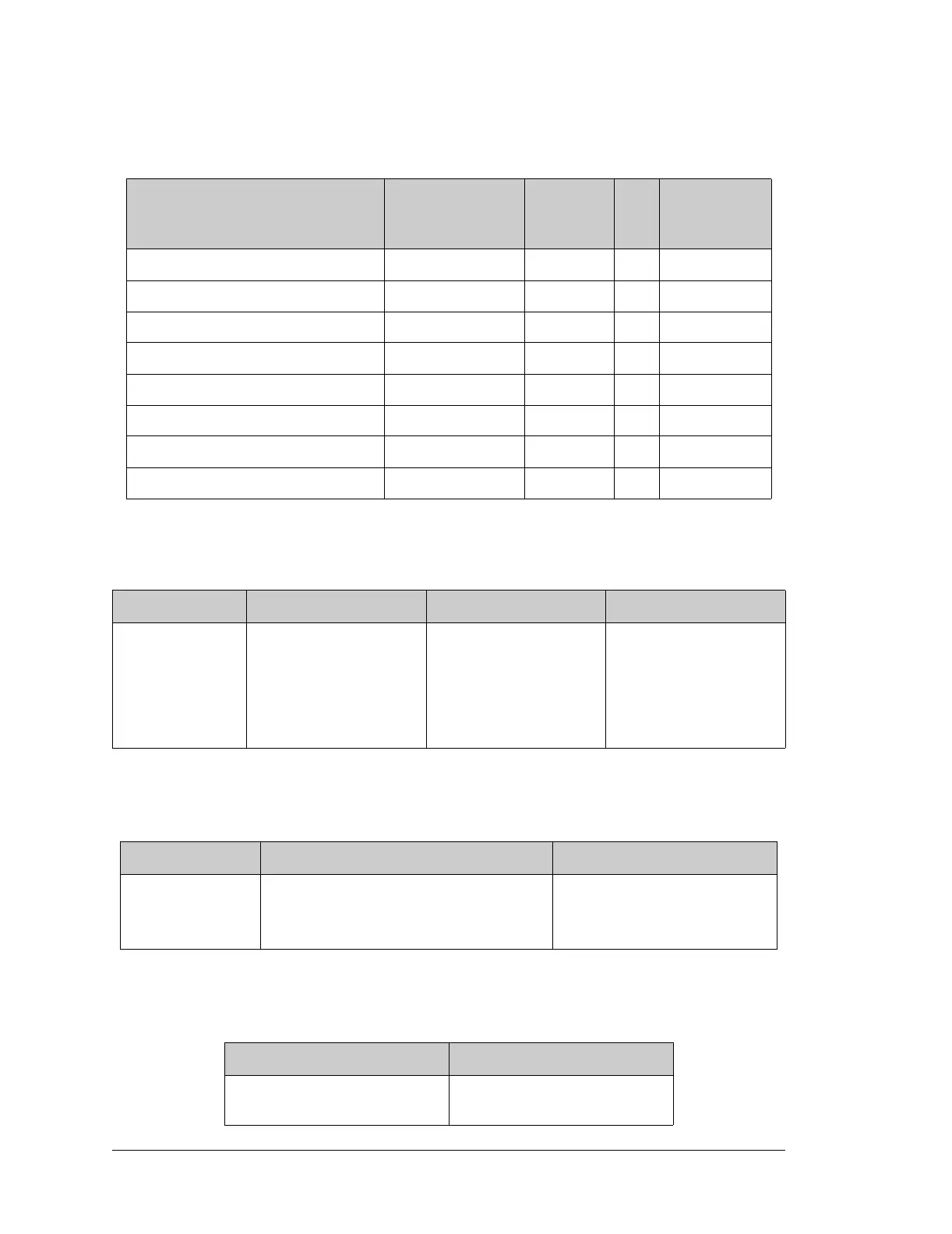

The Timer B I/O registers are listed in Table 11-4.

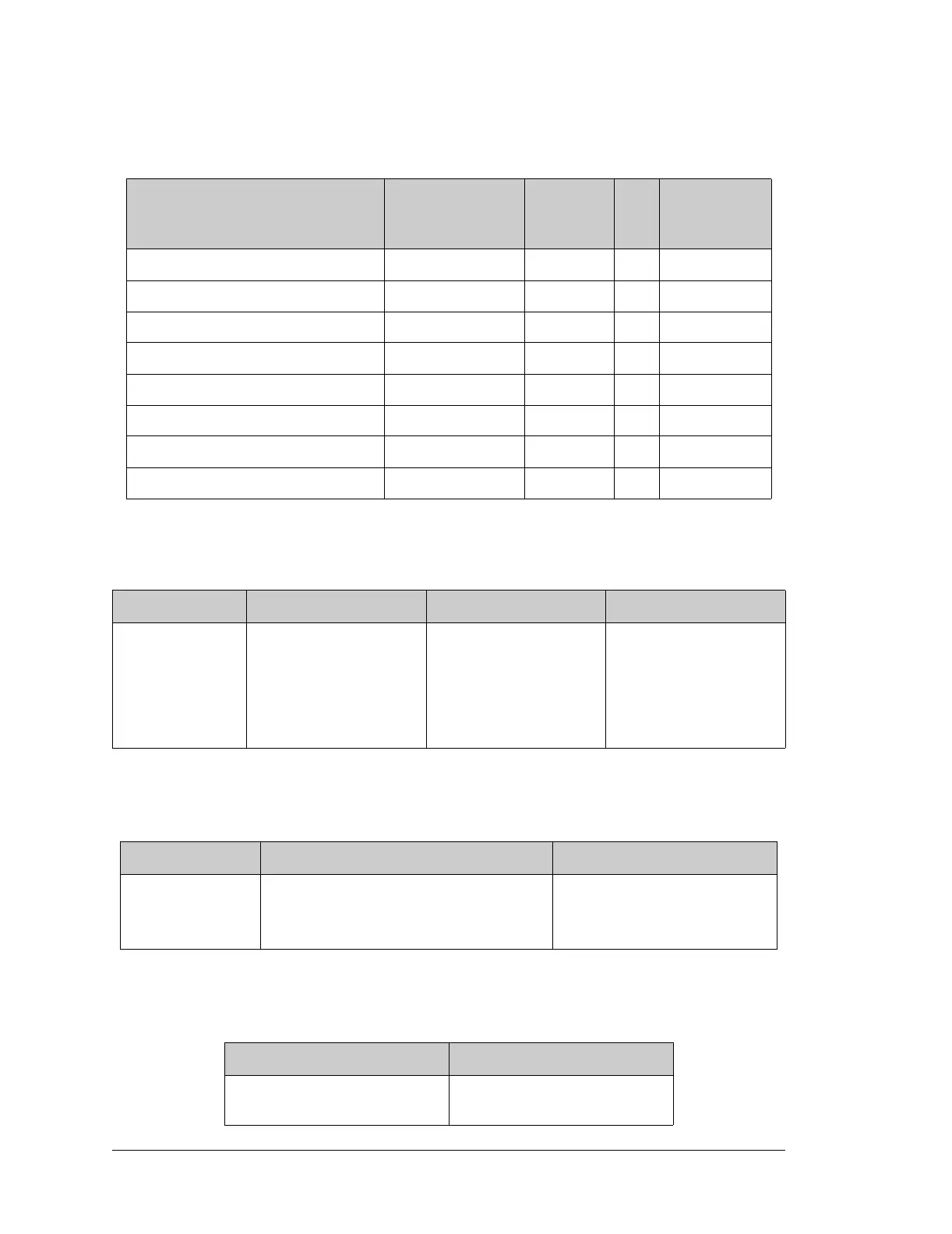

The control/status register for Timer B (TBCSR) is laid out as shown in Table 11-5.

The control register for Timer B (TBCR) is laid out as shown in Table 11-6.

The MSB x registers for Timer B (TBM1R/TBM2R) are laid out as shown in Table 11-7.

Table 11-4. Timer B Registers

Register Name

Register

Mnemonic

I/O

Address

(hex)

R/W

On Reset

To

Timer B Control/Status Register TBCSR B0 R/W xxxxx000

Timer B Control Register TBCR B1 W xxxxxx00

Timer B MSB 1 Reg TBM1R B2 x

Timer B LSB 1 Reg TBL1R B3 W x

Timer B MSB 2 Reg TBM2R B4 W x

Timer B LSB 2 Reg TBL2R B5 W x

Timer B Count MSB Reg TBCMR BE R x

Timer B Count LSB Reg TBCLR BF R x

Table 11-5. Timer B Control and Status Register (TBCSR) (adr = 0x0B0)

Bits 7:3 Bit 2 Bit 1 Bit 0

Not used

1—A match with match

register 2 was detected.

This bit is cleared when

this register is read;

setting this bit to 1 enables

the interrupt.

1—A match with match

register 1 was detected.

This bit is cleared when

this register is read;

setting this bit to 1 enables

the interrupt.

1—Enable the main clock

for this timer.

Table 11-6. Timer B Control Register (TBCR)

Bits 7:4 Bits 3:2 Bits 1:0

Not used

00—Counter clocked by perclk/2

01—Counter clocked by output of timer A1

1x—Timer clocked by perclk/2 divided by 8

00—Interrupt disabled

xx—Interrupt priority xx enabled.

Table 11-7. Timer B MSB x Register (TBM1R/TBM2R = 0x0B2/0x0B4)

Bits 7:6 Bits 5:0

Two most significant bits of timer

match preload register.

Not used.

Loading...

Loading...