User’s Manual 157

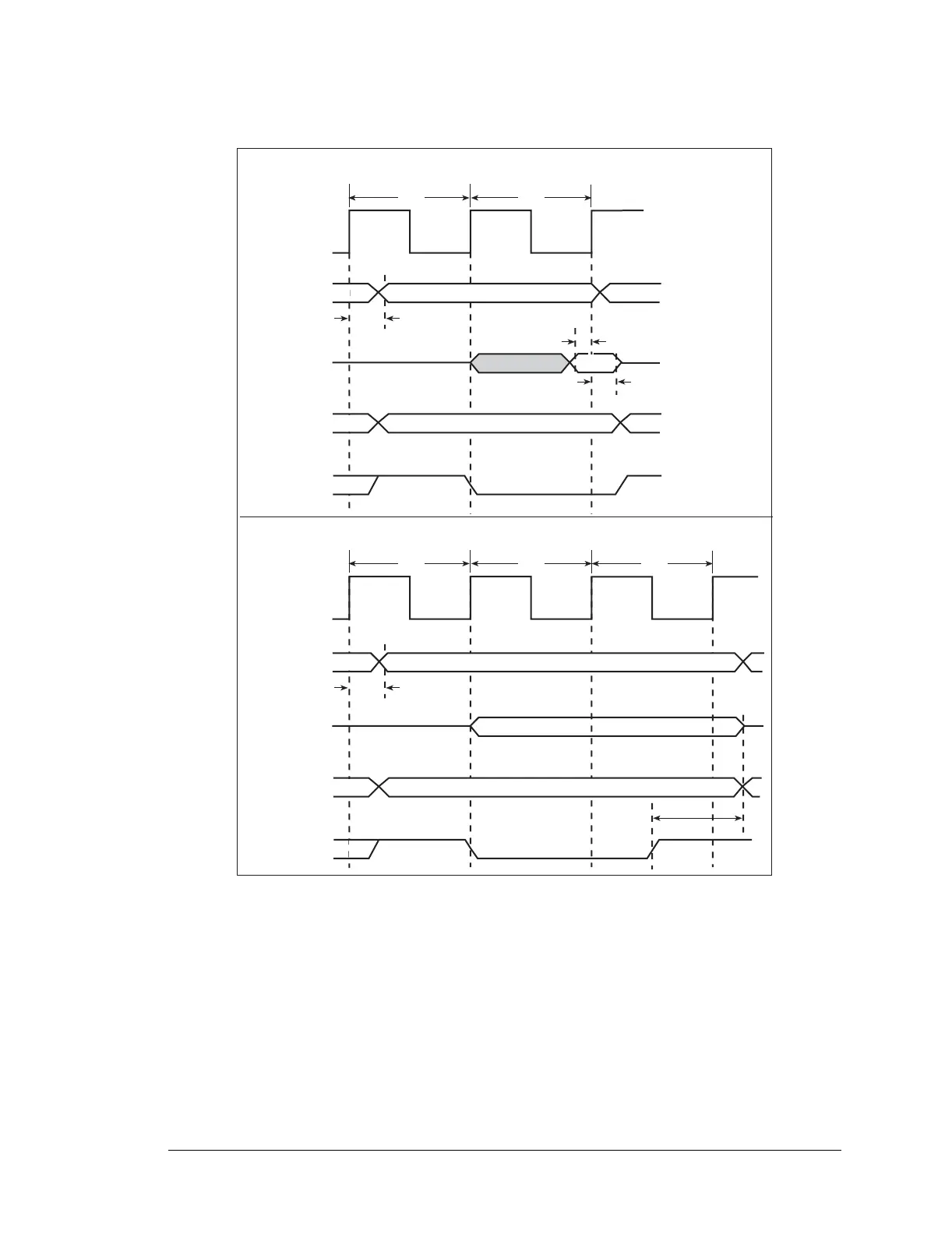

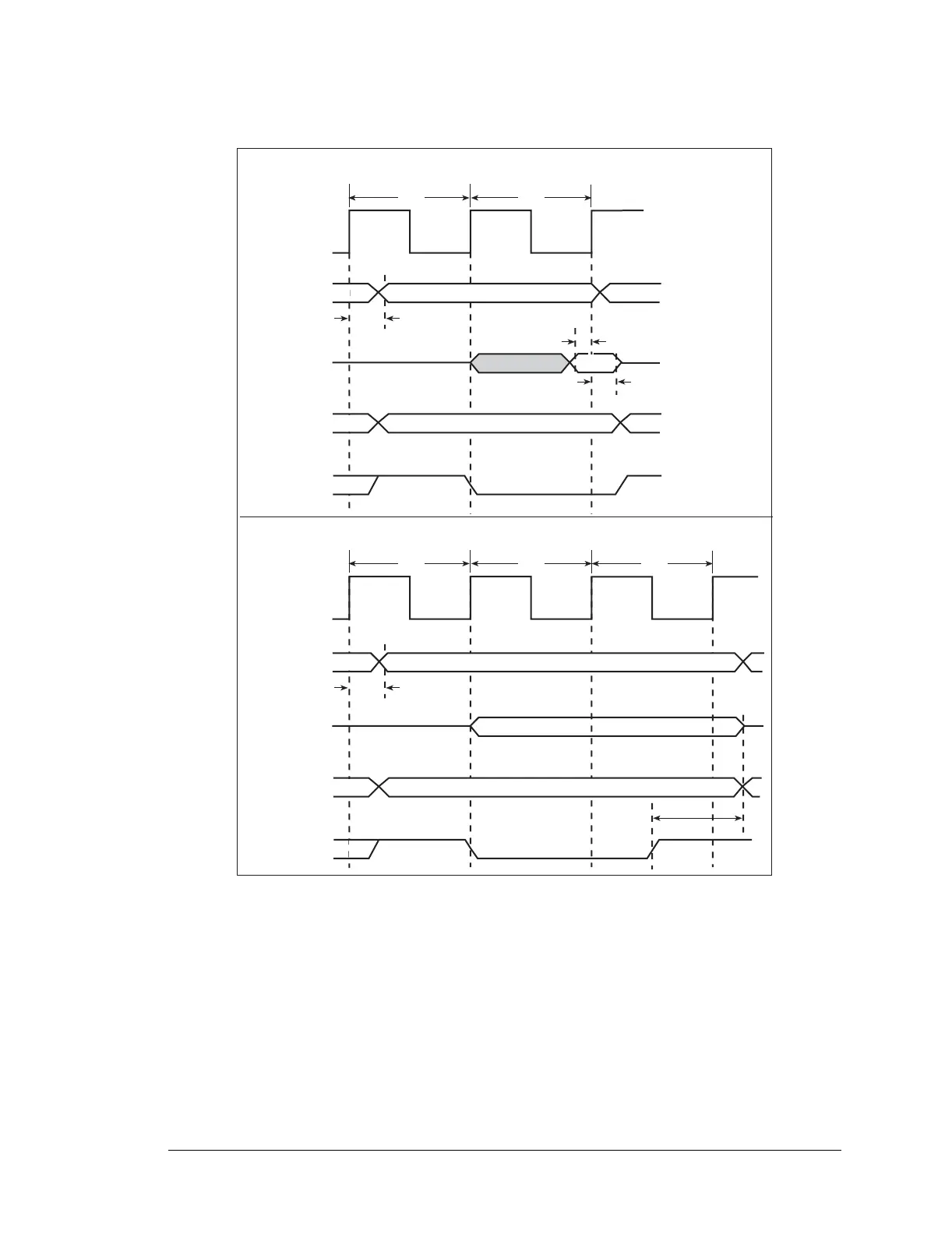

Figure 15-3. Memory Read and Write Cycles

Notice that the data times are different, depending on whether data are being read or writ-

ten. T

hold

for data read specifies how long the data must remain valid following the rising

edge of T1 when the clock cycle repeats. T

DHZV

for data write specifies how long the data

remain valid once /WEx goes high, and must be at least one-half of a CPU clock cycle.

T

adr

T

adr

Memory Read (no wait states)

/WE

T

hold

valid

CLK

A[19:0]

D[7:0]

valid

T

setup

T

hold

Memory Write (no extra wait states)

CLK

A[19:0]

D[7:0]

/CSx

valid

/OEx

/CSx

valid

/WEx

valid

T1

T2

T1

Tw

T2

valid

Loading...

Loading...