User’s Manual 75

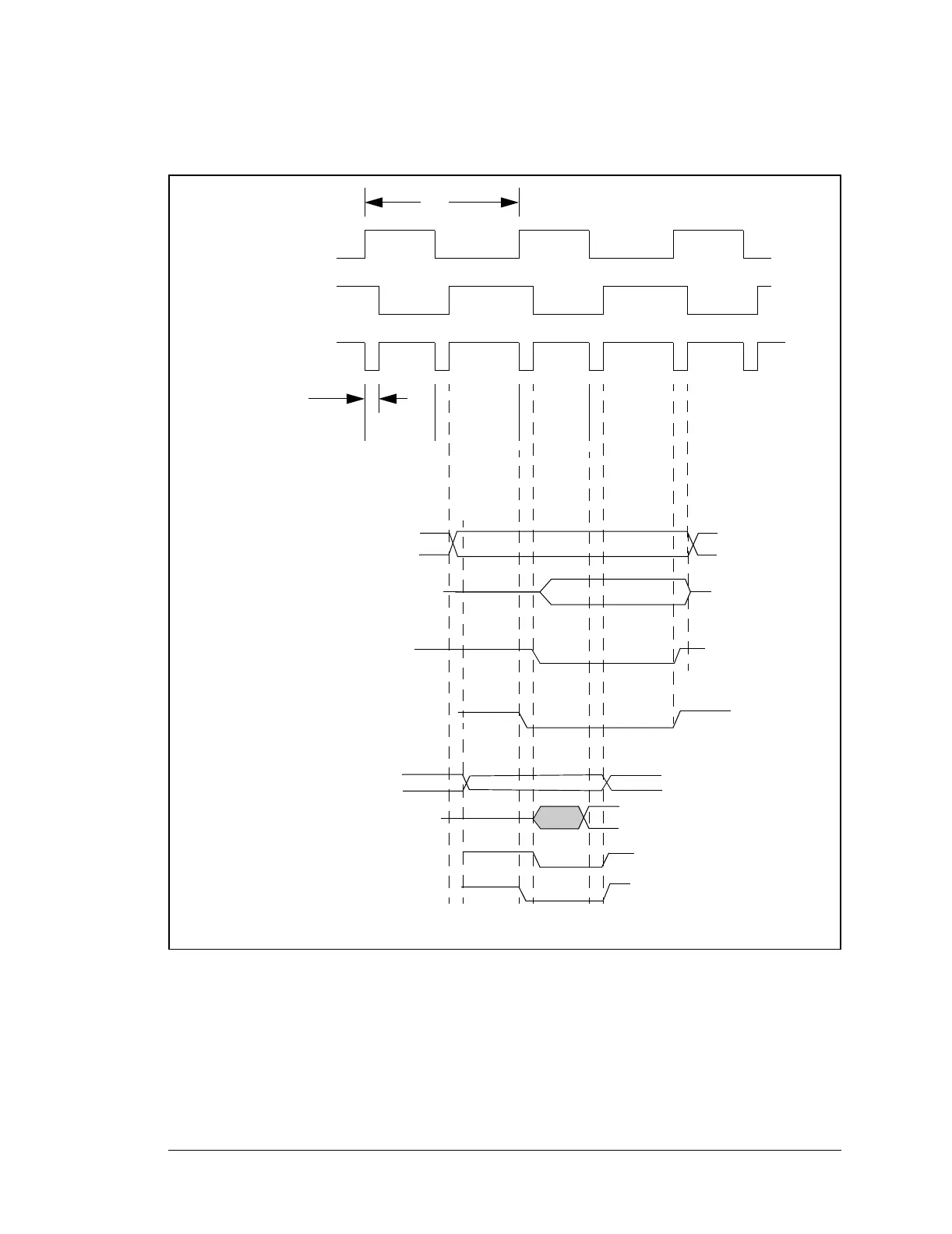

When the clock doubler is used and there is no subsequent division of the clock, the output

clock will be asymmetric, as shown in Figure 7-2.

Figure 7-2. Effect of Clock Doubler

The doubled clock-low time is subject to wide (50%) variation since it depends on process

parameters, temperature, and voltage. The times given above are for a supply voltage of 5 V

and a temperature of 25°C. The doubled clock-low time increases by 20% when the voltage

is reduced to 4 V, and increases by about 40% when the voltage is reduced further to 3.3 V.

The values increase or decrease by 1% for each 5°C increase or decrease in temperature.

Oscillator

Oscillator delayed

and inverted

Doubled clock

Delay

Time

48% 52%

P

0.48P 0.52P 0.48P 0.52P

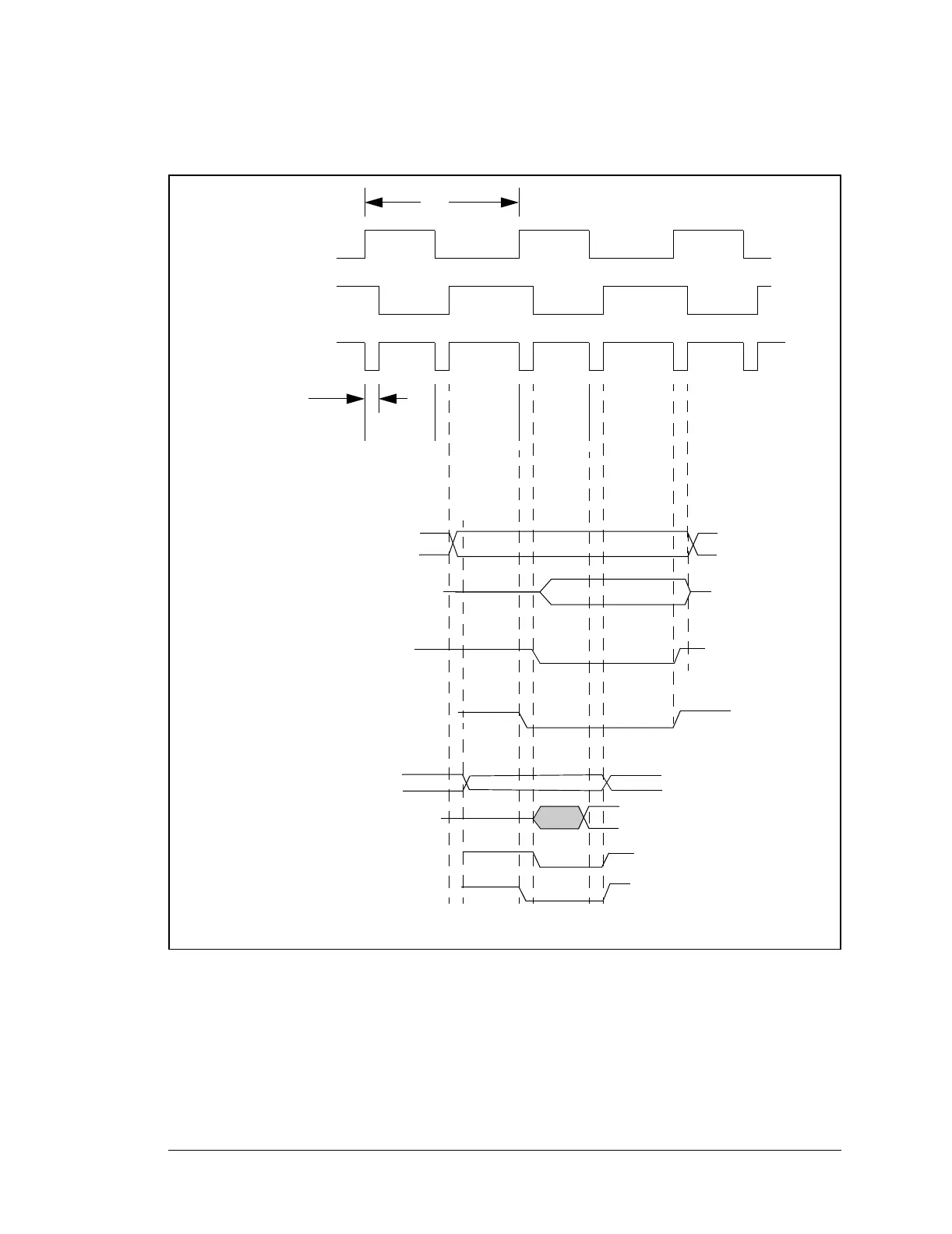

Data out

Example

Write

Cycle

Write pulse

Early write pulse

option

Example

Read

Cycle

Address, /CS

Address, /CS

Output enb

Early output enb

option

Valid data out from mem

Loading...

Loading...