RZ/A2M SUB Board RTK79210XXB00000BE 2. Function specifications

R20UT4398EJ0100 Rev.1.00 2-20

2018.10.11

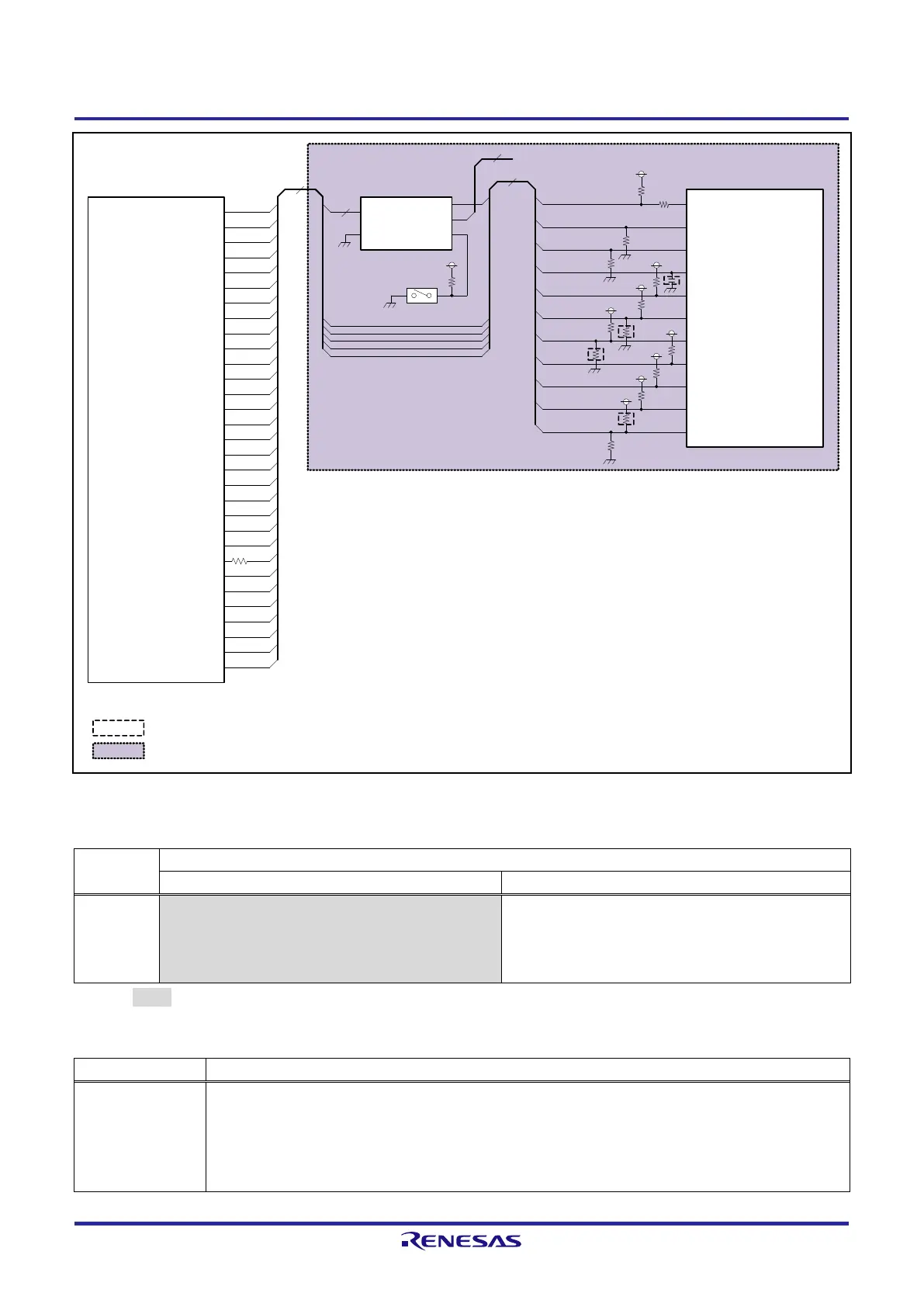

Figure 2.3.1 SDRAM Block Diagram

Table 2.3.2 Function Setting Table of DIP Switch SW6-1 for System Setting

P9_[7 :0] and P8_[7 :1], P2_2, P2_0, P1_3,

P1_[1 :0], P0_[6 :0], P6_7, P6_5, P7_[1 :0], P7[5 :3]

are used as SDRAM control pins.

P9_[7 :0] and P8_[7 :1], P2_2, P2_0, P1_3, P1_[1 :0],

P0_[6 :0], P6_7, P6_5, P7_[1 :0], P7[5 :3] are used

as DRP, audio, UART and/or USB interface pins

(default settings).

[Note] indicates setting functions.

Table 2.3.3 Clock Pulse Oscillator Settings

Clock pulse oscillator settings

■ CKIO selection register (CKIOSEL)

・Initial value: H'0001

・Recommended setting value: H'0000

‐CKIO output clock selection:

CKIOSEL[1:0] = B'00; Bφ clock output

DQML

39

CKIO

A13

A14

D7

3.3V

CS3#

D[15:0]

A[13:1]

A[15:14]

CKIO

DQMU

RD/WR#

CS3#

RAS#

CAS#

A15

D[6:0]

RAS#

CAS#

CKE

DQML

DQMU

RD/WR#

CKE

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

A10

A11

A12

A7

A8

A9

A4

A5

A6

D15

A[3:1]

D12

D13

D14

D11

D8

D9

D10

RZ/A2M (U1)

P1_4 / D11

P1_3 / D10

P1_1 / D8

P1_2 / D9

P1_0 / D7

P2_3 / D15

P2_2 / D14

P2_1 / D13

P2_0 / D12

P8_[3:1] / A[3:1] / DRP[21:23]

P8_4 / A4 / DRP20 / SSL00

P8_5 / A5 / DRP19 / MISO0

P8_6 / A6 / DRP18 / MOSI0

P8_7 / A7 / DRP17 / RSPCK0

P9_0 / A8 / DRP16 / TxD4

P9_1 / A9 / DRP15 / RxD4

P9_2 / A10 / DRP14

P9_3 / A11 / DRP13 / SSIRxD0

P9_4 / A12 / DRP12 / SSITxD0

P9_5 / A13 / DRP11 / SSIFS0

P9_6 / A14 / DRP10 / SSIBCK0

P9_7 / A15 / DRP09

P0_[6:0] / D[6:0] / DRP[30:24]

CKIO

P6_5 / DRP01 / CS3

P6_7 / WE0/DQML / DRP03

P7_0 / WE1/DQMU / DRP04 /

SCK1

P7_1 / RD/WR / DRP05 / RxD1

P7_3 / RAS / DRP06 / TxD1

P7_4 / CAS / DRP07 / RTS1

P7_5 / CKE / DRP08 / CTS1 /

OVRCUR1

SDRAM / Other

OE# S

A

B1

39

34

3.3V

DIP

SW6-1

ON

SDRAM(U30)

WE#

CLK

DQML

CS#

DQMH

D[15:0]

BA[1:0]

A[12:0]

RAS#

CAS#

CKE

D11

D13

D15

D9

CKIO

MUX×9

3.3V

Note: Red text indicates a function used.

:Indicates a function not implemented.

:Indicates a SUB board.

B2

34

To DRP I/F, Audio I/F, UART I/F, USB(ch1)

ON(L):A=B1, OFF(H):A=B2

Loading...

Loading...